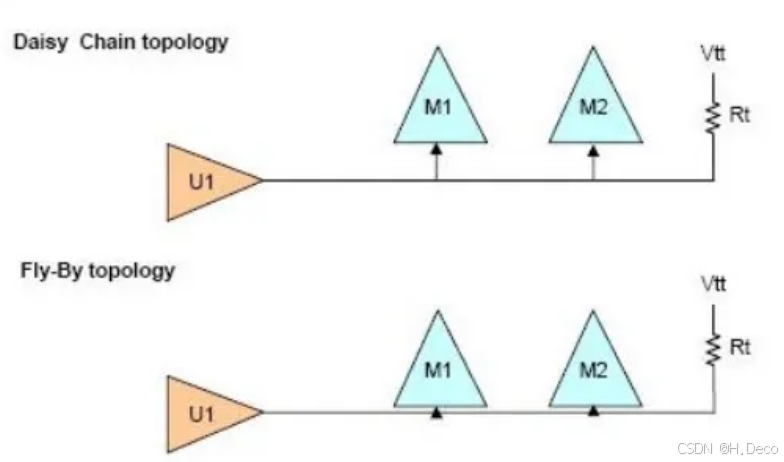

在高速PCB设计领域,信号完整性(Signal Integrity, SI)和电磁兼容性(Electromagnetic Compatibility, EMC)直接影响系统性能。本文将从传输线理论和实际应用角度,深入剖析三种关键的布线拓扑结构:Fly-by、Daisy Chain和T-topology

传输线理论基础

反射与阻抗匹配

在高速信号传输中,当信号遇到阻抗不连续点时会产生反射。反射系数Γ可表示为:

其中ZL为负载阻抗,Z0为特征阻抗。这个基础理论对理解不同拓扑结构的性能至关重要

拓扑结构详细分析

Fly-by拓扑

Fly-by拓扑作为DDR4的标准布线方案,其核心特征在于采用单一主干传输线结构。信号沿着阻抗匹配的主干线传播,通过精心设计的短支路将信号耦合到各个DRAM器件。

关键技术参数:

- 主干线特征阻抗:通常维持在50Ω ±10%

- 支路长度:应控制在最小化范围,典型值<5mm

- 终端匹配网络:采用Thevenin终端,典型值为50Ω到VTT(VDD/2)

传播延迟差:

其中L为信号路径长度,εr为介质相对介电常数,c为光速

Daisy Chain拓扑

Daisy Chain采用串行链式结构,每个节点都作为信号的接收者和驱动者。信号传输可用以下方程描述:

其中Gn为第n级的传输增益。

技术特征:

- 信号重新驱动机制

- 累积性延迟特性

- 节点间的阻抗匹配要求

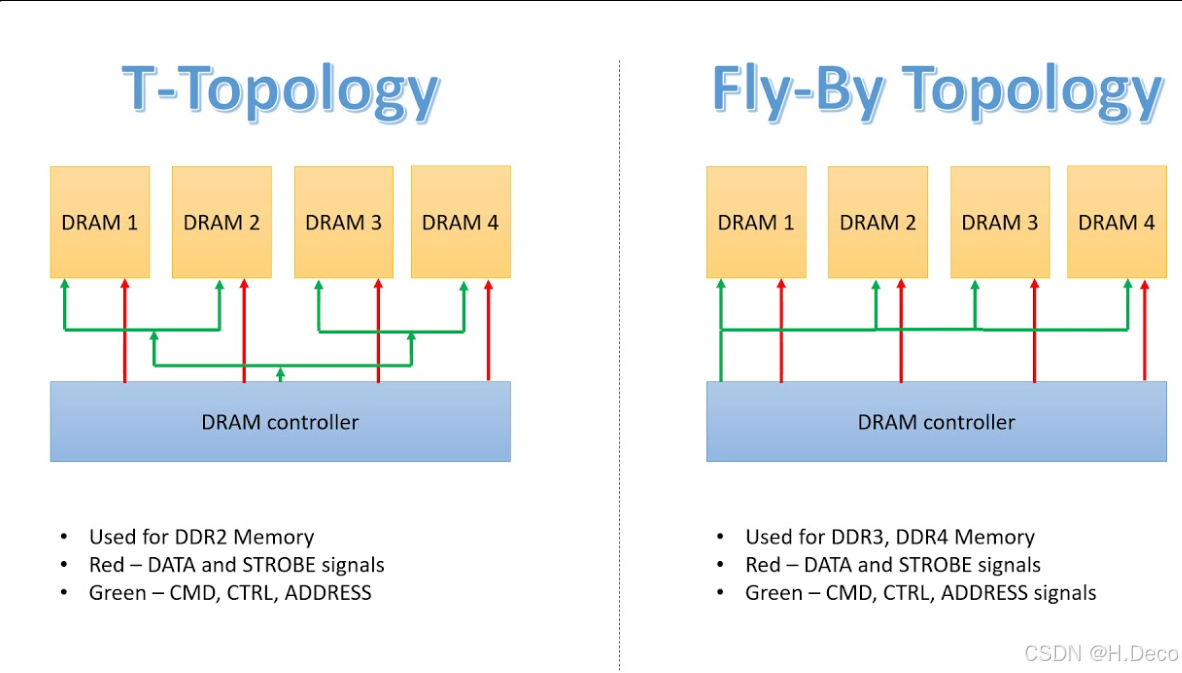

T-topology

T-topology在DDR3时代广泛应用,其特点是采用对称分叉结构。信号传输路径可以用传输线S参数矩阵表示:

分叉点的反射系数:

其中Z1、Z2为分支阻抗,Z0为主干特征阻抗

性能对比分析

信号完整性比较

通过时域反射(TDR)和眼图分析,三种拓扑的性能表现如下:

Fly-by拓扑

- 反射损耗:典型值<-20dB @1GHz

- 串扰抑制:>-30dB

- 信号上升时间保持率:>90%Daisy Chain拓扑

- 信号衰减:随链路长度呈指数衰减

- 带宽限制:由器件间互连决定

- 时序抖动:累积效应明显T-topology

- 分叉点反射:显著影响信号质量

- 带宽限制:通常<1.6Gbps

- 阻抗匹配难度:要求严格的对称性

拓扑结构的基本原理与电学特性

Fly-by 拓扑 (Fly-by Topology)

Fly-by 拓扑已成为高速 DDR4 及后续内存接口中命令、地址和控制信号线的首选标准布线方案。其核心思想是构建一条连续的主传输线,信号沿此主线顺序传播,每个目标器件(如 DRAM 芯片)通过极短的 Stub 分支连接到主线。主传输线的末端通常连接一个特性阻抗匹配的终端电阻

核心电学特性与结构特点:

-

近乎连续的传输线: 主信号线保持阻抗的连续性,最大程度地减少了由于阻抗不连续性引起的信号反射

-

短 Stub 分支: 连接到每个器件的 Stub 分支长度远小于信号的波长,其引入的容性负载和感性负载被限制在较小范围内,对信号完整性的影响可控

-

终端匹配: 终端电阻吸收传输到末端的信号能量,进一步抑制反射,改善信号质量

-

顺序传播与可预测延迟: 信号按照物理顺序依次到达每个器件,引入了固有的传播延迟差异 (Skew),但这种延迟是可预测的,可以通过诸如 Write Leveling 等动态校准机制进行补偿

-

减轻容性负载: 相比于 T 分叉拓扑,Fly-by 结构有效降低了每个信号线上连接的器件所带来的累积容性负载

可以将 Fly-by 拓扑比作一条高速公路,主干道上的车辆(信号)以接近恒定的速度流动,各个出口(DRAM 芯片)如同短匝道,车辆短暂驶入后即离开,不会显著干扰主干道的交通流

菊花链拓扑 (Daisy Chain Topology)

菊花链拓扑是一种纯粹的串行点对点连接结构,信号从源端开始,依次经过每一个器件。前一个器件的输出直接连接到下一个器件的输入

核心电学特性与结构特点:

-

串行阻抗链: 信号路径上,每个器件的输入阻抗和输出阻抗串联起来,形成一个复杂的阻抗网络,难以实现良好的阻抗匹配

-

信号累积效应: 信号在传输过程中可能发生衰减、失真,并且每个器件都可能引入噪声,这些不利影响会随着链的延长而累积

-

延迟累加: 信号的总延迟是每个器件的传输延迟以及互连线延迟的累加,这可能导致严重的时序偏差

-

对驱动能力的要求: 源端需要有足够的驱动能力来克服整个链条上的损耗

-

反射风险增加: 每个连接点都可能存在阻抗不连续,增加信号反射的风险

将菊花链拓扑看为一场接力赛跑,接力棒(信号)需要经过每一位运动员(器件)的手中传递,任何一位运动员的失误都可能影响最终结果

T 分叉拓扑 (T-topology)

T 分叉拓扑在早期的并行总线(如 DDR3)中被广泛采用。其特点是将信号从源端分叉成两条或多条等长的传输线,每条传输线连接到一组目标器件

核心电学特性与结构特点:

-

阻抗分叉与匹配挑战: 在信号分叉点,传输线的阻抗发生变化,理论上需要精确的阻抗匹配网络来避免反射,但在实际应用中很难实现理想匹配

-

Stub 效应显著: 从分叉点到每个器件的连接线形成了 Stub,其长度接近信号波长的四分之一时,会产生严重的阻抗不匹配和信号谐振

-

对等长性的极端依赖: 为了保证信号同步到达,各分支线路的物理长度、介质特性、走线宽度等参数必须严格一致,这在实际 PCB 制造中面临巨大挑战

-

共模噪声敏感: 由于很难保证完全对称,T 分叉拓扑对共模噪声比较敏感

-

同步开关噪声 (SSN) 问题: 多个器件同时开关可能导致严重的电源和地弹噪声

T 分叉拓扑则类似一条河流,在分叉口,水流会分成几支,如果河道宽度、深度不一致,水流速度和流量就会产生差异,难以同步到达下游

| 评估维度 | Fly-by拓扑 | Daisy Chain拓扑 | T-topology |

|---|---|---|---|

| 信号传输路径 | 单一主干线,器件通过短支路连接 | 器件串行连接,点对点传输 | 从源点分叉为两条等长支路 |

| 阻抗匹配特性 | 主干线50Ω,终端匹配简单 | 每段需单独匹配,难度中等 | 分叉点匹配复杂,难度高 |

| 信号延迟特性 | 存在固定传播延迟差(Flight time skew) | 延迟累积,随链路增加 | 理论上同时到达,实际难保证 |

| 信号完整性 | 优秀(反射损耗<-20dB @1GHz) | 中等(信号逐级衰减) | 较差(分叉点反射明显) |

| 最大传输速率 | 高(>3200MT/s) | 中等(取决于链路长度) | 低(通常<1600MT/s) |

| 布线复杂度 | 中等(需控制支路长度) | 简单(点对点连接) | 复杂(严格等长要求) |

| EMI特性 | 良好(辐射源集中) | 中等(分布式辐射) | 较差(分叉点辐射) |

| 扩展性 | 好(易于增加节点) | 有限(受链路长度限制) | 差(受分叉平衡限制) |

| 成本效益 | 中等(需要训练机制) | 低(结构简单) | 高(要求严格的布线控制) |

| 典型应用 | DDR4命令/地址信号 | 低速串行接口 | DDR3双通道配置 |

| 关键设计考量 | - Write leveling补偿 |

可以看出Fly-by拓扑在高速信号传输中具有显著优势。其在信号完整性、实现复杂度和成本效益等方面的平衡,使其成为DDR4的最佳选择

1758

1758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?