走线的拓扑结构是指一根走线的布线顺序及布线结构,在实际电路中常常会遇到单一驱动源驱动多个负载的情况,驱动源和负载构成了信号的拓扑,不同的拓扑分布对信号的影响是非常显著的。常用的PCB走线拓扑结构有Daisy Chain、Fly-by、Star、Far-end cluster、Tree几种结构。本篇将介绍这些常用拓扑结构在不同匹配模式下的负载瞬态特性的研究。

Daisy Chain结构

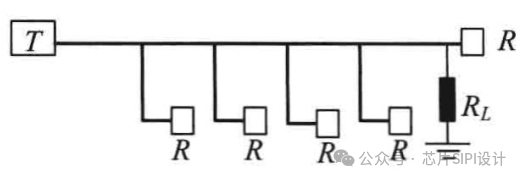

菊花链结构(Daisy Chain)比较简单,是从发射端出发依次到达各接收端进行布线,阻抗比较容易控制,如下图所示,连接每个接收端的短桩线stub需要较短,因为stub表现为一个容性负载,会将信号的上升时间降低,在优化的时候,经常在终端加一个匹配,位于所有的分支接收端之外。Daisy Chain布线结构由于不同步,所以限制了走线长度,同时由于stub电容的效应,所以适合较低速传输情况。

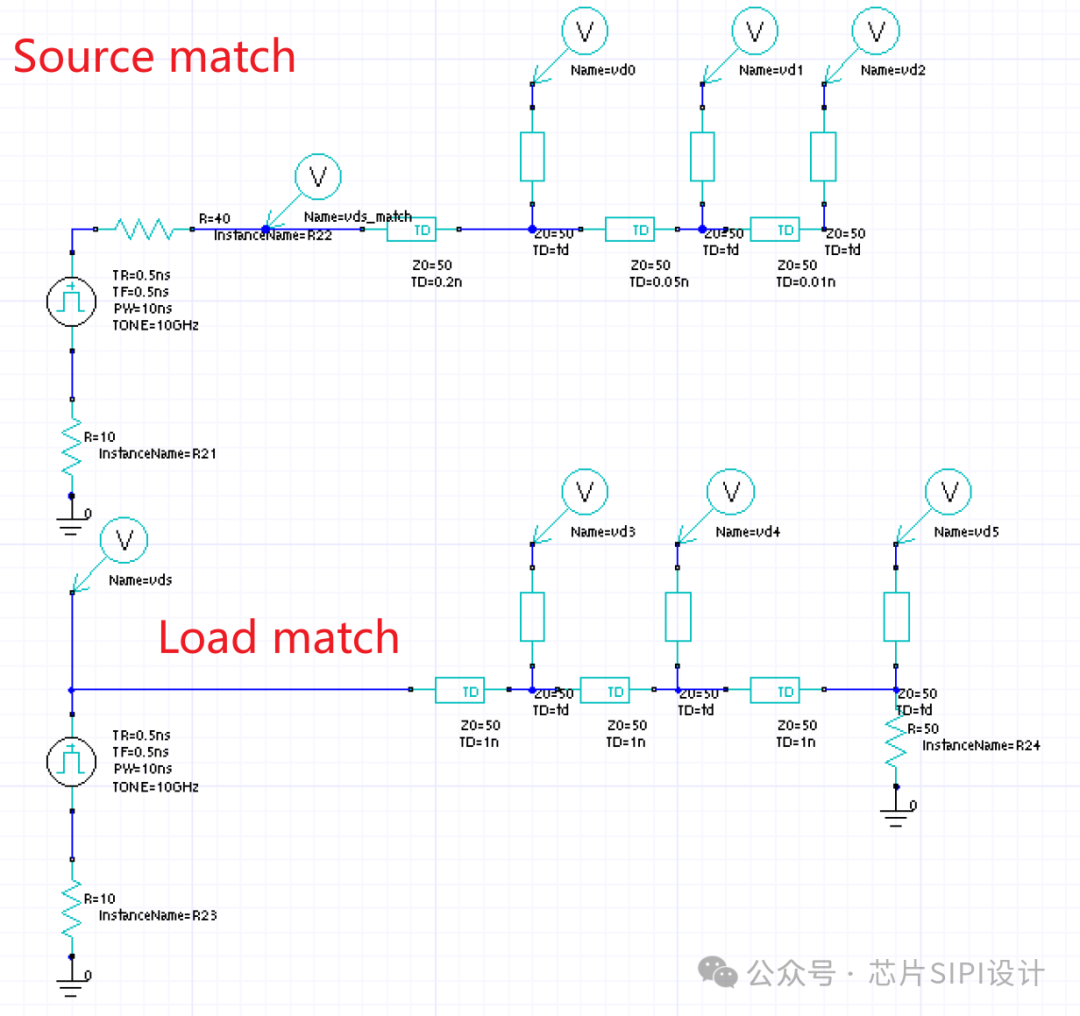

接下来分析源端匹配或负载端匹配下,菊花链拓扑结构信号的瞬态特性,如下是仿真链路图。

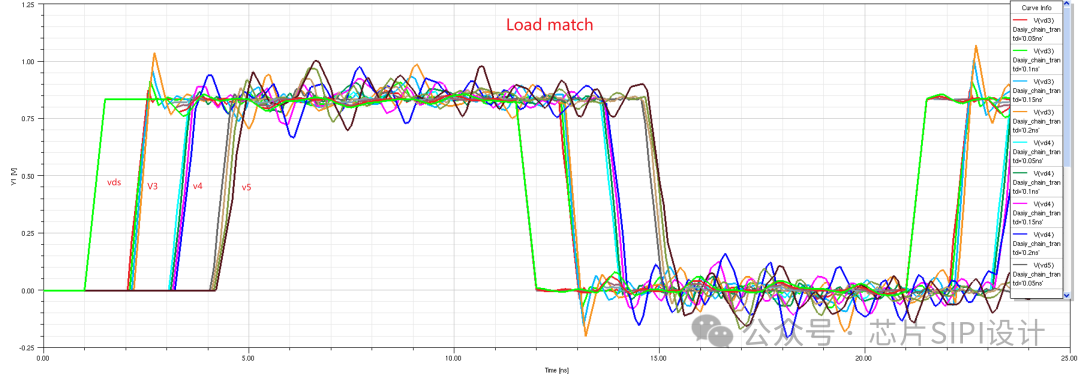

如下瞬态波形为负载端匹配时,各个距离源端1ns/2ns/3ns的负载端及源端对应的舒耐波形图,可以看到负载端幅值波动不是很大,区别仅在于延迟的不同。

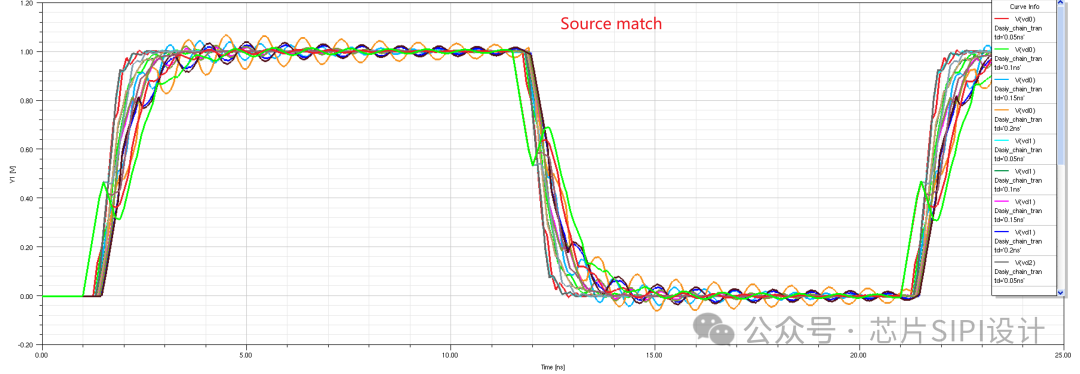

如下图为源端匹配时,对应的不同stub长度的瞬态波形,可以看到,随着stub长度增加,信号恶化也逐渐增大,同时随着离源端的距离增大负载波形恶化也加大。

从上面的仿真可以看到,反射噪声电压的幅度取决于stub传输延时于信号上升沿的相对关系,当stub延时td≤10%的信号边沿TR时,反射噪声电压摆幅可以控制在信号幅度的10%左右,其中负载端并联匹配的相对噪声幅度小于源端串联匹配的情况;同时,由于各个负载存在延迟差,所以限制了走线长度,同时负载电容存在也降低了信号速度。

Fly-By结构

Fly-by结构是一种特殊的菊花链结构,理想情况下stub线为0,这样的信号质量比较好,如下图所示为DDR4常用的Fly-by系统拓扑结构,这种拓扑结构延续了菊花链的缺点,即各个接收端均存在延迟。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1512

1512

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?