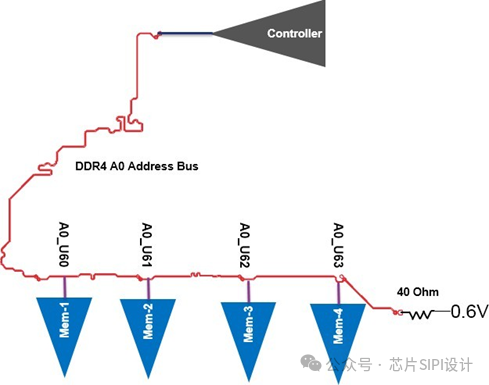

DDR4地址总线的信号完整性和电源完整性分析对于数据可靠性和鲁棒性是必要的。DDR4具有3.2Gbps数据速率的单端信号。在如此高的数据速率下,各种操作之间的timing减少,信号完整性效应的幅度增加。在DDR4中,涉及的两大类总线是数据和地址、控制和命令总线。其中地址、控制和命令总线包括差分时钟和地址、命令和控制信号,差分时钟的工作频率为1.6GHz。这些信号从控制器IC连接到每个存储器模块。下面我们以DDR4 Fly-by拓扑结构(如下图)的应用来评估SIPI性能,这样地址总线是从控制器IC到存储器模块的多点单向连接。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?