在电子系统设计中,"low-power interface"(低功耗接口)是指专为减少能耗而设计的硬件接口。这类接口在不需要牺牲性能的情况下,通过各种技术降低功耗,对于移动设备、嵌入式系统和其他电池供电的应用来说尤其重要。

低功耗接口的关键特性可能包括:

-

电源管理:接口可能包括用于动态调整电源供应的信号,以匹配当前操作的能耗需求。

-

时钟门控:这是一种技术,允许系统在不需要时关闭时钟信号,以减少不必要的时钟能耗。

-

电源门控:在不需要时,可以切断或降低特定电路或模块的电源供应。

-

低功耗模式:接口可能支持一种或多种低功耗模式,如睡眠或待机模式,以在系统不活跃时减少能耗。

-

高效数据传输:设计用于最小化传输数据所需的能量,例如通过减少信号跳变或使用高效的编码技术。

-

自适应工作频率:接口可以根据当前的工作负载动态调整工作频率,以避免过度消耗能量。

-

短突发传输:优化数据传输以使用短突发,从而减少在空闲状态中的能量消耗。

-

信号完整性:即使在低电压下,也要确保信号的完整性和可靠性,以维持数据传输的准确性。

1. 关于低功耗接口

低功耗接口是AXI协议的一个可选扩展,它针对两类不同的外设:

- 任何没有电源关闭序列的外设,且能够指示何时可以关闭其时钟。

- 任何需要电源关闭序列的外设,且只有在进入低功耗状态后才能关闭其时钟。该外设需要从系统时钟控制器接收一个指示,以了解何时启动电源关闭序列,然后必须在其进入低功耗状态时发出信号

2. 低功耗时钟控制

低功耗时钟控制接口由以下信号组成:

- 来自外设的信号,指示何时可以启用或禁用其时钟。

- 两个握手信号,用于系统时钟控制器请求退出或进入低功耗状态。

2.1 外设时钟需求

CACTIVE信号指示外设是否需要时钟信号。外设在需要时钟被启用时将CACTIVE置为高电平,系统时钟控制器必须立即启用时钟。 外设将CACTIVE置为低电平,以指示它不需要时钟,系统时钟控制器随后可以禁用时钟,但不是必须这样做。 可以在外设需要时随时启用或禁用其时钟的情况下,可以将CACTIVE驱动为永久低电平。必须始终启用其时钟的外设,必须将CACTIVE永久驱动为高电平。 CACTIVE是一些没有电源关闭或电源启动序列的外设所需的唯一时钟控制信号。

2.2 电源关闭或电源启动握手

对于具有电源关闭或电源启动序列的外设,只有在系统时钟控制器的请求下才会进入低功耗状态。AXI协议提供了请求/确认握手信号以支持此请求:

-

CSYSREQ:系统时钟控制器使用CSYSREQ信号请求:

- 外设进入低功耗状态,系统时钟控制器将CSYSREQ信号置为低电平以启动请求。

- 外设退出低功耗状态,系统时钟控制器将CSYSREQ信号置为高电平以启动请求。

-

CSYSACK:外使用CSYSACK信号确认:

- 进入低功耗状态的请求,当它识别到此请求时,将CSYSACK置为低电平。

- 退出低功耗状态的请求。当它识别到此请求时,将CSYSACK置为高电平。

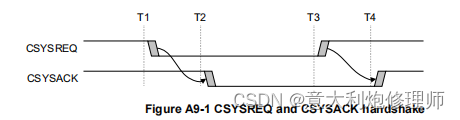

图A9-1显示了CSYSREQ和CSYSACK之间的关系。

在图A9-1所示序列的开始时,CSYSREQ和CSYSACK均为高电平,以进行正常的时钟操作。在时间T1,系统时钟控制器将CSYSREQ置为低电平,表示请求外设进入低功耗状态。外设在时间T2通过将CSYSACK置为低电平来确认请求。在T3,系统时钟控制器将CSYSREQ置为高电平,要求退出低功耗状态。在T4,外设将CSYSACK置为高电平以确认退出。

AXI协议要求CSYSREQ和CSYSACK之间有这种关系。

外设可以接受或拒绝系统时钟控制器提出的进入低功耗状态的请求。当外设通过将CSYSACK置为低电平来确认请求时,CACTIVE信号的电平表示接受或拒绝该请求。

2.3 接受低功耗请求

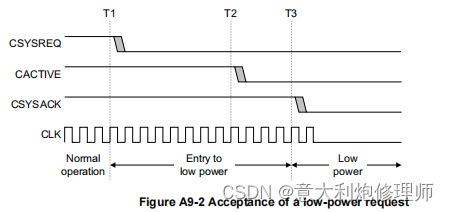

图A9-2显示了外设接受系统低功耗请求的事件序列。

- T1:系统时钟控制器将CSYSREQ置为低电平,请求外设进入低功耗状态。

- T2:外设识别到请求后,执行其电源关闭序列,并在T2将CACTIVE置为低电平,信号表明可以移除时钟。

- T3:外设将CSYSACK置为低电平,信号表明它已完成进入低功耗状态。外设在将CACTIVE置为低电平后,至少一个周期内不能将CSYSACK置为低电平。

2.4 拒绝低功耗请求

图A9-3显示了外设拒绝系统低功耗请求的事件序列。

- T1:系统时钟控制器将CSYSREQ置为低电平,请求外设进入低功耗状态。

- T2:外设通过将CSYSACK置为低电平来确认低功耗请求,但通过保持CACTIVE为高电平来拒绝请求。

- T3:系统时钟控制器通过将CSYSREQ置为高电平,开始低功耗状态退出序列。

- T4:外设通过将CSYSACK置为高电平,完成退出序列。

系统时钟控制器必须维持时钟,并在可以发起另一个低功耗请求之前,必须完成低功耗状态退出序列。

2.5 退出低功耗状态

系统时钟控制器或外设都可以请求从低功耗状态退出。协议要求在低功耗状态下,CACTIVE和CSYSREQ都是低电平,将这两个信号中的任何一个置为高电平都会启动退出序列。

2.5.1 系统时钟控制器发起的退出

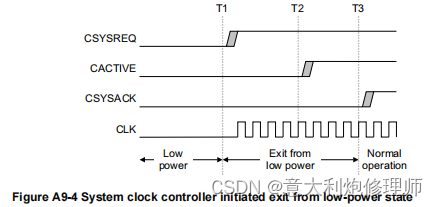

图A9-4显示了系统时钟控制器发起从低功耗状态退出的过程。

- T1:系统时钟控制器将CSYSREQ置为高电平,请求退出低功耗状态,然后启用时钟。

- T2:外设识别到CSYSREQ为高电平,执行其电源启动序列,并将CACTIVE置为高电平,以指示它需要时钟信号。

- T3:外设在T3完成退出序列,通过将CSYSACK置为高电平。

2.5.2 外设发起的退出

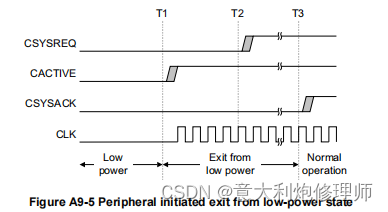

图A9-5显示了由外设发起的从低功耗状态退出的信号过程。

- T1:外设将CACTIVE置为高电平,以信号表明它需要时钟信号,系统时钟控制器随后必须恢复时钟。

- T2:系统时钟控制器将CSYSREQ置为高电平,以继续握手序列。

- T3:外设完成从低功耗状态的退出,并将CSYSACK置为高电平以完成退出序列。

2.6 时钟控制序列总结

图A9-6显示了请求进入低功耗状态的典型流程。

图A9-7显示了请求退出低功耗状态的典型流程。

2.7 将外设组合在低功耗时钟域中

系统时钟控制器可以将多个不同的外设组合到同一个低功耗时钟域中。如果遵守以下规则,它可以像对待单个外设一样对待该时钟域:

-

时钟域的CACTIVE信号是该时钟域中所有外设的CACTIVE信号的逻辑或(OR)。这意味着只有当所有外设都指示它们可以被禁用时,系统时钟控制器才能禁用时钟。

-

系统时钟控制器必须使用一个单一的CSYSREQ信号,该信号被路由到时钟域中的所有外设。

-

时钟域的CSYSACK信号是这样生成的:

- CSYSACK的下降沿发生在该时钟域中最后一个驱动CSYSACK为低电平的外设的CSYSACK信号的下降沿。

- CSYSACK的上升沿发生在该时钟域中最后一个驱动CSYSACK为高电平的外设的CSYSACK信号的上升沿。

1304

1304

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?