XILINX FPGA DDR3 verilog代码,将DDR3配置成一个大型FIFO,使用简单方便,可用于大数据量的

缓存,直接联系默认为DDR3。

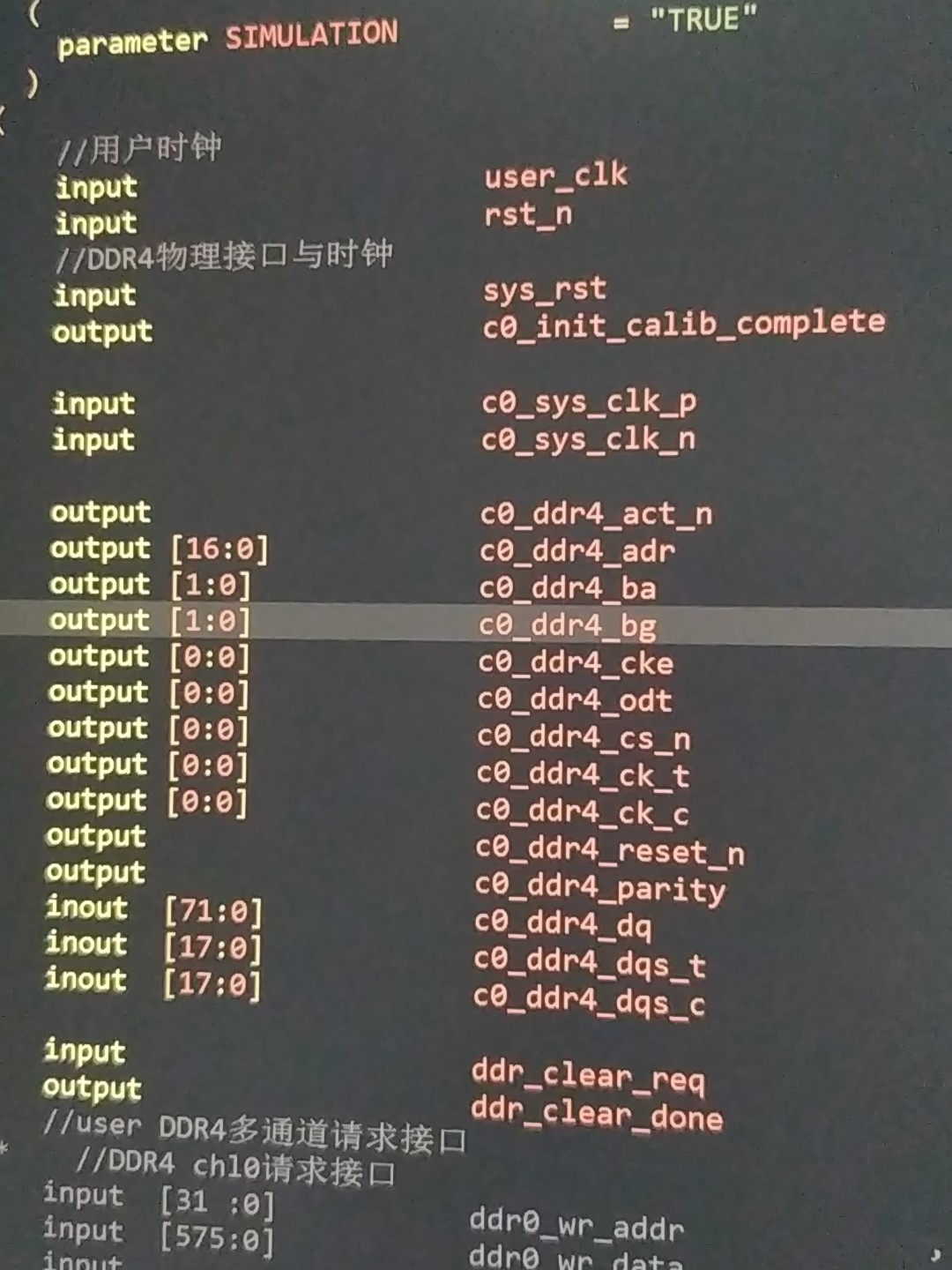

同时也有8通道的DDR4驱动(需单沟通):Xilinx DDR4多通道读写防冲突设计,可实现8个通道同时读写DDR且不冲突问题,每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求,有设计说明文档

ID:52100673834971358

FPGA_2049

标题:XILINX FPGA在大数据处理中的高效DDR3和DDR4驱动设计

摘要:

本文主要介绍了在XILINX FPGA中利用Verilog代码将DDR3配置成大型FIFO的方法,并探讨了其在大数据量缓存中的应用。同时,还详细阐述了Xilinx DDR4多通道读写防冲突设计,可以实现8个通道同时读写DDR且不发生冲突的机制,设计说明文档已给出。

-

引言

随着大数据时代的到来,对于高性能存储和处理的需求越来越迫切。而FPGA作为一种可编程的硬件平台,具备较高的并行性和可重构性,因此成为大数据处理中的重要工具。本文旨在通过使用XILINX FPGA和DDR3、DDR4内存,实现高效的数据存储和处理。 -

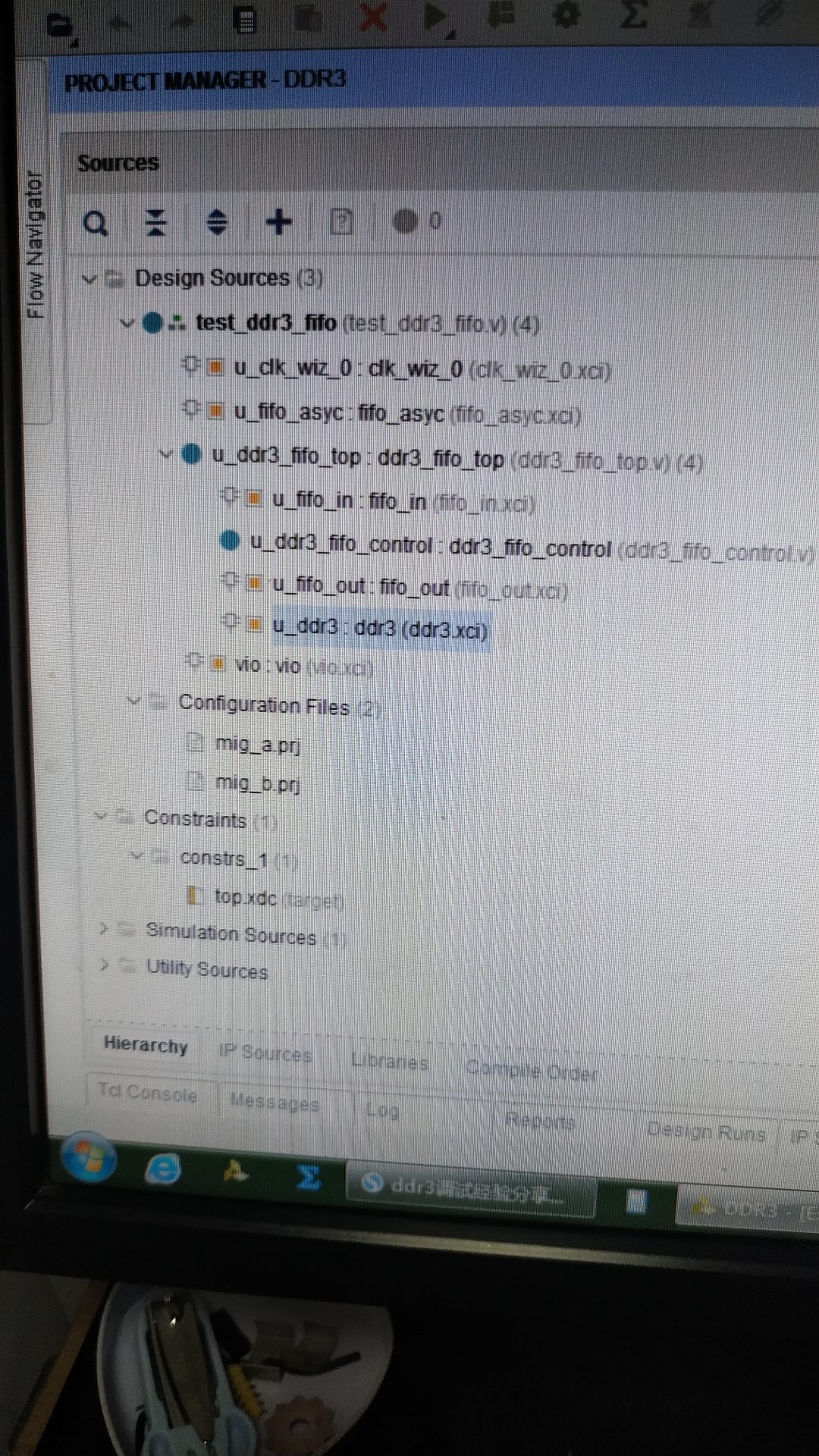

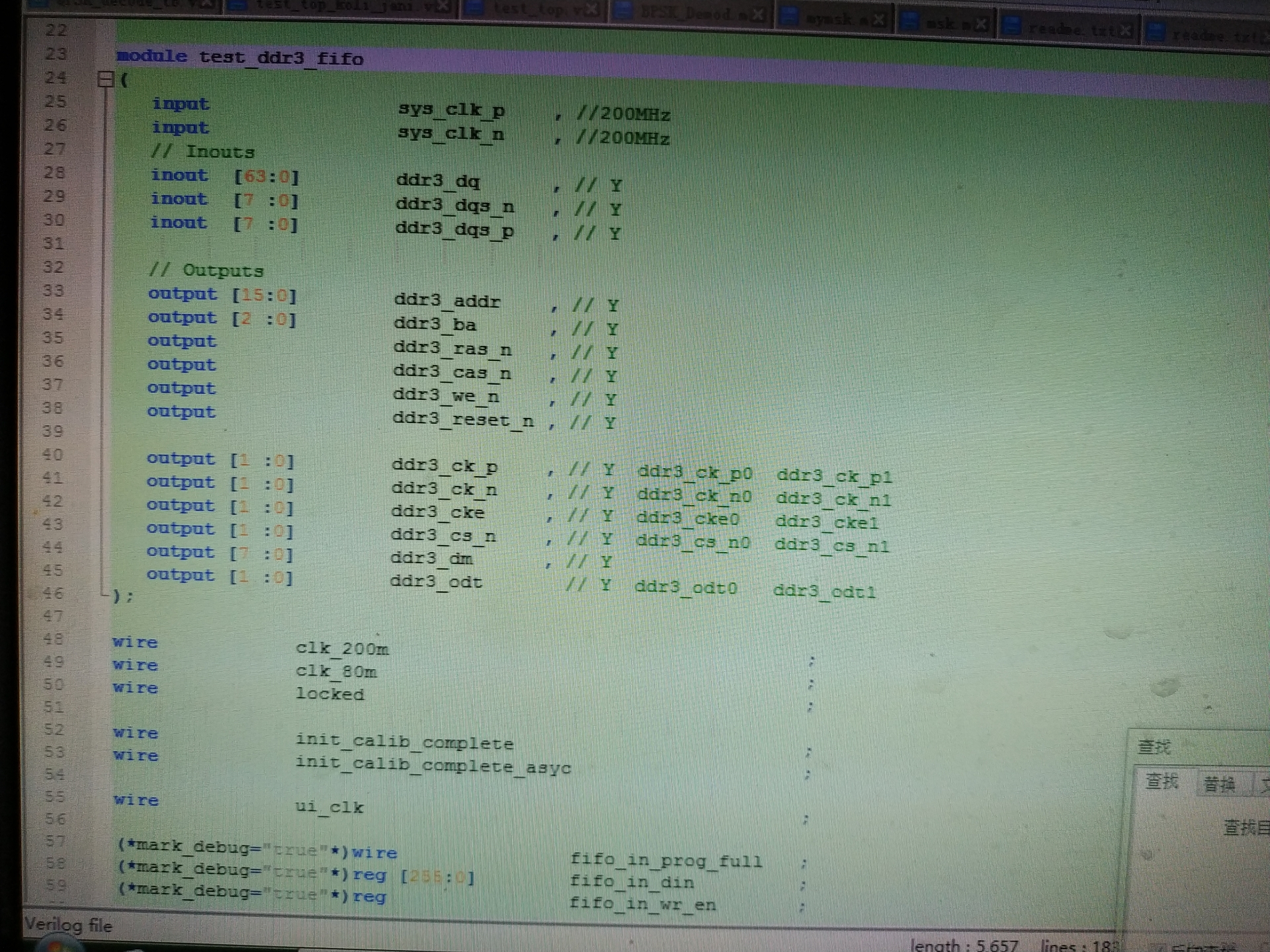

XILINX FPGA中的DDR3配置成大型FIFO

通过使用Verilog代码,我们可以将DDR3内存配置成一个大型FIFO,以满足大数据量的存储需求。这种配置方式使得数据的读写操作变得简单方便,同时具备较高的传输速率和稳定性。详细的配置步骤和代码实现可以参考Xilinx提供的文档。 -

大数据量缓存的应用

配置成大型FIFO的DDR3内存可以作为大数据量缓存的一种解决方案。在大数据处理中,数据的传输速度对于整体系统性能至关重要。DDR3内存的高带宽和低延迟特性,使其成为存储和传输大量数据的理想选择。通过合理设计和管理FIFO,可以实现高效的数据读写和存储。 -

Xilinx DDR4多通道读写防冲突设计

除了DDR3内存外,Xilinx FPGA还支持DDR4内存,并且提供了多通道读写防冲突设计方案。该设计可实现8个通道同时读写DDR4内存而不会发生冲突的机制。每个通道的读写接口简单易懂,并且可以独立操作,实现高效的读写请求。详细的设计说明文档已由Xilinx提供,供开发者参考和使用。 -

结论

本文介绍了XILINX FPGA中配置DDR3为大型FIFO的方法,并讨论了其在大数据量缓存中的应用。同时,还详细阐述了Xilinx DDR4多通道读写防冲突设计,可实现8个通道同时读写DDR且不发生冲突的机制。这些技术在大数据处理中具有重要的意义,为系统设计带来了高性能和高效率的解决方案。

关键词:XILINX FPGA、DDR3、DDR4、Verilog代码、大数据缓存、读写防冲突设计、高性能存储和处理

以上相关代码,程序地址:http://matup.cn/673834971358.html

895

895

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?