XILINX FPGA DDR3 verilog代码,将DDR3配置成一个大型FIFO,使用简单方便,可用于大数据量的

缓存,直接联系默认为DDR3。

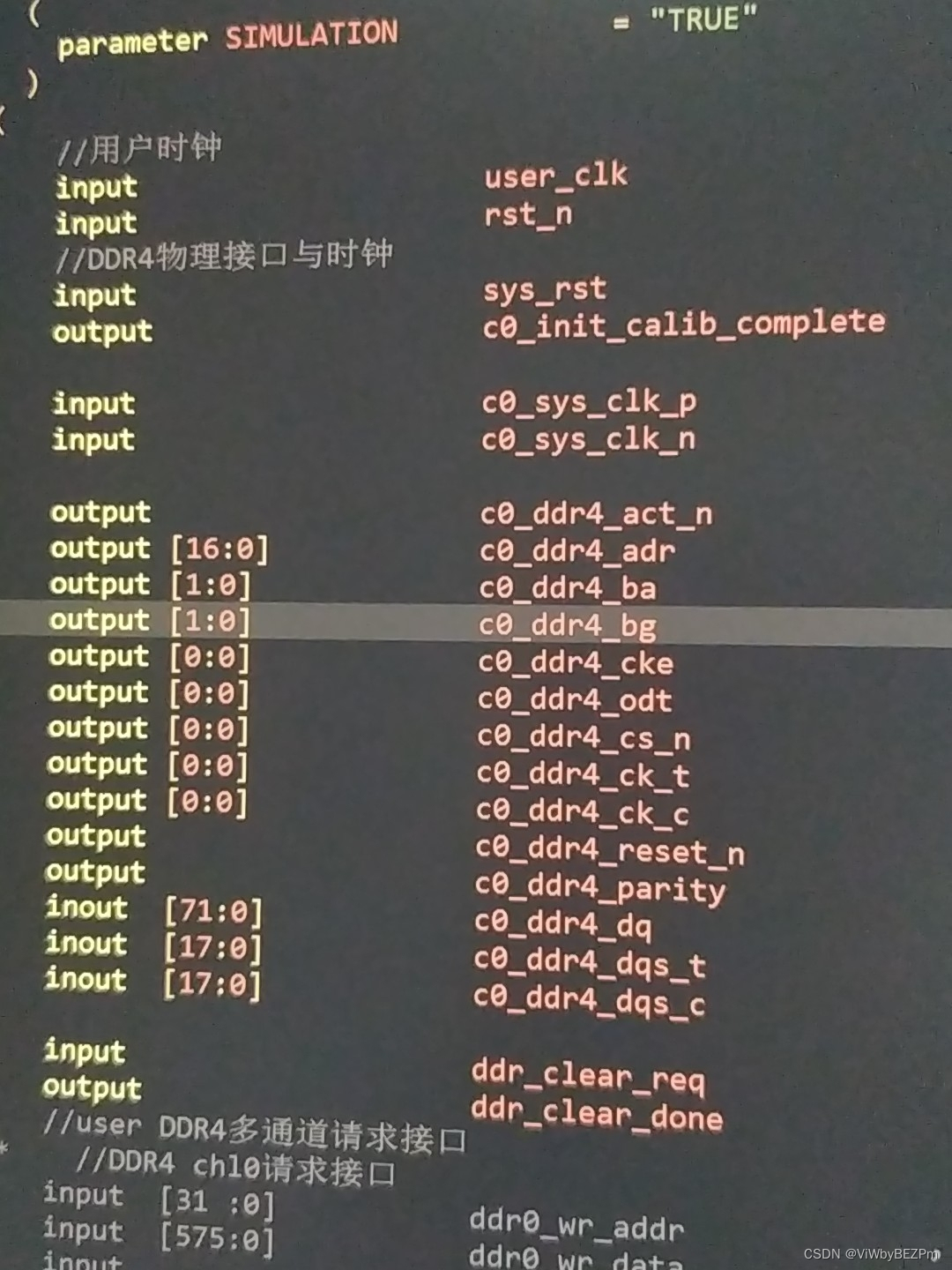

同时也有8通道的DDR4驱动(需单沟通):Xilinx DDR4多通道读写防冲突设计,可实现8个通道同时读写DDR且不冲突问题,每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求,有设计说明文档

随着人们对数据处理速度和容量的需求越来越高,FPGA(现场可编程门阵列)技术成为了数据加速和处理的首选。DDR3和DDR4是目前最流行的内存架构,因此将DDR3和DDR4与FPGA相结合,可以创建一个高性能的数据处理系统,用于大数据量的缓存和处理。本文将介绍如何使用Xilinx FPGA进行DDR3数据缓存,并详细讲解如何将DDR4配置为多通道读写防冲突设计。

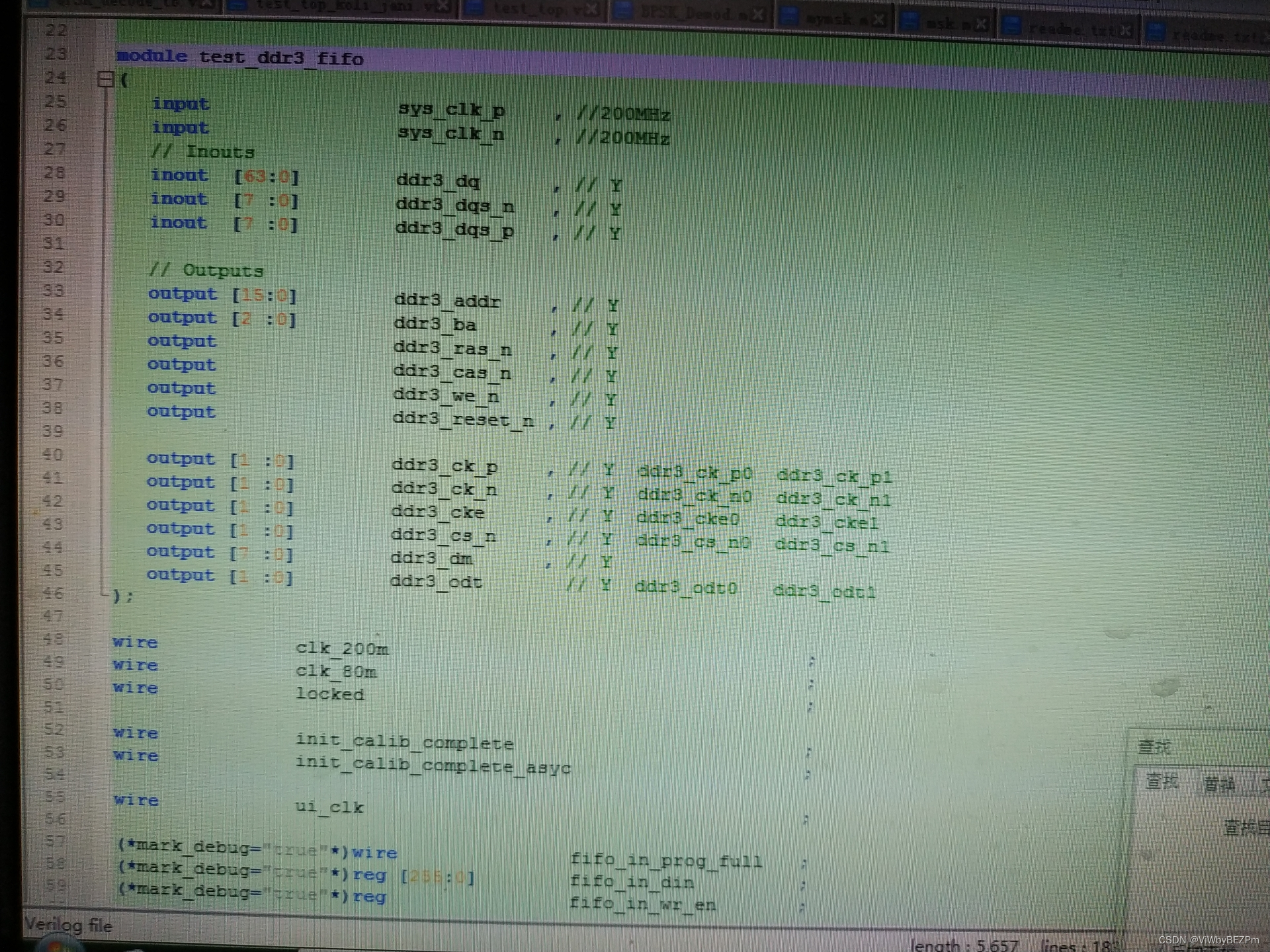

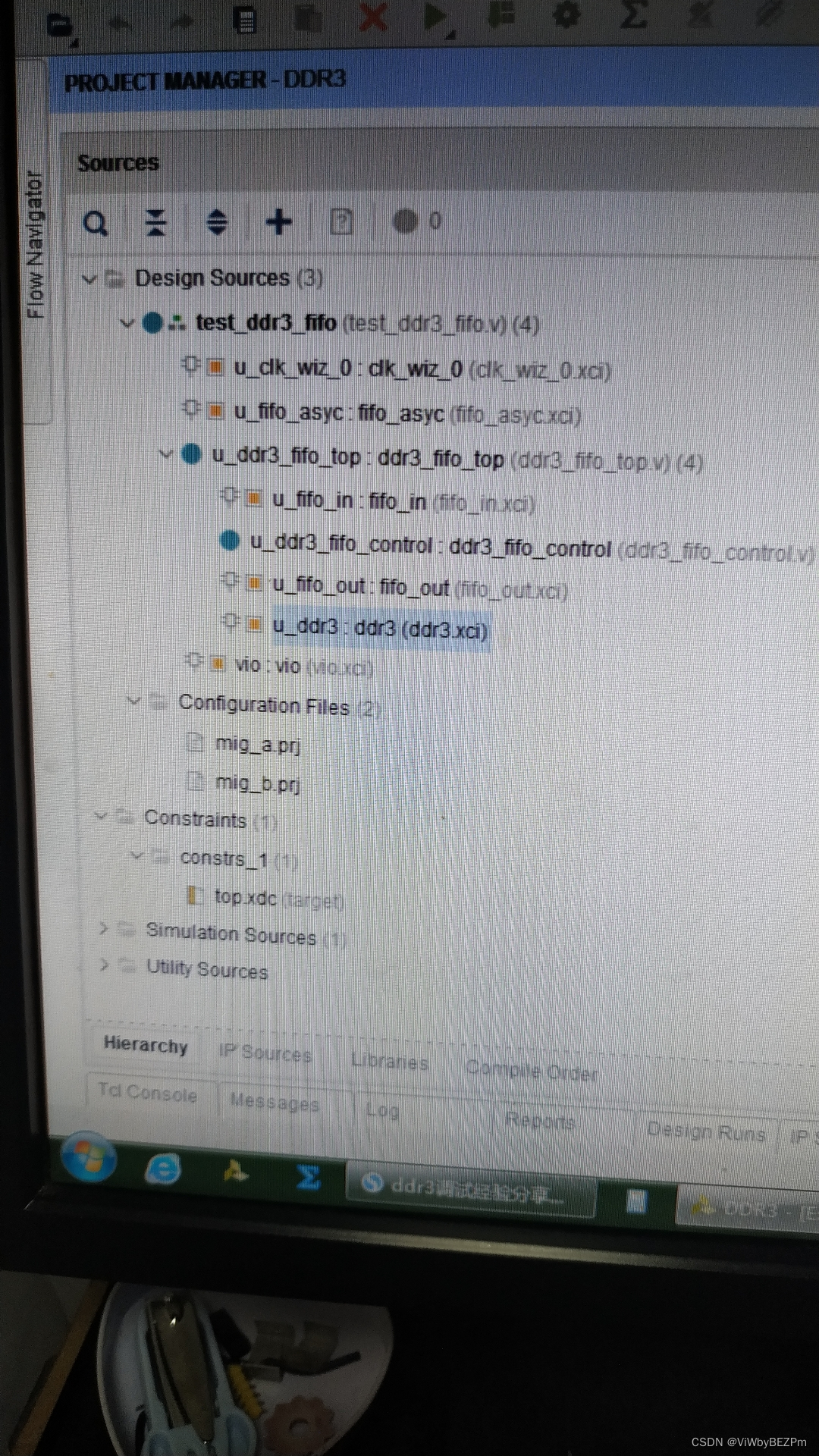

首先,我们来探讨如何使用Xilinx FPGA将DDR3配置成一个大型FIFO。FIFO是一种数据结构,可用于缓存和传输数据,即先进先出。FPGA通常用FIFO创建大容量缓存,以满足高速数据处理的需求。我们可以使用Verilog语言编写FIFO的代码,并将其应用于DDR3的配置。

在配置DDR3之前,需要确定以下参数:数据宽度、时钟速率和时序。数据宽度指的是数据总线的宽度,时钟速率是指FPGA系统时钟的速率,时序包括一系列时间参数,如读写延迟、预充电时间和刷新周期等。这些参数将影响DDR3的性能和稳定性。

在确定参数后,我们可以开始编写Verilog代码,并使用IP核将其集成到Xilinx Vivado开发环境中。IP核是一种可配置的硬件单元,可简化FPGA设计的复杂度。在Vivado中,可以使用IP核向设计中添加各种功能模块,并在IP仓库中查找各种IP核。

将DDR3配置成FIFO后,可以将其用于高速数据缓存。在实际应用中,我们可以使用FIFO缓存来处理大量数据,以提高处理速度和减少延迟。

除了DDR3,Xilinx FPGA还支持DDR4技术,可用于更高级别的数据处理。我这里推荐使用Xilinx DDR4多通道读写防冲突设计,它可以实现8个通道同时读写DDR且不冲突问题。这些通道可以通过独立的接口进行操作,从而实现更高效的数据传输。

Xilinx DDR4多通道读写防冲突设计的实现需要进行一些配置和编程。 首先,需要对内存控制器进行初始化,然后配置读写通道以防止冲突。在初始化期间,需要设置一些参数,如时序、数据宽度和时钟速率。这些参数应与DDR4的规格相匹配。

完成初始化后,就可以配置读写通道了。读写通道的配置涉及到一些复杂的算法,用于确保通道之间的数据传输不会发生冲突。这些算法需要基于时序和传输速率进行计算,以确保数据传输的精度和稳定性。

总的来说,Xilinx FPGA可以轻松地配置DDR3和DDR4内存,用于高速数据缓存和处理。通过使用FIFO和多通道读写防冲突设计,可以实现更高效的数据传输和处理。这些技术已经被广泛应用于各种应用程序中,如高频交易、机器学习和人工智能等领域。

相关代码,程序地址:http://lanzouw.top/673834971358.html

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?