目录

1. 简介

本文主要介绍了 AXI4-Stream 到视频输出 的内容。其中,示例工程展示了一个具体的设计,包括时钟、复位信号、视频数据以及一些参数设置。该示例工程使用 AXI4-Lite 接口配置视频输出的参数,例如图像的高度、宽度和背景图案。此外,文本还详细解释了 AXI4-Stream 到视频输出 IP 的组成部分,包括数据部分、时序信号部分和同步部分。同步器的工作原理涵盖了初始对齐阶段和时序模式,以实现数据和时序信号的同步。

2. 原理详解

2.1 示例工程

`timescale 1ns / 1ps

import axi_vip_pkg::*;

import design_1_axi_vip_0_0_pkg::*;

module tb_AXI4S_to_Vid_Out();

bit aclk = 0, aresetn = 0;

xil_axi_resp_t resp;

bit vid_hblank, vid_vblank, vid_hsync, vid_vsync ;

bit [23:0] vid_data;

integer counter_width = 0, counter_height = 0;

integer final_width = 0, final_height = 0;

parameter integer tpg_base_address = 12'h000;

parameter integer TPG_CONTROL_REG = tpg_base_address;

parameter integer TPG_ACTIVE_H_REG = tpg_base_address + 8'h10;

parameter integer TPG_ACTIVE_W_REG = tpg_base_address + 8'h18;

parameter integer TPG_BG_PATTERN_REG = tpg_base_address + 8'h20;

integer height=480, width=640;

always #12.5ns aclk = ~aclk; // 40MHz

design_1_wrapper UUT(

.aclk_40MHz (aclk),

.aresetn_0 (aresetn),

.vid_data (vid_data),

.vid_hblank (vid_hblank),

.vid_hsync (vid_hsync),

.vid_vblank (vid_vblank),

.vid_vsync (vid_vsync));

initial begin

#50ns aresetn = 1;

end

design_1_axi_vip_0_0_mst_t master_agent;

initial begin

master_agent = new("master vip agent",UUT.design_1_i.axi_vip_0.inst.IF);

master_agent.start_master();

wait (aresetn == 1'b1);

#200ns

master_agent.AXI4LITE_WRITE_BURST(TPG_ACTIVE_H_REG, 0, height, resp);

master_agent.AXI4LITE_WRITE_BURST(TPG_ACTIVE_W_REG, 0, width, resp);

master_agent.AXI4LITE_WRITE_BURST(TPG_BG_PATTERN_REG, 0, 9, resp);

#200ns

master_agent.AXI4LITE_WRITE_BURST(TPG_CONTROL_REG, 0, 8'h81, resp);

end

endmodule

注意:

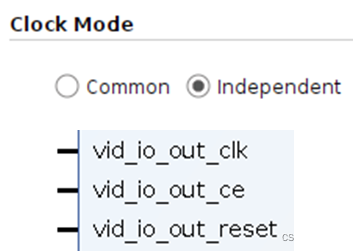

- 如果 Clock Mode 选用独立时钟,则启用fifo的跨时钟域功能。

- fifo深度如何设定?答:在根据fifo_flag调试;

- fid仅用于隔行扫描,很少用到;

2.2 AXI4-Stream to Video Out

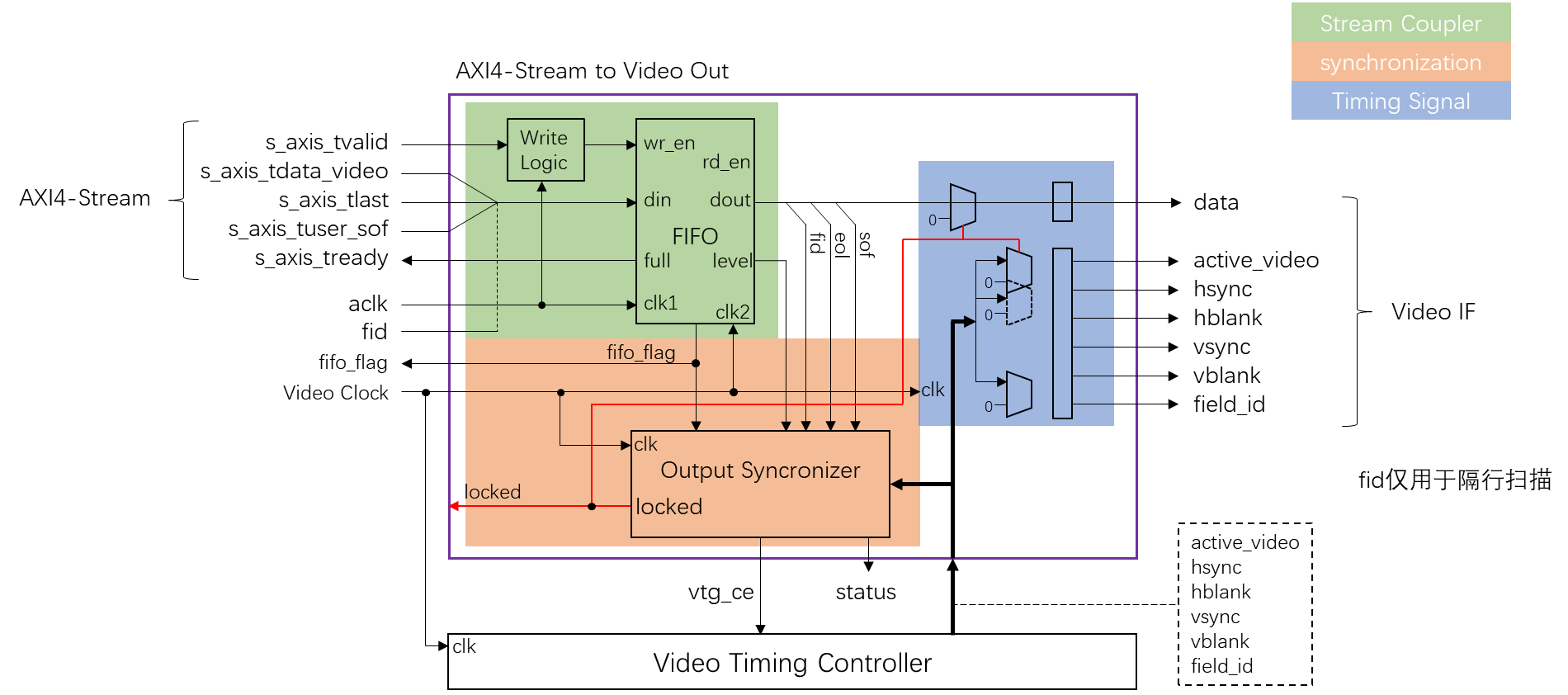

其中:

fifo_flag: overflow, underflow

status:

status[1] – Course Align, Wait for VTG SOF

status[3] – Fine Align, VTG EOL Leading

status[8] – Fine Align Locked

…

AXI4-Stream到视频输出IP的组成部分:

- 数据部分(红色):数据首先通过FIFO,然后进行格式化,以遵循Xilinx视频IP的AXI4-Stream编码(UG934中定义)。

- 时序信号部分(绿色):时序信号直接从VTC(视频时序控制器)传递给AXI4-Stream到视频输出IP,无需修改。

- 同步部分(橙色):输出同步器从AXI4-Stream接收帧边界信息信号(帧开始和行结束),以及来自VTC的时序信号,以实现数据和时序信号的同步。

同步器的工作原理:

- 初始对齐阶段:AXI4-Stream到视频输出首先进入粗对齐阶段,然后进入精细对齐阶段,最终锁定。具体的对齐细节可以在PG044中找到。

- 时序模式:根据Master或Slave模式,同步器控制VTC或内部FIFO,以实现同步。详细的时序模式说明在PG044的第3章中有。

- 输出同步器块从AXI4-Stream接收帧边界信息信号(tuser, or sof and eol)以及从VTC IP接收的时序信号作为输入,以同步数据和时序信号。根据时序模式(Master 或 Slave),它将控制VTC(使用vtg_ce)或内部FIFO以实现同步。

3. Master/Slave Timing Mode

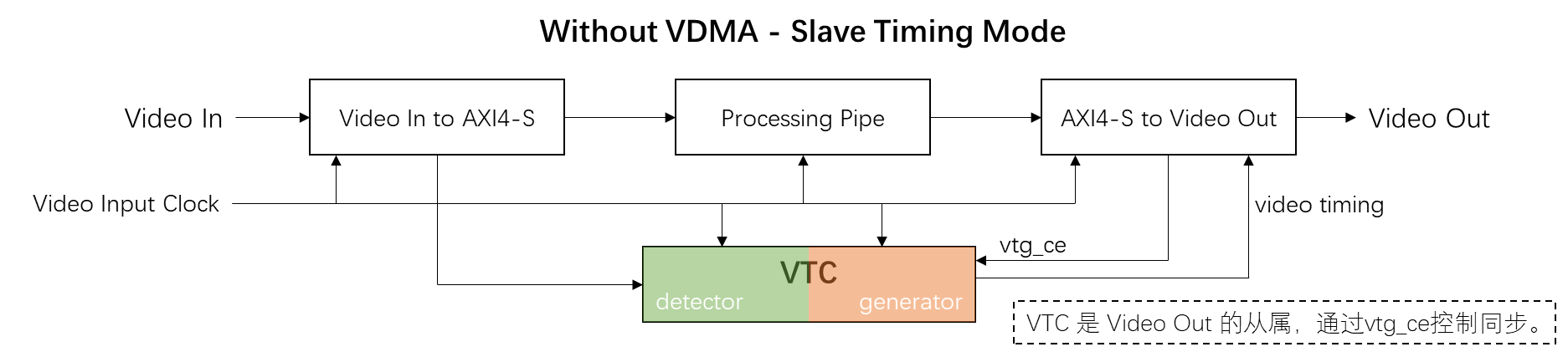

3.1 Slave Timing Mode

Slave Timing Mode,是指 VTC 是 Video Out 的从属,通过vtg_ce控制同步。

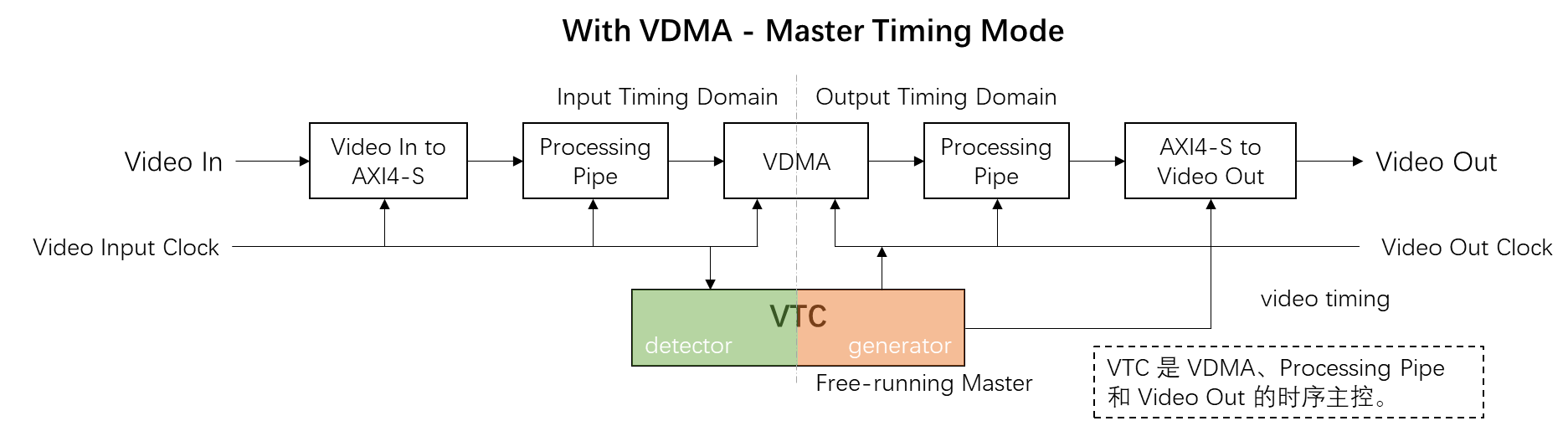

3.2 Master Timing Mode

Master Timing Mode,是指 VTC 是 VDMA、Processing Pipe 和 Video Out 的时序主控。

4. 总结

本文介绍了 AXI4-Stream 到视频输出的工作原理和示例工程。通过该工程,详细展示了如何使用 AXI4-Lite 接口配置视频输出参数,包括图像高度、宽度和背景图案等。AXI4-Stream 到视频输出 IP 包含数据部分、时序信号部分和同步部分,确保数据与时序信号的同步。同步器通过初始对齐和时序模式来实现这一目标,支持独立时钟模式下的跨时钟域功能。最后,解释了 Master 和 Slave 时序模式,分别由 VTC 控制同步信号和作为时序主控。总的来说,本文为实现视频输出提供了全面的技术指导和详细的操作示例。

668

668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?