基于ADRV9026的四通道射频收发FMC+子卡是一款基于 ADRV9026BBCZ 芯片的高集成度射频收发子卡,提供包含四通道发射器和四通道接收器、集成式频率合成器以及数字信号处理功能的收发方案。支持时分双工(TDD)和 FDD(频分双工)应用,可满足 3G、4G 和 5G 宏系统和大规模多路输入/输出(MIMO) 基站的应用要求。

接收路径由四个独立的宽带宽、直接变频(零中频) 接收器组成,可在低功耗实现低噪声运行,具有一流的动态范围。完整的收发器子系统拥有自动和手动衰减控制、直流失调校正、正交误差校正(QEC)和数字滤波功能。还集成了多种辅助功能,比如模数转换器(ADC)、数模转换器(DAC)和用于提供各种数字控制选项的通用输入/输出(GPIO)接口。

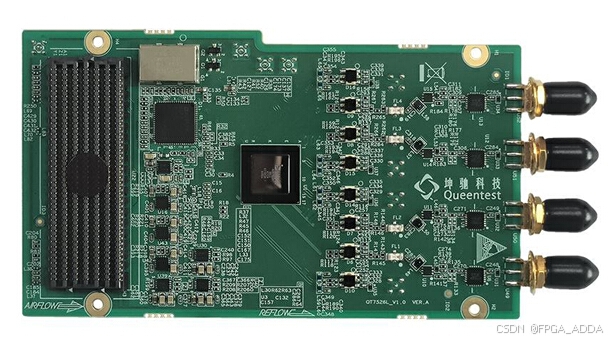

使用HSPC 连接器作为标准 FMC+接口,对外提供 12 个同轴连接器,其中 4 个 SMA 个为 Rx 收,4 个 XSMP 为 Tx 发,还有 1 个MMCX 为外部触发输入,2 个 MMCX 为外部观测接收通道输入,1 个MMCX 为参考时钟通道,可由载板通过 FMC+连接器控制为参考时钟输入或者输出。 QT7526L 能支持速率最高达 24.33 Gbps 的 JESD204B/ JESD204C 数字接口通道。

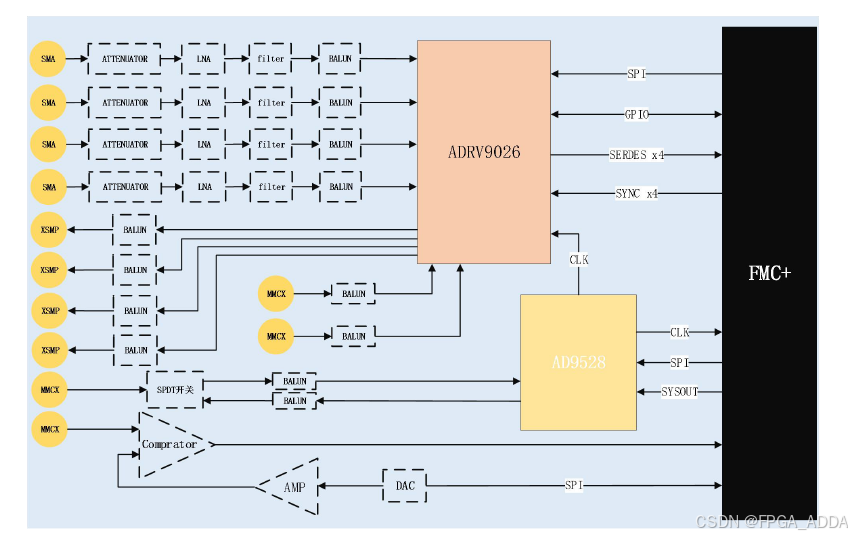

板卡功能框图

板卡性能:

- TX输出

- 交流耦合;

- DAC分辨率:14Bits;

- 四发射器;

- 最大可调谐发射器合成带宽:450MHz;

- JESD204B/C数据接口;

- 接收采样率:最高500Msps;

- 中心频率:75MHz~6000MHz;

- XSMP连接器;

- RX输入

- 交流耦合;

- 四接收器;

- ADC分辨率:14Bits;

- 最大接收器带宽:200MHz;

- JESD204B/C数据接口;

- 发送采样率:最高250Msps;

- 中心频率:75MHz ~ 6000MHz;

- SMA连接器;

- ORX输入

- 交流耦合;

- 2接收器;

- 最大观察接收器带宽:450MHz;

- MMCX连接器;

- 时钟

(1)内参考时钟:30.72MHz;

(2)外参考时钟:10 ~ 400MHz;

(3)交流耦合;

(4)MMCX连接器;

- 功耗

(1)+12V: <0.7A;

(2)+3.3V: <0.02A; (3)Vadj(+1.8V):<0.8A;

应用

- 软件无线电

- 宽带 MIMO 应用

- 宏蜂窝时分双工(TDD)基站

- (雷达/声纳)电子战

- 模拟记录和回放系统

- 信号智能检测和测试仪器

功能特点:

- 12 个射频同轴连接器,其中 4 个 SMA 个为 Rx 收,4 个 XSMP 为 Tx 发,1 个 MMCX 为外部触发输入,2 个 MMCX 为外部观测接收通道输入,1 个 MMCX 为参考时钟通道;

- 四发射器和四接收器;

- 双输入共享观察接收器;

- 最大接收器带宽:200 MHz;

- 最大可调谐发射器合成带宽:450 MHz;

- 最大观察接收器带宽:450 MHz;

- 全集成的小数 N 射频合成器;

- 全集成的时钟合成器;

- 适用于射频 LO 和基带时钟的多芯片相位同步;

- JESD204B/C 数据路径接口;

- 调谐范围:75 MHz 至 6000 MHz;

- 适应范围:管脚定义完全符合 Vita57.4 规范,只是长度稍长;

- 散热方式:风冷;

- 单 HSPC 连接器;

- 工作温度:商业级 0℃~+55℃ ,工业级-20℃~+65℃;

功能实现:

FMC 子卡基于 ADRV9026 实现。板上提供基于 AD9528 的高性能时钟方案,子卡上提供 30.72MHz 的 TCXO 作为系统时钟源,提供高性能 PLL,PLL 输出的低相噪时钟和同步信号,同时提供给中频收发器和连接到FMC+插座的 FPGA 作为参考,如果需要更精确的时钟源,子卡也可以通过板上的 MMCX 连接器,由外部(信号源/频谱仪参考输出等) 输入 30.72MHz 的参考时钟。另外,如果需要多块子卡实现多通道收发并要求同步,也可以由载板(包含FPGA 和同步时钟源的板卡)统一通过 FMC+接插件下发同步时钟,达到多子卡同步的目的。

1506

1506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?