Arm Armv9-A A64 Instruction Set Architecture

Arm使用的是RISC(精简指令集)

Contents

ARMv9文档

零、简单介绍

目前来说:Intel和AMD的CISC广泛用于PC机,而高通、联发科、苹果等基于RISC的ARM芯片广泛用于移动设备(ipad,手机等)

Intel和ARM对比

Intel被诟病挤牙膏?

Intel通常第一年更新制作工艺(制程),第二年保持其他不变,更新\改变架构,第三年保持其他不变,优化CPU…三年一个循环,更新周期长,每年挤一点。

一、Base Instructions基本指令集

1.数据传送指令

传送指令:mov,movk(Move wide with keep.),movn(Move wide with NOT),movz( Move wide with zero.)

mov dst,src

(1) CPU内部寄存器之间的数据传送,如:

mov ah,al

(2) 立即数送至通用寄存器(非段寄存器)或存储单元,如:

mov al,3

mov [bx],1234h

(3) 寄存器与存储器间的数据传送,如:

mov ax,var

mov ax,[bx

(4)movk将一个可选移位的16位即时值移动到寄存器中,保持其他位不变。

2.加减运算指令

加法指令:add、adc、cinc\csinc<-inc,

(1) add(Addtion)

格式:ADC des_reg, source_reg1, source_reg1

功能:ADC des_reg=source_reg1+source_reg1

注: 影响FLAG

(2) adc(add with Carry) ;带进位的加法

格式:ADC des_reg, source_reg1, source_reg1

功能:带进位的加法,des_reg=source_reg1+source_reg1 + CF

注: 影响FLAG,主要用于多字节运算

(3) csinc(Conditional Select Increment)

格式:CSINC des_reg, source_reg1, source_reg1, <cond>

功能:if(cond==ture)

des_reg=source_reg1;

else

des_reg=source_reg2+1;

注: 不影响CF

减法指令:sub,cmp

(1) sub(Subtraction)

格式:sub OPRD OPRD1,OPRD2

功能:OPRD = OPRD1 - OPRD2

(3) cmp(decrement)

格式:CMP <Xn|SP>, #<imm>

cmp OPRD1,OPRD2

功能:OPRD = OPRD1 - OPRD2

根据OPRD的结果进行判断,改变标志寄存器中对应的标志位

注:cmp不改变原数的大小,影响标志位CF、ZF、SF、OF、AF、PF来判断OPRD1和OPRD2的大小关系。通过ZF判断是否相等;如果是无符号数,通过CF可判断大小;如果是有符号数,通过SF和OF判断大小

3.乘除运算指令

乘法指令:UMADDL、SMADDL

(1)UMADDL(Multiply) ;无符号数乘法指令

格式:UMADDL OPRD

功能:将OPRD与EAX中的操作数相乘,结果保存在EDX:EAX中

注: 无符号数相乘分为32位*32位,结果为64位,保存将结果写入64位目标寄存器。

(2) SMADDL<-imul(Signed Multiply) ;有符号数乘法指令

格式:IMUL OPRD

功能:将两个32位寄存器值相乘,得到一个64位寄存器值,并将结果写入64位目标寄存器。

除法指令:udiv,sdiv

(1) UDIV(Division) ;无符号数除法指令

格式:UDIV <destination>, <first sourse>, <second sourse>

功能:无符号数除法,first sourse为被除数,second sourse为除数

(2) SDIV(Signed Division) ;有符号数除法指令

格式:SDIV <destination>, <first sourse>, <second sourse>

功能:将一个有符号整数寄存器值除以另一个有符号整数寄存器值,并将结果写入目标寄存器。条件标志不受影响。

4.逻辑运算指令

逻辑运算指令:neg、and、orr、orn、tst

(1) NEG<-not

格式:NOT OPRD

功能:把操作数OPRD取反,然后送回OPRD。

注: OPRD可以是通用寄存器,也可以是存储器操作数,此指令对标志没有影响

(2) AND

格式:AND OPRD1,OPRD2

功能:对两个操作数进行按位逻辑“与”运算,结果送到OPRD1中

注: 该指令执行后,CF=0,OF=0,标志PF、ZF、SF反映运算结果,AF未定义。

某个操作数与自身相与,值不变,但可以使CF置0。

(3) ORR<-or

格式:ORR OPRD1,OPRD2

功能:对两个操作数进行按位逻辑“或”运算,结果送到OPRD1中

注: 该指令执行后,CF=0,OF=0,标志PF、ZF、SF反映运算结果,AF未定义。

某个操作数与自身相或,值不变,但可以使CF置0。

(4) ORN<-xor

格式:ORN OPRD1,OPRD2

功能:对两个操作数进行按位逻辑“异或”运算,结果送到OPRD1中

注: 该指令执行后,CF=0,OF=0,标志PF、ZF、SF反映运算结果,AF未定义。

(5) TST<-test

格式:TEST OPRD1,OPRD2

功能:把OPRD1与OPRD2按位“与”,但结果不送到OPRD1中,仅影响标志位。

注: 该指令执行后,CF=0,OF=0,标志PF、ZF、SF反映运算结果。常用于检测某些位是否为1

5.移位运算指令

LSR 逻辑右移

ASR 算术右移

ROR 循环右移

(1) LSR(Logic Shift Right) ;逻辑右移指令

格式:LSR OPRD,m

功能:操作数右移m位,同时每移1位,左边用0补足,移出的最低位进入标志位CF

注: 对无符号数,逻辑右移1位相当于除以2

(2) ASR(Shift Arithmetic Right) ;算数右移指令

格式:ASR OPRD,m

功能:操作数右移m位,同时每移1位,左边的符号位保持不变,移出的最低位进入标志位CF

注: 对有符号数和无符号数,算数右移1位相当于除以2

(3)ROR(Rotate Right) ;循环右移指令

格式:ROR OPRD,m

功能:把操作数OPRD右移m位,每移动一位,将右边移出的那一位放在最左边的空缺处。

6.控制指令

LDR加载指令

格式:LDR <Xt>, [<Xn|SP>, (<Wm>|<Xm>)

功能:通过基址寄存器Xn+变址寄存器Xm查找得到的内存中对应的存储单元中值,将该值写入到寄存器Xt中

— LDRB 字节数据加载指令

— LDRH 半字数据加载指令

STR存储指令

格式:STR <Xt>, [<Xn|SP>, (<Wm>|<Xm>)

功能:将通用寄存器Xt的值,放入通过基址寄存器Xn+变址寄存器Xm得到的对应的存储单元中

— STRB 字节数据存储指令

— STRH 半字数据存储指令

二、SIMD&FP Instructions

SIMD单指令流多数据流(Single Instruction Multiple Data)

以及浮点数运算指令FP Instructions

三、SVE Instructions

SVE=Scalable Vector Extension可伸缩矢量扩展

SVE引入了很多新的架构特点, 比如

• 可变矢量长度

• 每通道预测

• 聚集加载和分散存储

• 横向操作

四、Index by Encoding

五、Shared Pseudocode

六、Proprietary Notice

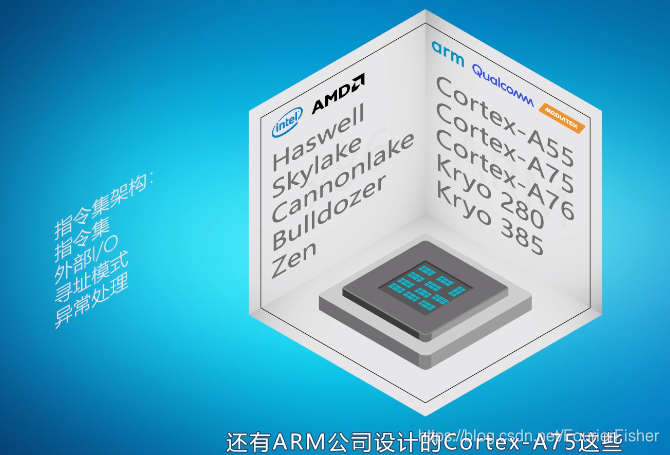

七、ARMv9与ARMv8的不同

从指令集角度来看,从ARMv7到ARMv8的变化的具有革命性的,指令的位数从32bit拓展到64bit,单条指令可以执行更多的操作。

而从ARMv8到ARMv9,虽然单条指令的位数上没有发生拓展,但是通过查阅资料不难发现,ARMv9具有三大优势:AI(机器学习)、矢量和 DSP 性能改进以及安全性。

所以最显著的是,ARMv9相较于ARMv8,增加了许多矩阵运算的指令。例如矢量运算、矩阵运算等。

2095

2095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?