FPGA实现74LS160计数器功能Verilog程序+仿真

用 Verilog 语言设计一个和 TTL 电路功能相同的74LS160 同步十进制计数器,参考74LS160 的pdf 文档,用仿真测试电路模块的功能。

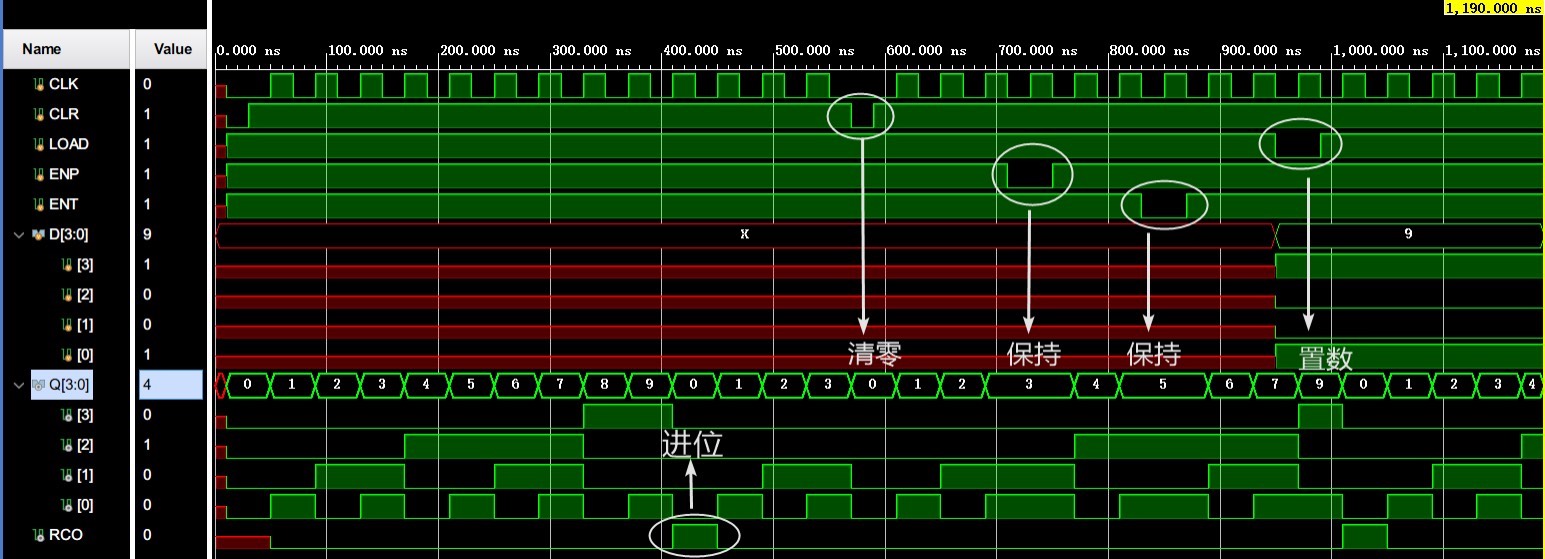

74LS160 的计数范围为0~9,用4 位BCD 码表示,在时钟上升沿时计数,一个计数周期完成后会产生一个进位信号,并开始下一轮计数循环。

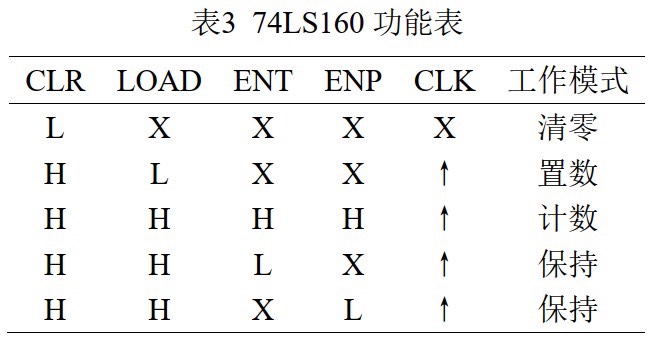

清零、置数、保持均为低电平有效,其中清零信号不受时钟限制,两个保持端只要有一个为低电平则进入数据保持模式。

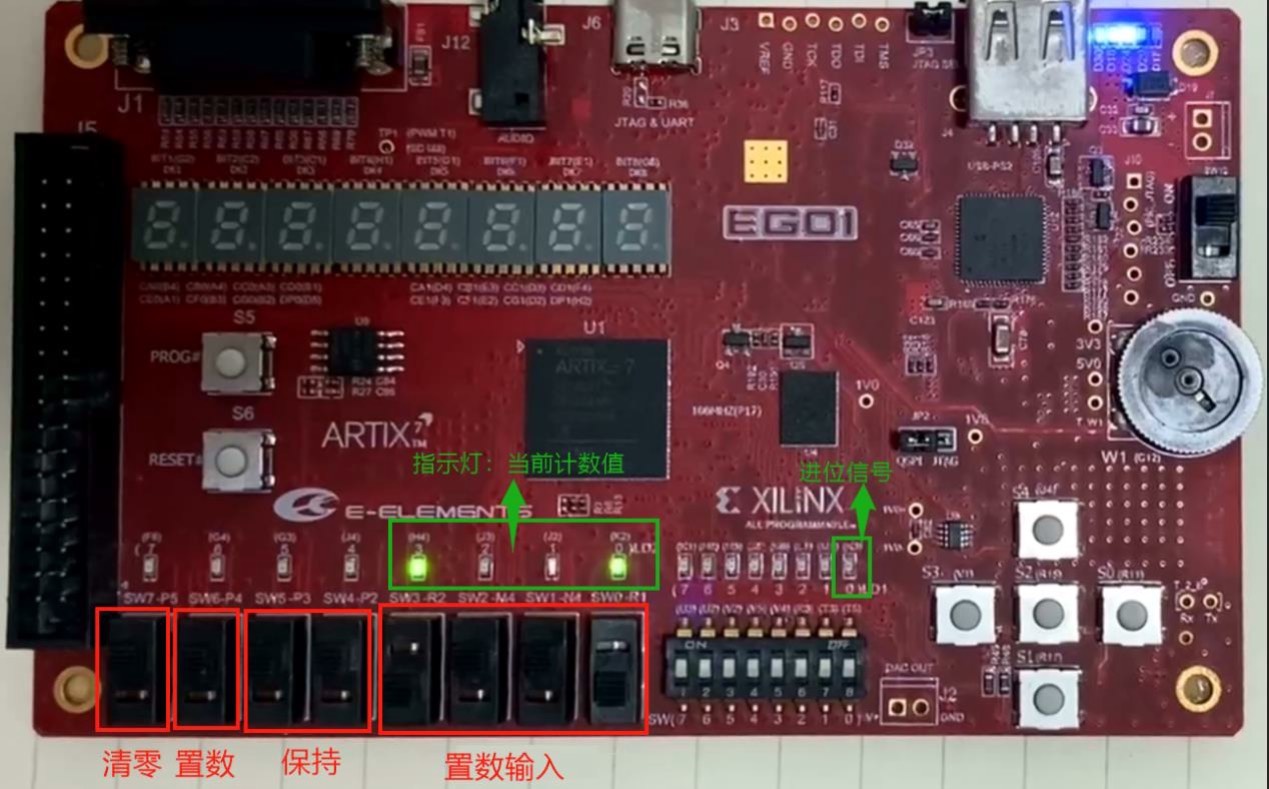

本程序采用了自顶向下的设计思想,总共分为三个模块,顶层模块(top.v)由分频模块(FrequncyDiv.v)和74LS160 计数器模块(Counter74LS160.v)组成。

其中分频模块的作用是将FPGA 开发板上频率为100MHz 的时钟信号转换为周期1s 的时钟信号。

ID:4124694176380835

女巫的工具箱

FPGA实现74LS160计数器功能Verilog程序+仿真

摘要:本文介绍了使用Verilog语言设计并实现一个和TTL电路功能相同的74LS160同步十进制计数器的方法。通过参考74LS160的pdf文档,并使用仿真测试电路模块的功能,实现了计数范围为0~9、使用4位BCD码表示的计数器。设计采用了自顶向下的设计思想,分为顶层模块、分频模块和74LS160计数器模块三个模块。

-

引言

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有高度灵活性和可重构性。通过使用Verilog语言来设计和实现电路功能,可以充分发挥FPGA的性能优势。本文主要介绍了在FPGA上实现74LS160计数器功能的方法,并提供了对应的Verilog程序和仿真测试。 -

74LS160计数器功能介绍

74LS160是一款十进制计数器,计数范围为0~9。它使用4位BCD码表示,并在时钟上升沿进行计数。每个计数周期完成后会产生一个进位信号,并开始下一轮计数循环。该计数器具有清零、置数和保持功能,其中清零信号不受时钟限制,只要两个保持端中有一个为低电平,就会进入数据保持模式。 -

设计思路

为了实现74LS160计数器功能,本文采用了自顶向下的设计思想,将整个设计分为三个模块:顶层模块、分频模块和74LS160计数器模块。

3.1 顶层模块

顶层模块(top.v)是整个设计的最高层次,它由分频模块和74LS160计数器模块组成。顶层模块的主要功能是将FPGA开发板上的100MHz时钟信号转换为周期为1s的时钟信号。

3.2 分频模块

分频模块(FrequencyDiv.v)是顶层模块的子模块之一,它的作用是将100MHz的时钟信号分频,生成1s的时钟信号。分频模块可以根据需求自定义分频比例,以满足不同的应用场景。

3.3 74LS160计数器模块

74LS160计数器模块(Counter74LS160.v)是顶层模块的另一个子模块,它实现了74LS160计数器的功能。该模块使用4位BCD码来表示计数器的值,并在时钟上升沿进行计数。当一个计数周期完成后,模块会产生一个进位信号,并开始下一轮的计数循环。同时,该模块还实现了清零、置数和保持功能,通过控制对应的输入信号,可以实现不同的操作。

- Verilog程序实现

根据上述设计思路,我们可以编写对应的Verilog程序来实现74LS160计数器

以上相关代码,程序地址:http://wekup.cn/694176380835.html

3803

3803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?