一、设计目的

1、学会用HDL语言设计时序电路;

2、用HDL语言设计74LS160计数器芯片的数字功能。

二、设计原理

计数器是最常用的寄存器逻辑电路,从微处理器的地址发生器到频率计都需要用到计数器。一般计数器可以分为两类:加法计数器和减法计数器。加法计数器每来一个脉冲计数值加1;减法计数器每来一个脉冲计数值减1。

下面将通过模仿中规模集成电路74LS160的功能,用HDL语言设计一个十进制可预置计数器。74LS160共有一个时钟输入端CLK,一个清除输入端CLR,两个计数允许信号P和T,4个可预置数据输入端D、C、B、A,一个置位允许端LOAD,4个计数输出端QD、QC、QB、QA,一个进位输出端RC,其工作模式及时序图如下表和图2-14所示。

| 功能 | 输入 | 输出 | ||||

| 操作 | CLR | CLK | P | T | LOAD | QD、QC、QB、QA |

| 复位 | L | X | X | X | X | L、L、L、L |

| 预置 | H | ↑ | X | X | L | D、C、B、A |

| 计数 | H | ↑ | H | H | H | +1 |

| 保持 | H | X | L | X | H | QD、QC、QB、QA |

| 保持 | H | X | X | L | H | QD、QC、QB、QA |

注:进位输出端RC=Q3&!Q2&!Q1&Q0&T

三、设计内容

本实验要完成的任务就是实现中规模集成电路74LS160的功能,观察其工作时序,并下载到芯片中观察其实际工作过程。

实验时为了便于观察,需经分频得到1Hz时钟,用拨挡开关的SW1A~SW4A作为计数器的输入D,按键F3和F4作为计数器的控制允许P和T信号,F2作为清除输入CLR,用按键开关模块的F1作为LOAD信号(注意:由于计数器采用的是1Hz时钟,而装载数据是在时钟信号的上升沿作用下进行,所以要想正确的加载预制数据,F1按键必须按住至少1s以上才可以),用七段数码管模块中的某一位作为计数器的输出Q指示,用LED8作为计数器的输出翻转信号RC指示。

四、设计结果

1、74LS160源程序:

module A74LS160(clr,clk,et,ep,load,datain,dataout,rc,smg);

input clr,clk,et,ep,load;

input [3:0] datain;

output [6:0] smg;

reg [6:0]smg;

output [3:0] dataout;

output rc;

reg rc;

reg clk2;

reg [3:0] q1;

reg [8:0] cnt;

wire clr;

parameter n=50000000;

always@(posedge clk)

begin

if(cnt<(n/2-1))

begin

cnt<=cnt+1'b1;

clk2<=clk2;

end

else

begin

cnt<=9'd0;

clk2<=~clk2;

end

end

always@(posedge clk2 or negedge clr)

begin

if(clr==0)

begin

q1<=4'd0;

end

else

begin

if(clk2==1&load==0)

q1=datain;

else if(clk2==1&load==1)

begin

if(ep==1&et==1&q1<4'd10)

begin

q1=q1+1;

rc=0;

end

else if((et&ep)==0)

begin

q1=q1;

rc=0;

end

else if(q1==4'd10)

rc=1;

end

end

end

assign dataout=q1;

always@(dataout)

begin

case(dataout)

4'b0000:smg=7'b0000001;

4'b0001:smg=7'b1001111;

4'b0010:smg=7'b0010010;

4'b0011:smg=7'b0000110;

4'b0100:smg=7'b1001100;

4'b0101:smg=7'b0100100;

4'b0110:smg=7'b1100000;

4'b0111:smg=7'b0001111;

4'b1000:smg=7'b0000000;

4'b1001:smg=7'b0001100;

4'b1010:smg=7'b0001000;

endcase

end

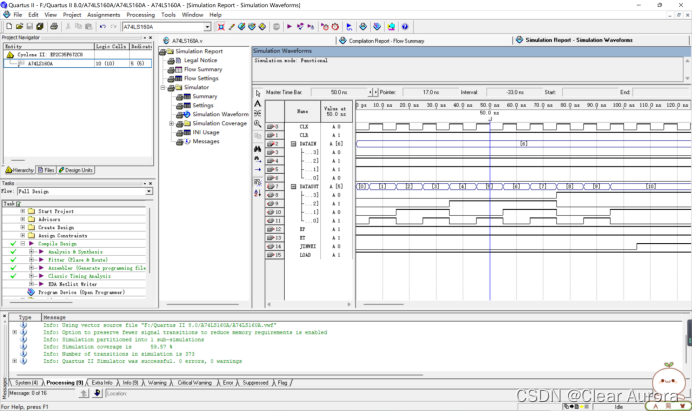

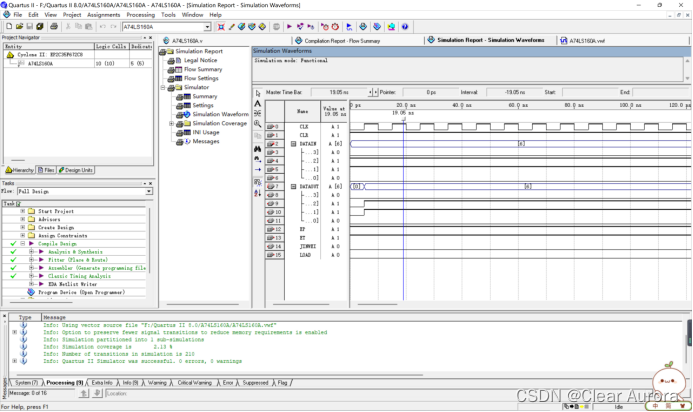

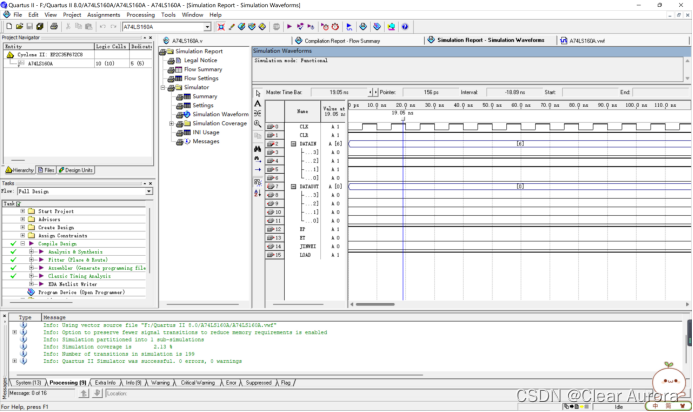

endmodule2、仿真波形图:

上图为未分频仿真74LS160在普通计数模式下的结果。

上图为未分频仿真74LS160预置数为6的结果。

上图为未分频仿真74LS160保持输出为0不变功能结果。由于50M分频时仿真时钟波形不够显示50000000次时钟波形,所以计数器模块输出结果未显示出,便不再附图。

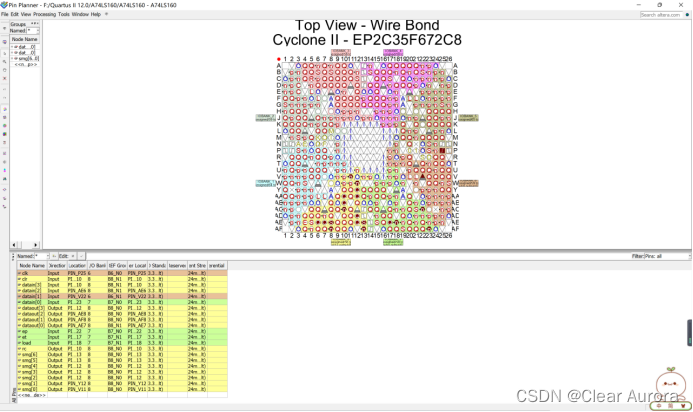

3、管脚约束:

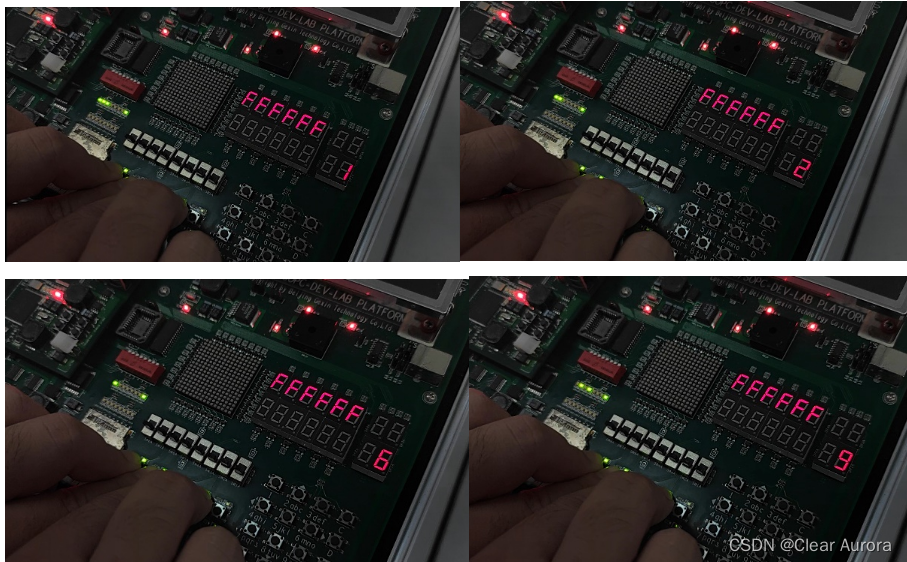

4、下载到试验箱上的结果:

4、下载到试验箱上的结果:

上图为模块EP、ET、LOAD、CLR端完全置1,处于普通计数模式时数码管的计数显示结果,此模式下计数显示每隔一秒加一,同时也说明了时钟50MHz被成功分频为1Hz。

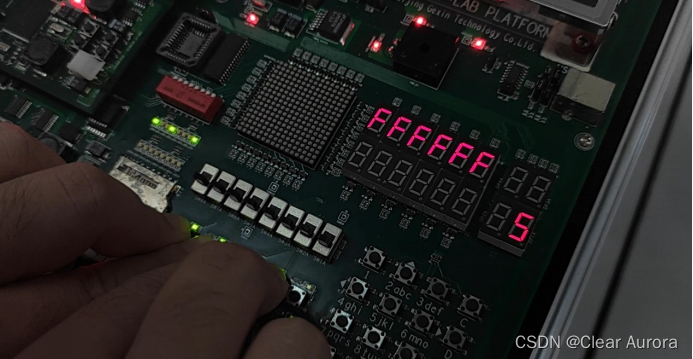

上图为模块EP端置0,ET、LOAD、CLR端完全置1,输出结果保持不变的情况。同理模块ET端置0,EP、LOAD、CLR端完全置1,也可达到保持的功能。

上图为模块EP端置0,ET、LOAD、CLR端完全置1,输出结果保持不变的情况。同理模块ET端置0,EP、LOAD、CLR端完全置1,也可达到保持的功能。

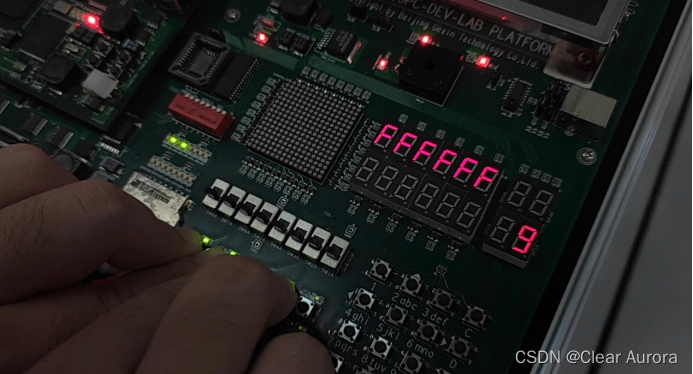

上图为计数到10,进位端被置1,进位标志位使LED熄灭的结果。

五、注意

将所有功能的程序糅杂在一个module中会使程序复杂化,难以改动,应将争取将其进行例化,采用模块结构描述,使程序更简洁明了,更直观,易改动易移植。

该文详细介绍了使用HDL语言设计74LS160计数器的过程,包括设计目的、设计原理和设计内容。通过模仿74LS160的功能,创建了一个十进制可预置计数器,并进行了仿真验证,展示了不同工作模式下的计数器行为。最后,讨论了程序优化的注意事项,强调模块化设计的重要性。

该文详细介绍了使用HDL语言设计74LS160计数器的过程,包括设计目的、设计原理和设计内容。通过模仿74LS160的功能,创建了一个十进制可预置计数器,并进行了仿真验证,展示了不同工作模式下的计数器行为。最后,讨论了程序优化的注意事项,强调模块化设计的重要性。

6090

6090

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?