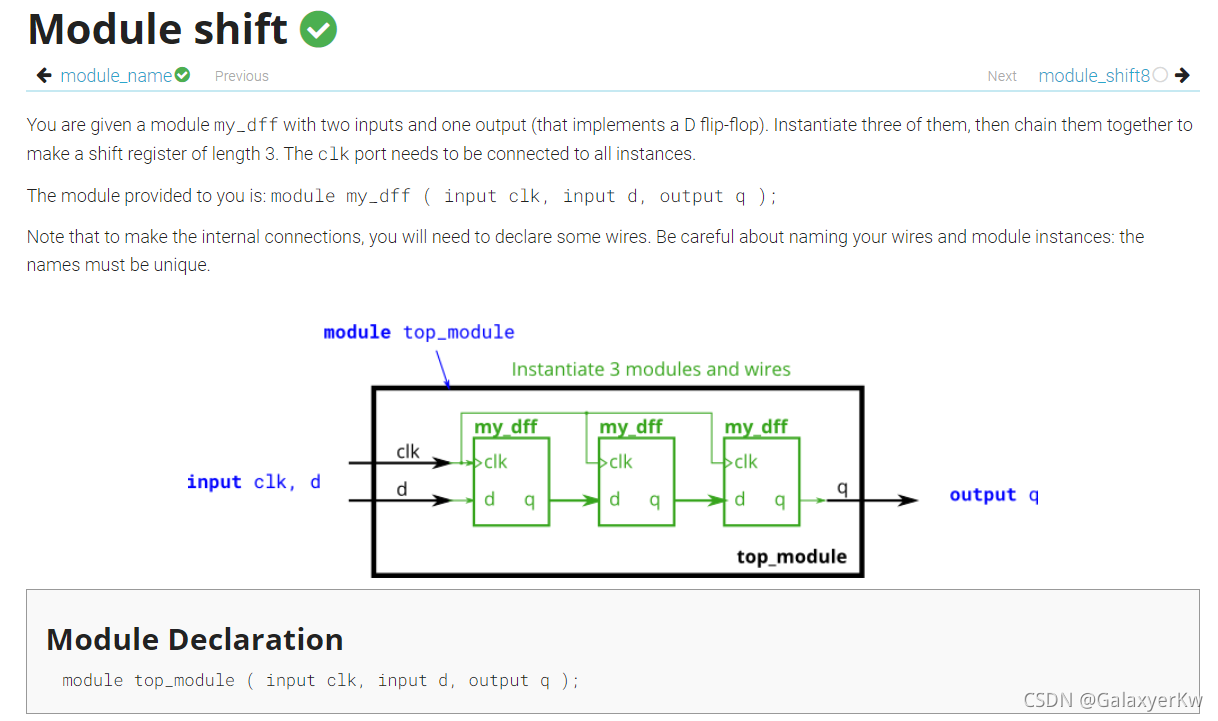

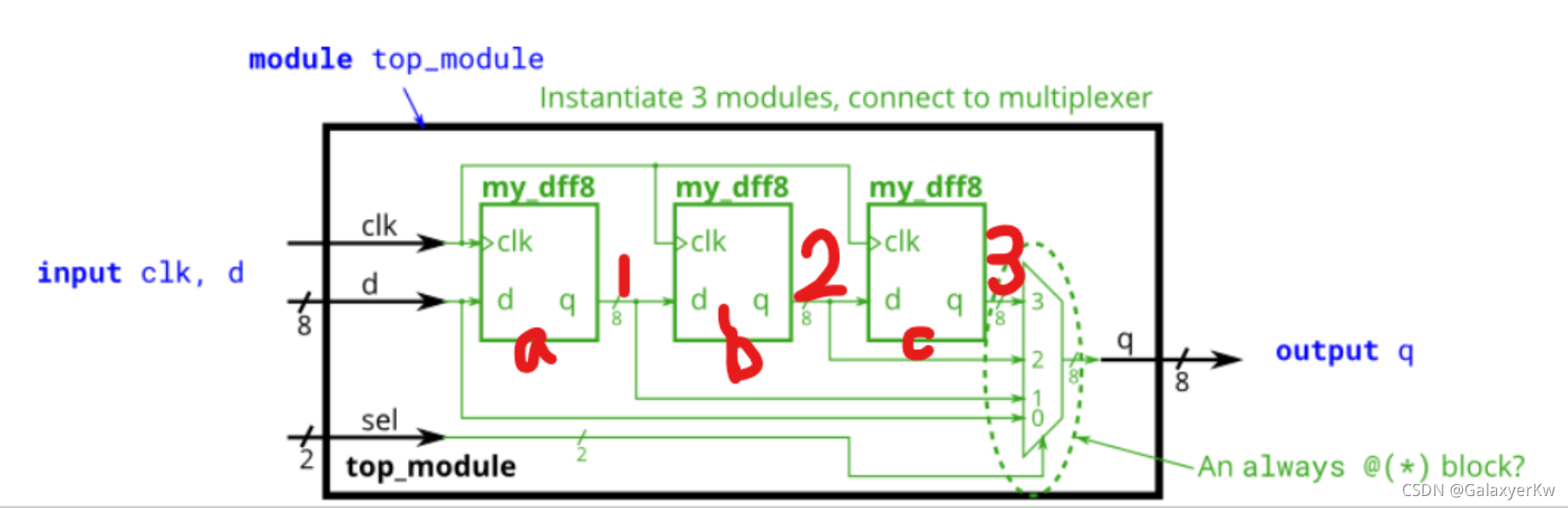

一.通过wire变量达成不同子模块的互相连接

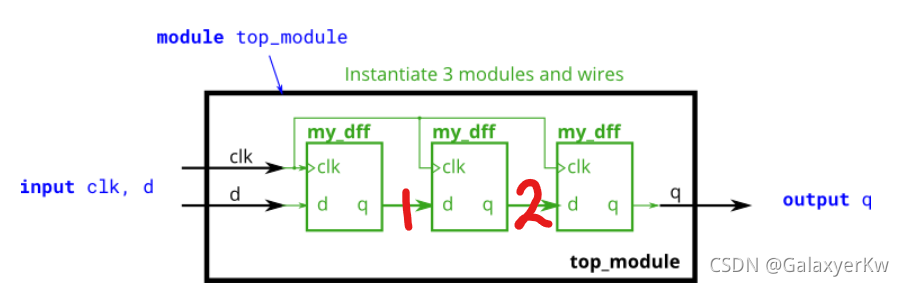

我们通过创建wire变量互通这几个子模块的q→d,然后通过端口名称互联子模块与顶层模块:

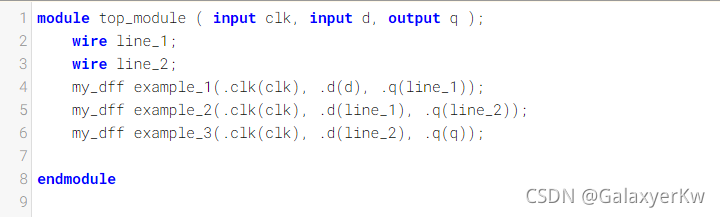

程序如下:

写出这个程序你需要知道的知识:

①子模块的定义,声明和调用(实例化)。

②子模块与顶层的连接方法(by name)。

③wire变量存放二进制信号,由此起到承接作用。

【练习地址链接:Module shift】

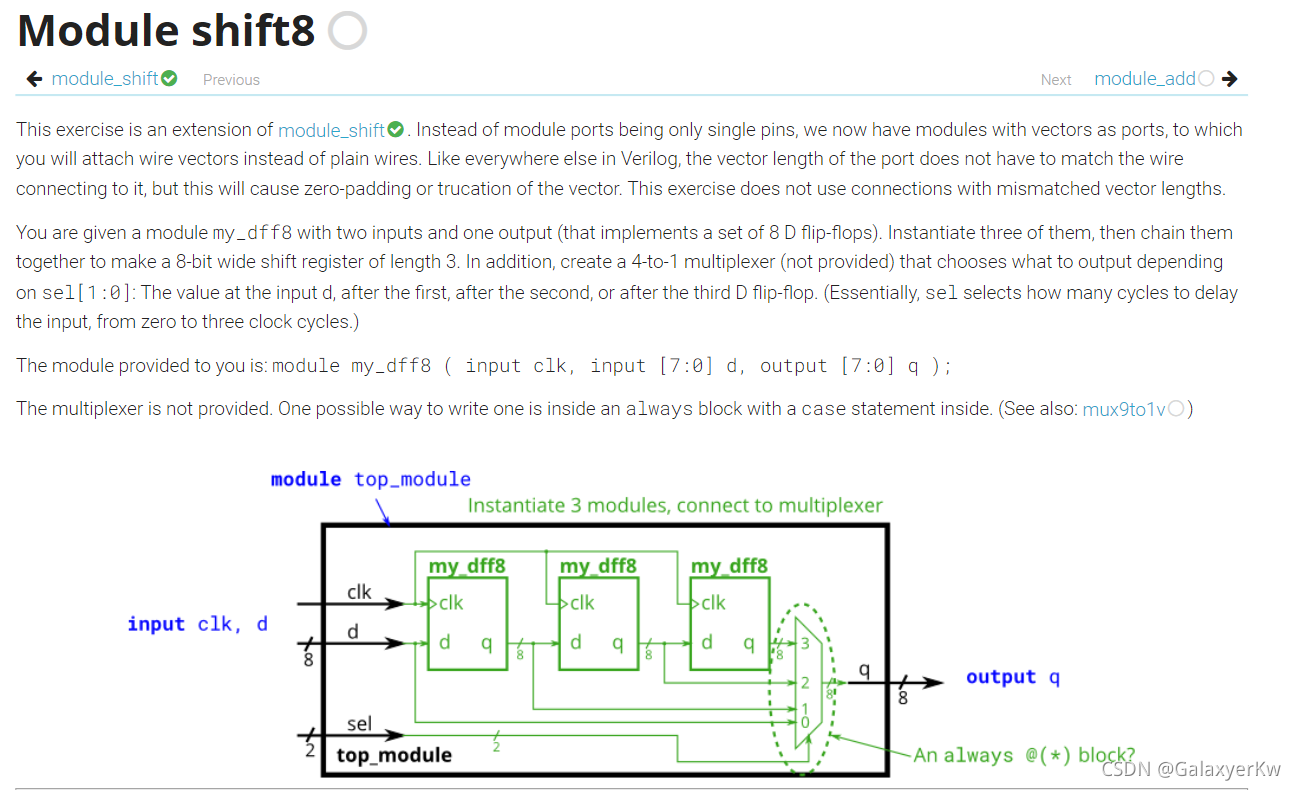

二.稍复杂一些的例子

注意:

①此例不仅需要互联子模块,而且需要传输多位的信号。

②关键性的一步在最后四个8位信号经过“信号选择器”(梯形元件),并由一个二位信号sel控制输出。信号选择器的实现需要借助alway@(*)语句。

下图是wire和实例的一些名称规定:

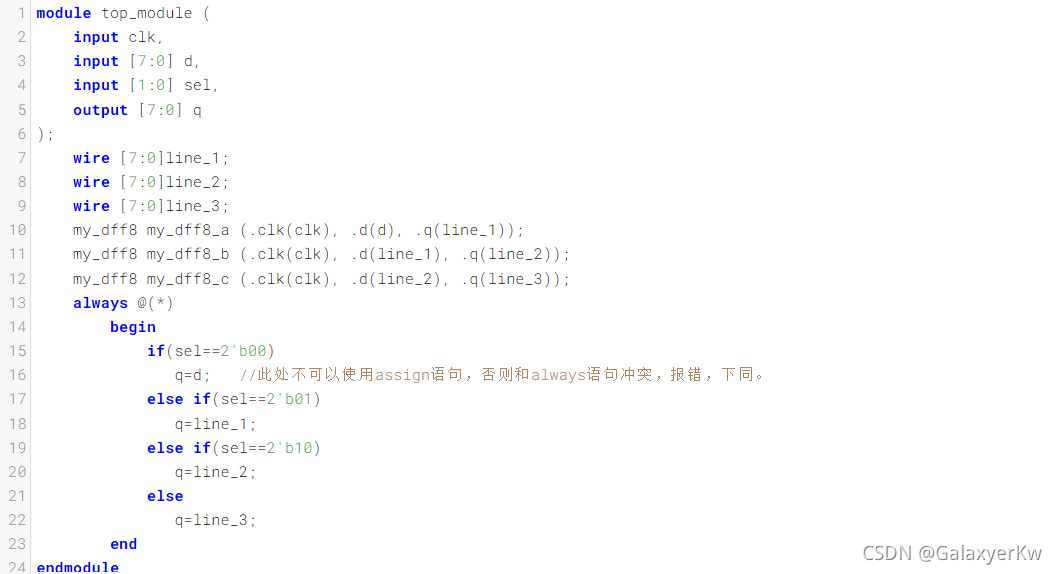

程序如下:

【练习地址链接:Module shift8】

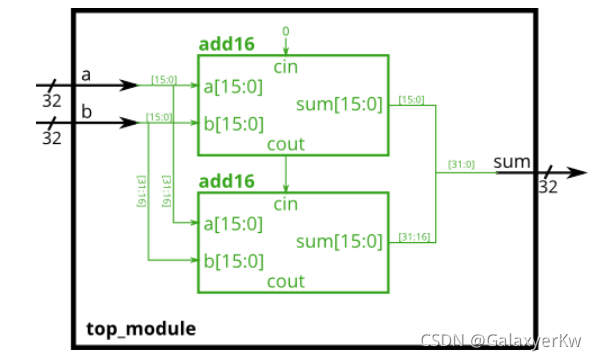

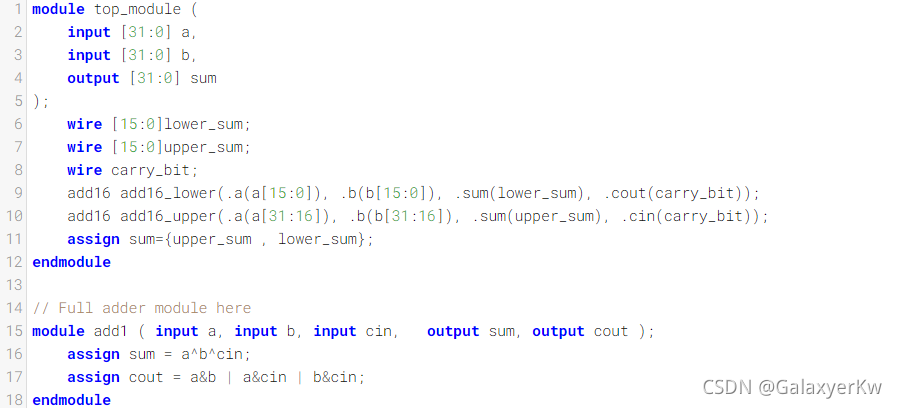

三.加法器的设计

如图所示的32位加法器是将一个32位的信号拆分成“高16位”和“低16位”,分别运算再整合。其中cin和cout管控“进位”:低16位运算的进位通过cout传输给cin,低16位初始没有进位值,所以低16位加法器传入的cin==0。因此,每一个加法器实际上在运算a+b+cin。

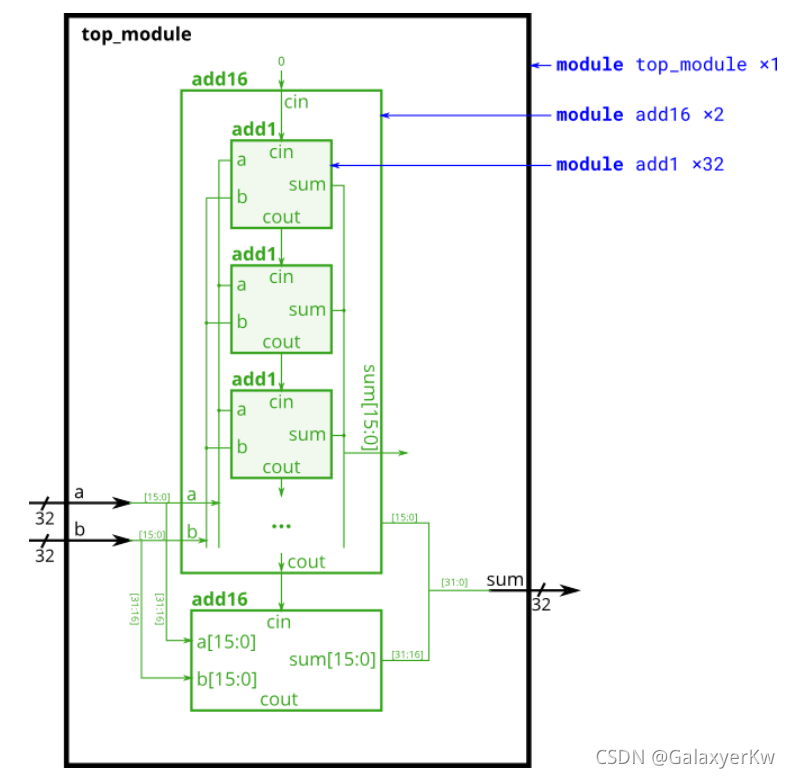

上述的加法器其实是“全加器”,其内部是由多个“半加器”复合而成的:

每一个半加器(图中的add1)只能操作两个1位信号的加法运算。不难看出,一个“16位全加器”是由8个“半加器”复合而成的。

半加器输入两个一位信号,输出两个信号:“和”和“进位”,逻辑门如下:

sum = a ^ b ^ cin

cout = a&b | a&cin | b&cin

现在,我们通过代码来实现“半加器”:

(需要考虑半加器的逻辑门设计,不需要考虑半加器之间的连接)

【练习地址链接:Module fadd】

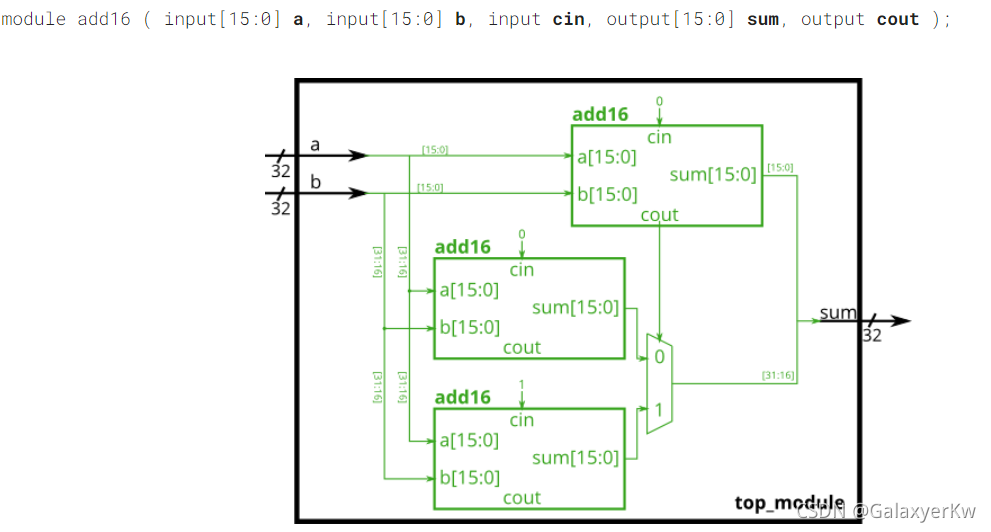

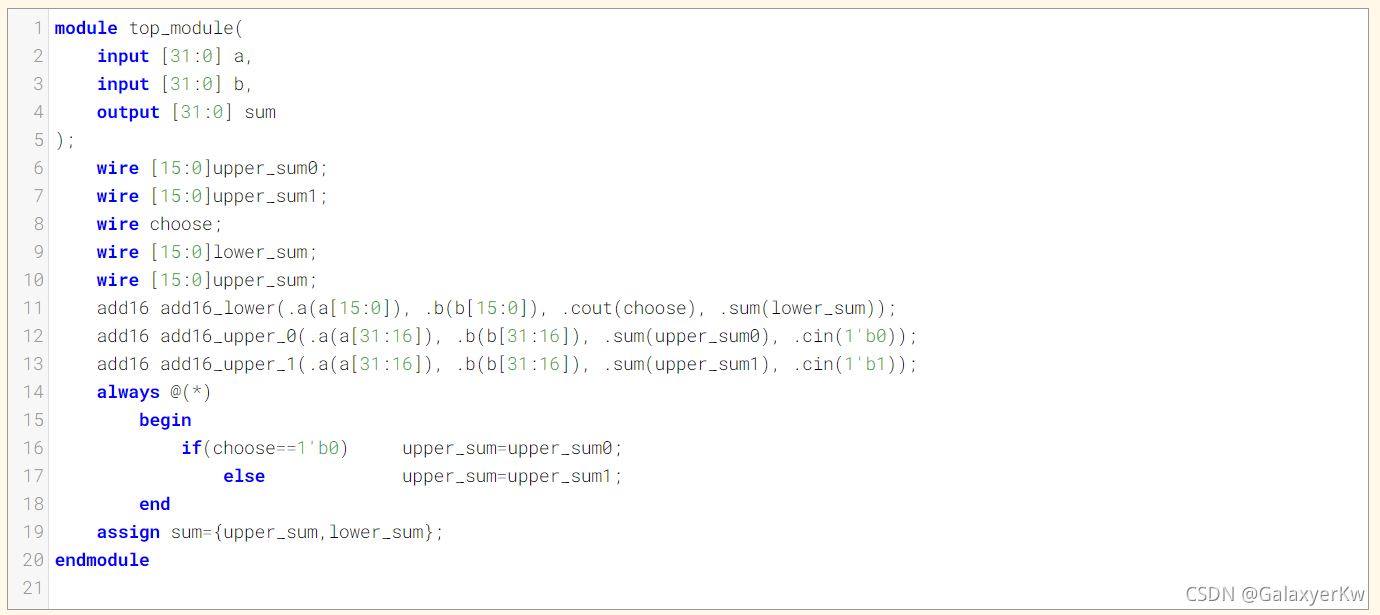

四.加法器优化

“低16位”加法器通过cout向“高16位”传输进位信号,这个过程延迟相当大,需要优化:

优化方法即:多复制一份”高16位“加法器,不过一个cin=1,另一个cin=0。通过“低16位”输出的进位信号控制一个“选择器”,选择其中一个“高16位”的运算结果,最后再进行整合。这样就避免了“高16位”和“低16位”加法器之间的信号传输,降低了延时。

规定名称如下:

顶层程序如下:

【练习地址链接:Module cseladd】

3242

3242

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?