1、使用背景

就是在企业做开发的时候啊,会遇见这样一种事情,就是说我这边写好的功能模块需要拿去给别的项目小组进行使用,那么这个时候你又不想让别人拿到你的源代码文件,怎么办呢;这个时候就可以选择将你的网表文件给到他使用,就是相当于把你的功能模块封装成了一个黑匣子一样,只有外部端口,没有内部代码;

2、实现流程

本次的功能流程是基于紫光同创FPGA在PDS软件开发环境之下进行实现的;

第一步:

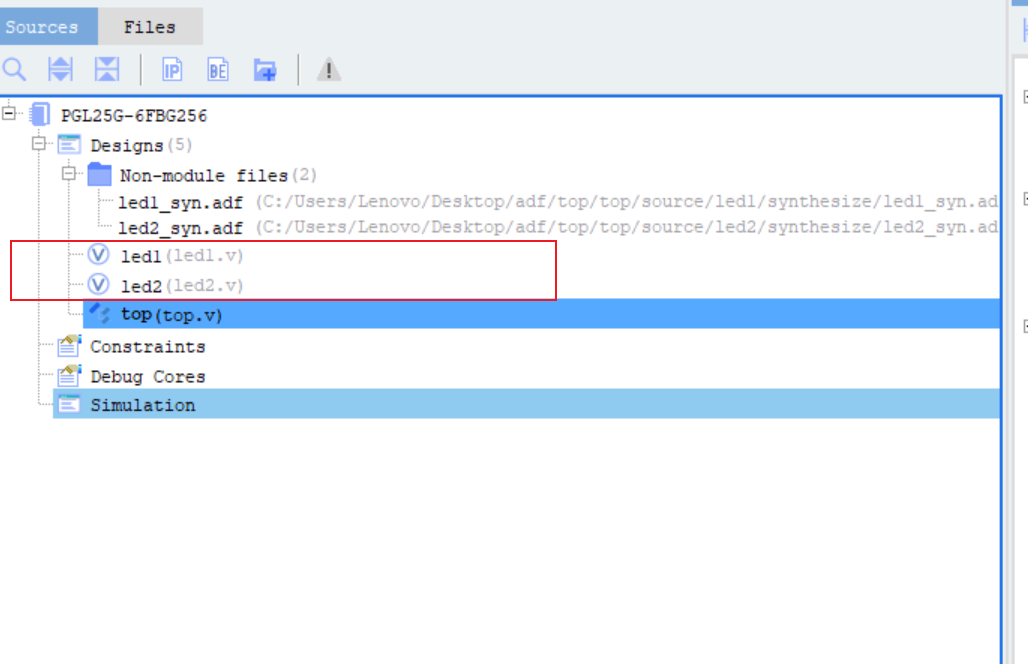

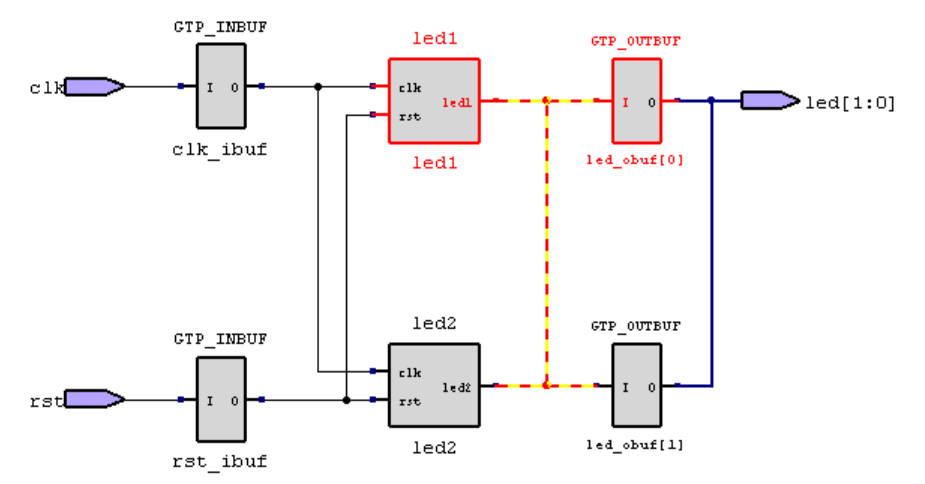

首先我们需要先建立3个项目工程,当然这里不一定需要三个啊,但是不能少于2个项目工程;一个子模块,一个顶层;我这里为了整个流程的清晰度,所以建立了3个项目(2个子模块、一个TOP层);如下图所示(就用LED做例子了哈哈哈) 第二步:生成加密网表

第二步:生成加密网表

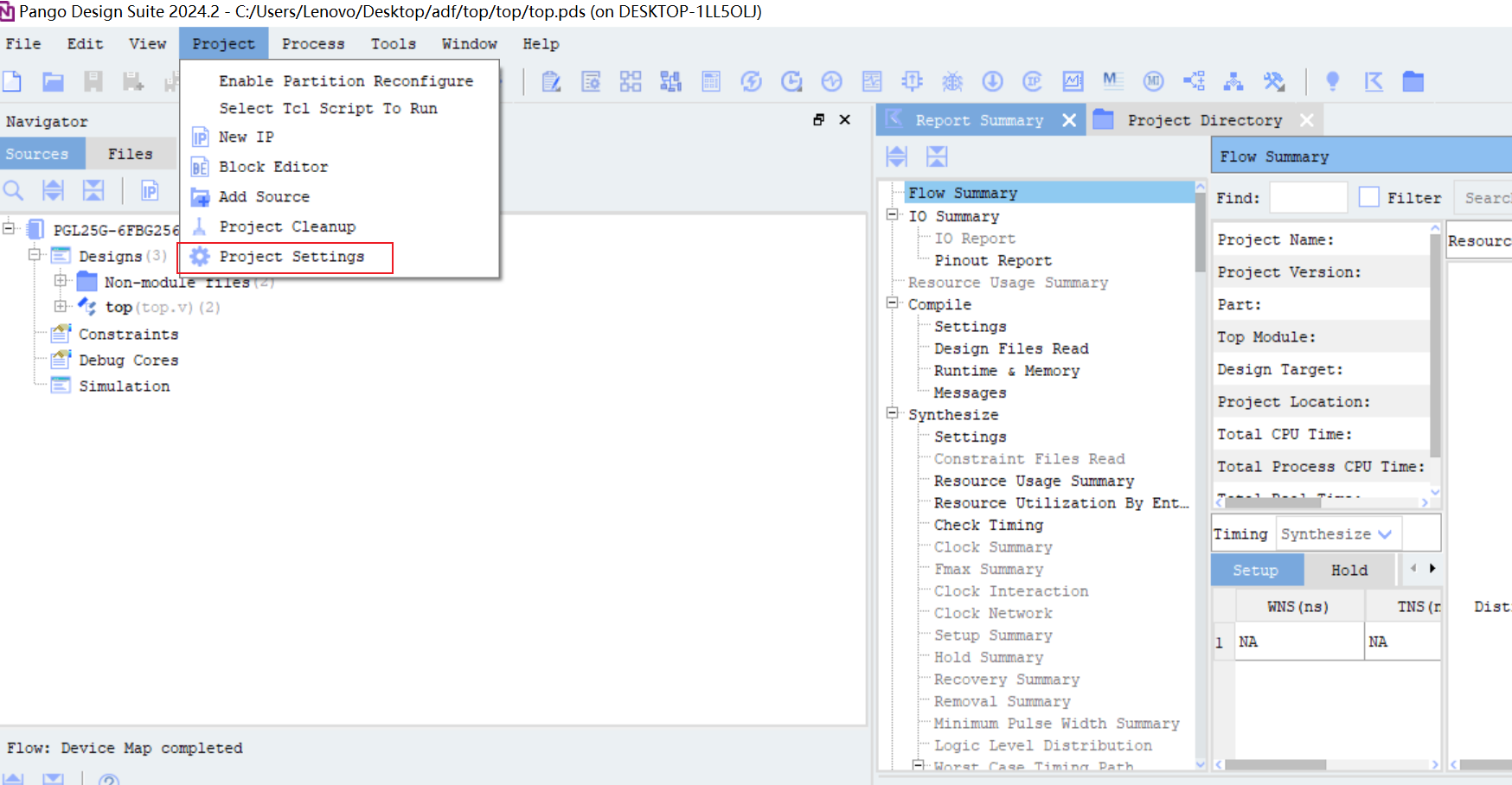

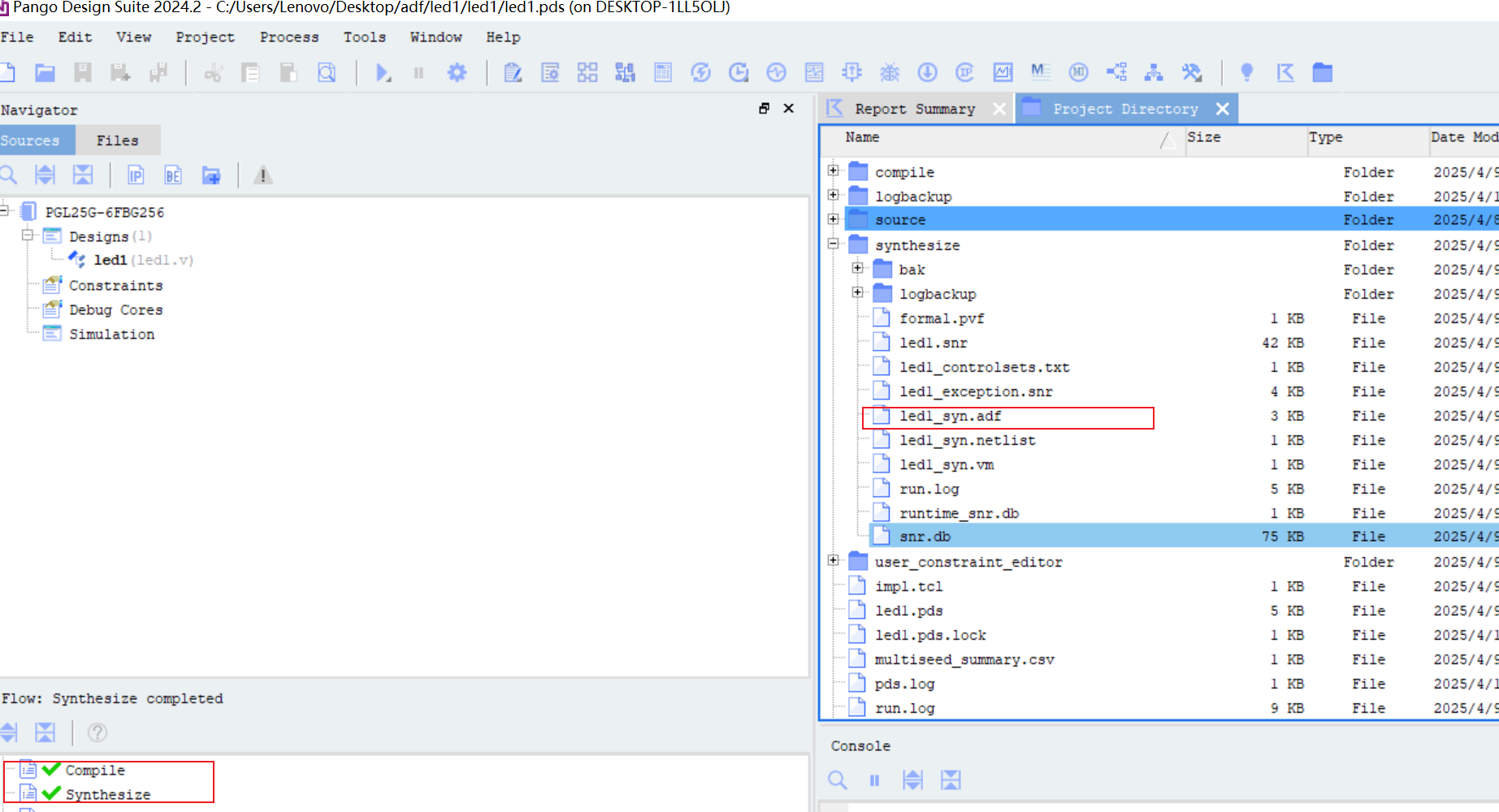

用PDS软件打开我们的LED1和LED2子模块,然后对软件进行相关设置;找到project——>project settings——>synthesize——>disable io insertion进行点击勾选;

注意这些设置是在子模块里面操作设置的,在top层就不需要这样子进行设置了;

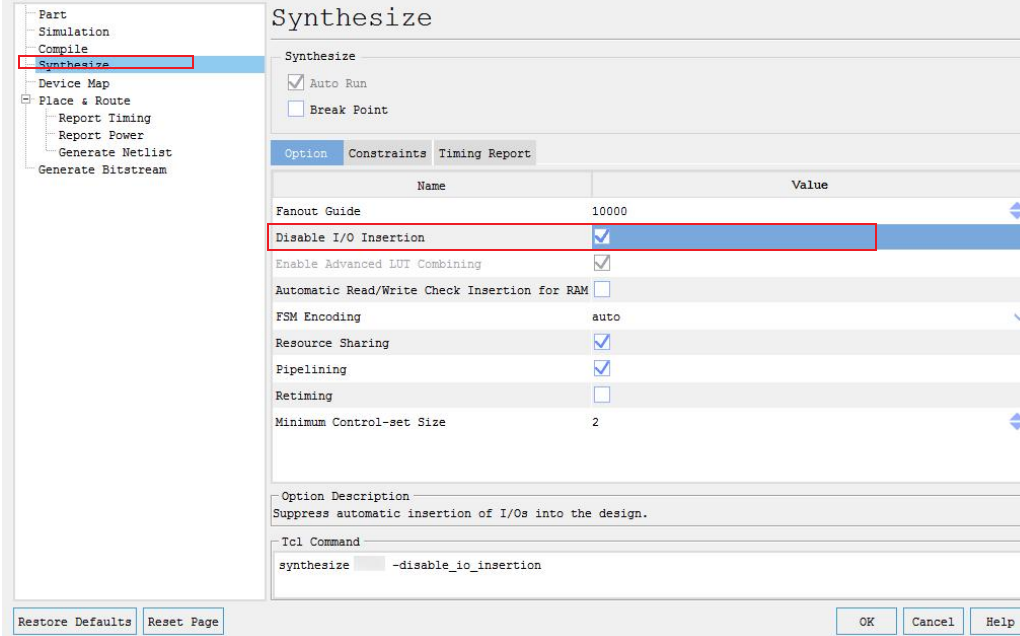

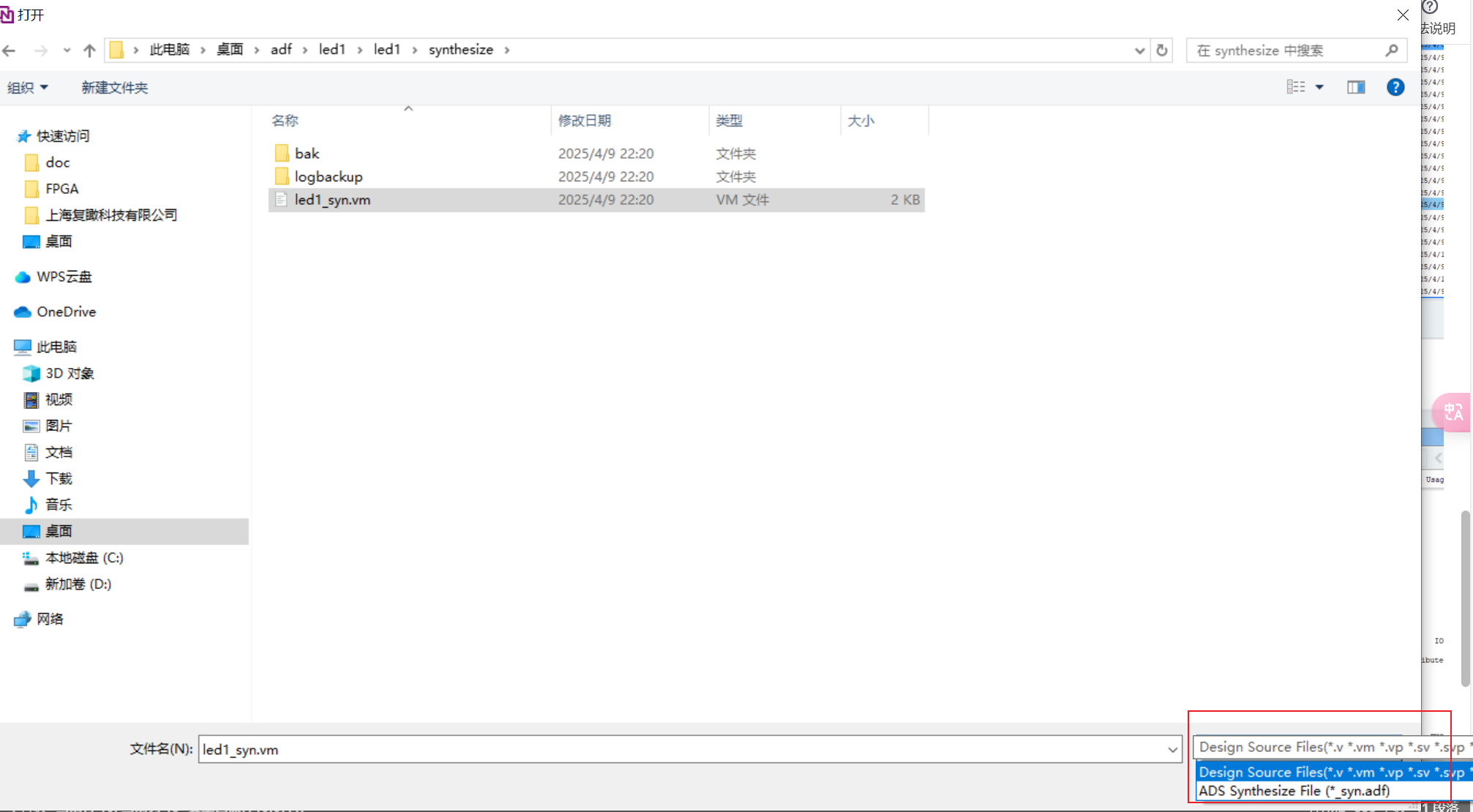

这些都设置完毕后呢,就可以对工程进行编译和综合了,综合完毕后会生成一个.adf的网表文件,我们要使用的就是这个文件;如下图所示:

第三步:如何使用这个.adf 网表文件

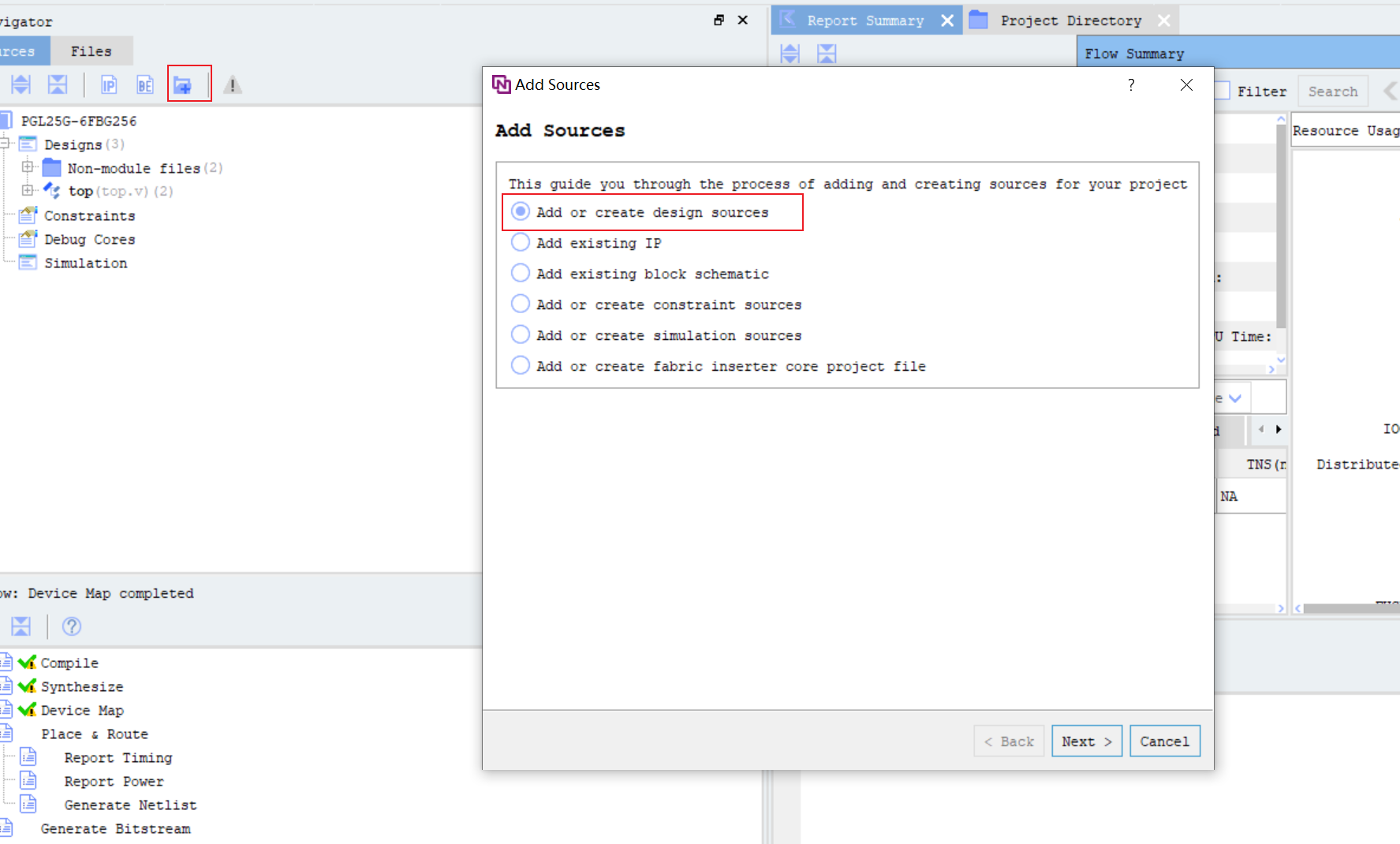

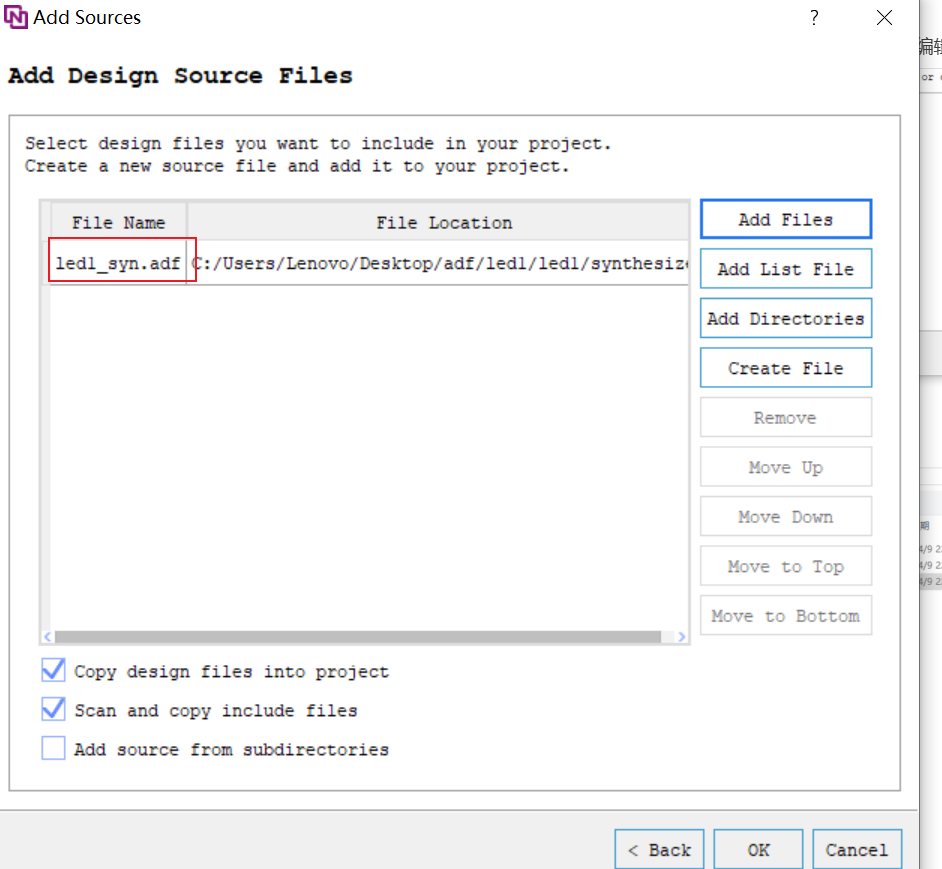

回到top 工程,我们对这个adf文件进行添加;下面就是添加adf 文件的流程;

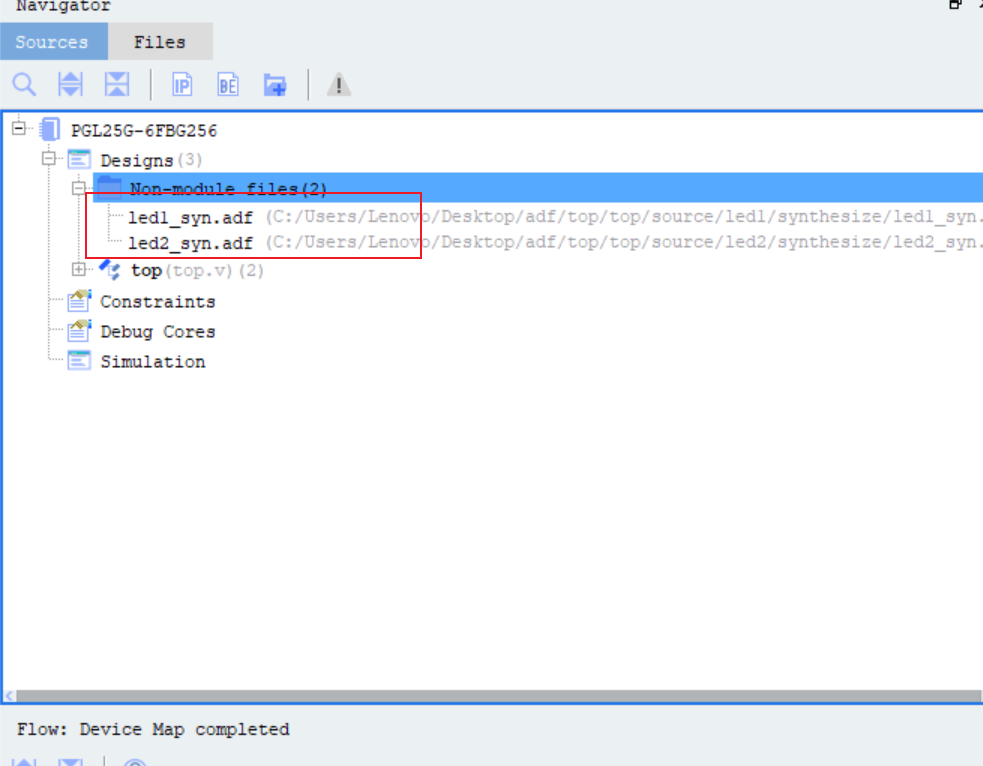

当文件添加好后如下图所示;我这里是把两个子模块的添加了哈;各位小伙伴儿在尝试的时候可以只弄一个子模块哈;

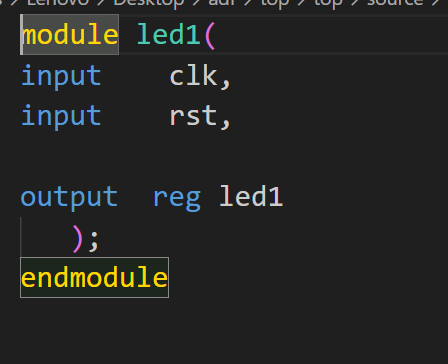

adf 文件添加完毕后,这边在软件里面手动创建一个端口声明(xilinx的是自动生成);如下图所示:

这里也是把端口声明给创建好了;

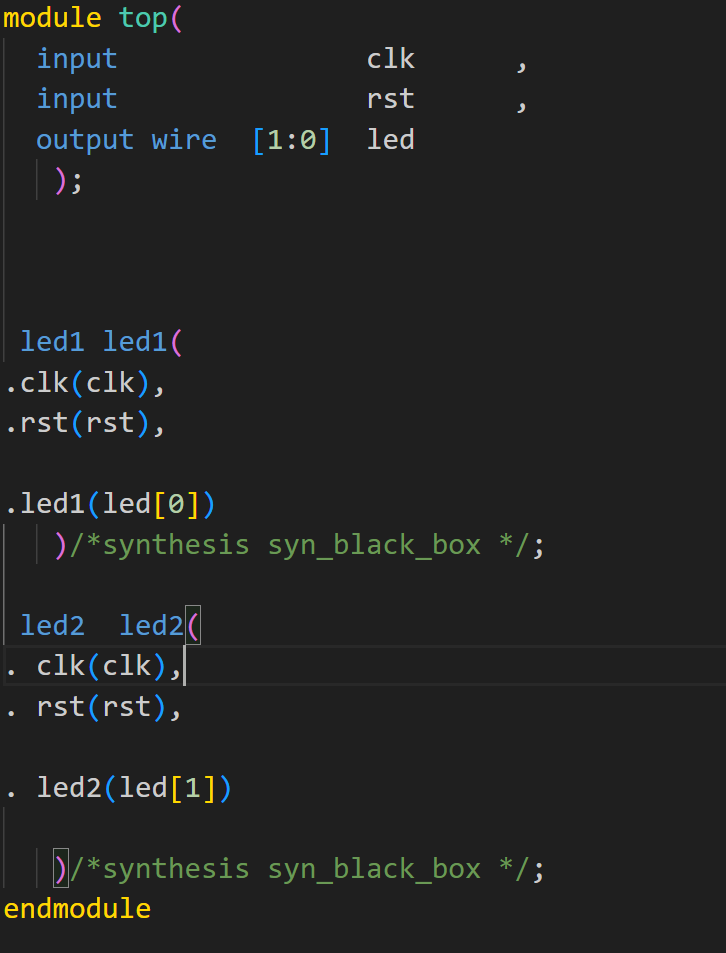

然后将创建好的端口例化进top 层进行连线,如下图所示:

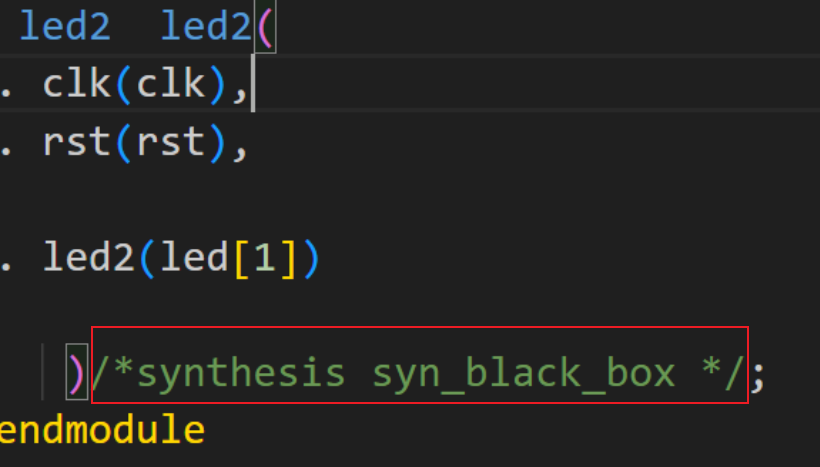

但是这里需要注意!!!,在TOP层的子模块声明里面需要加上/*synthesis syn_black_box */进行黑匣子设置,此时子层 adf 文件作为黑盒是不会综合的,在 device map 时会将顶层综合结果与子层 adf 文件合并传递至布局布线阶段;

至此adf 文件的使用流程以及完成,我们可以综合一下,然后看看综合后的视图;

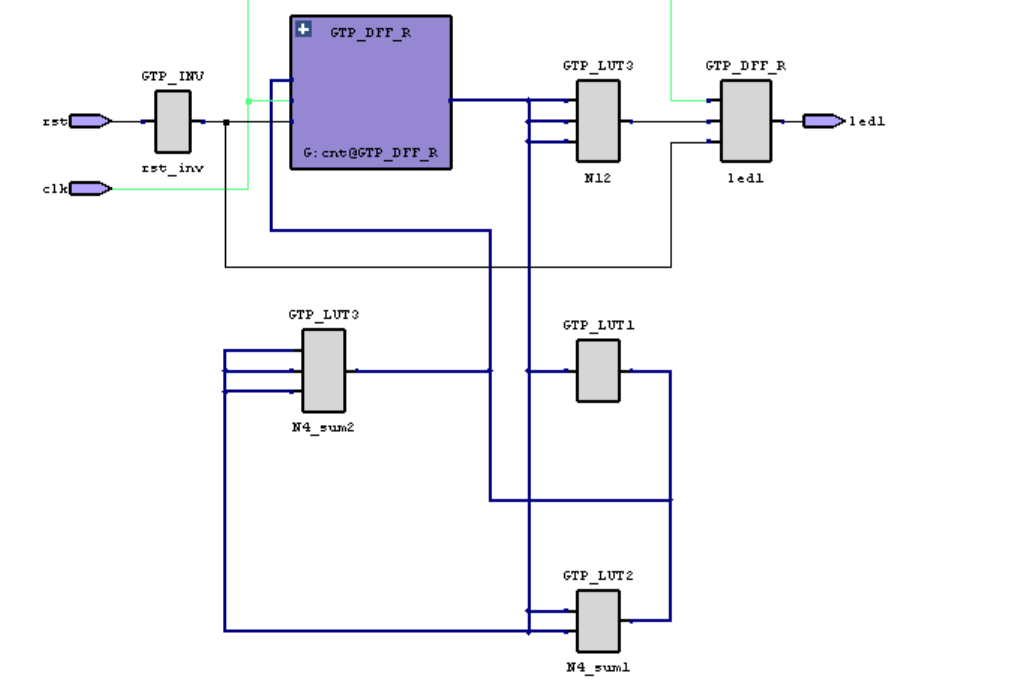

再看一下子模块的视图

对比看我们top 工程网表视图里面是无法看见子模块详细网表构成的;该模块已经被封装成了一个黑匣子。

好了这次的分析就到这里结束了呀,再见了呀哈哈哈。

3965

3965

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?