1 计算机概述

1.1 编译汇编

- 汇编和编译生成

- 编译(想到编译原理):生成汇编代码

- 汇编:生成机器码

- 编译和解释

- 编译->汇编代码->汇编->机器码->链接(库函数)->可执行文件

- 解释:边翻译为机器语言边执行,执行效率低

- 硬件和软件实现逻辑等价

- 系统软件:操作系统、数据库管理系统(数据库系统不是)、编译程序、网络软件

- 冯诺依曼架构:

- 包含(5叔叔空存储):输入、输出、控制、存储器、处理器

- 数据和指令一同存放,靠不同的执行周期进行区别

1.2 计算机性能指标

- 字长:

- 机器字长:处理器可以处理的最大字长,ALU运算位数

- 存储字长:一个主存单元的位数

- 指令字长:一条指令的位数

- 周期:

- 时钟周期:主频的倒数,最小的时间单位(带有时钟就是最小)

- 机器周期:一条指令有四个机器周期:取指、间址、执行、中断,通常选四个周期中最长的作为机器周期

- 指令周期:执行一条指令的时间。一般包含四个机器周期。

- 计算有关:

- 如果简单(只有两个数据),则直接计算,频率理解为一秒发生了多少次。

- 如果数据较多,根据单位进行计算

- 主频xxHz: 单位:C/S

- CPI:每秒执行的指令数,单位C/I

- 时钟周期:单位C

- 主频和时钟周期转化 主频 = 1 时钟周期 主频=\frac{1}{时钟周期} 主频=时钟周期1

- 运算速度:

- MIPS:每秒执行百万条指令

- MFLOP(6), GFLOP(9), TFLOP(12), PFLOP(15). E(18), Z(21)(买高铁票而坐,每个差3)

- 单位是每秒执行的浮点运算=执行的浮点操作次数/时间

- 效率提升: 提升部分比例 提升比例 + ( 1 − 提升部分比例 ) \frac{提升部分比例}{提升比例}+(1-提升部分比例) 提升比例提升部分比例+(1−提升部分比例)

2 数据运算

常识

- 对于1111…11一共n个1,值为 2 n − 1 2^n-1 2n−1

- 对于n位数,可以表示的不同组合为00…000-1111…111,一共 2 n 2^n 2n个

- 对于有符号16进制数,如果第一位大于等于8是负数,小于8是正数

2.1 数据表示概念

- 0表示不唯一:

- 源码:符号位+绝对值

- 反码:正数不变,负数全部取反,

- 0 表示唯一:

- 补码:正数不变,负数取反+1

- 移码:加上了一个偏移量,使得负数变为正

加上偏移量: 2 n − 1 2^{n-1} 2n−1,则先算补码,然后最高位取反

注意如果偏移量不是 2 n − 1 2^{n-1} 2n−1,则没有这个性质,比如IEEE754浮点数偏移127

2.2 数字计算

-

比大小

- 先比符号位(先比正负)

- 符号位相同,则后面n-1位谁大就是谁大

-

整数移位

- 算数左移: 符号位不动,其他位动,右边补0。

- 算数右移:

- 补码:左边添加符号位

- 源码:符号位不动,左边添加0

- 逻辑移位:直接补0即可

-

减法

- 用补码计算: X − Y = X + ( Y ˉ + 1 ) X-Y=X+(\bar Y+1) X−Y=X+(Yˉ+1)

-

乘法

- 用移位和加法实现(如果是无符号乘法可能遇到减法,但是减法也可以用加法计算)

- Booth算法(补码一位乘法):

- 第一次在右边添加0,

- 如果是10则减去乘数

- 如果是01则加上乘数

- 如果是00或者11则不做,最后移位

- 原码一位乘法:符号位单独判定,真值按照无符号数计算

-

除法

- 减法和移位(如果够减则商1,如果不够减则商0)

-

双符号位(模4补码)

- 第一位表示结果的正负,第二位表示是否溢出

- 更容易发现加减法溢出

- 运算时使用双符号位,存储时只需要1位(因为未溢出的数两位总是相同)

- 移位时低符号位也参与移位

-

溢出判定

- 移位:只有左移可能溢出,移出位和符号位不同溢出, x 0 , x 1 x 2 . . . , x 0 ≠ x 1 x_0,x_1x_2..., x_0\neq x_1 x0,x1x2...,x0=x1

- 加减法:

- 单符号位:四种情况,看运算结果和原来操作数是否相同。正+正,正-负,负+负,负-正

- 双符号位:符号位如果不同(01或者10)则溢出

- 双进位:如果符号位进位和数值进位不同则溢出

- 乘法:高32位全0或者全1不溢出,否则溢出

- 浮点数运算:左归下溢,右归上溢(记忆方法:右上)注意左归下溢作为0,右归上溢出现异常

2.3 状态位

- OF:溢出(只对符号数有意义)

- SF:运算结果第一位,

- ZF:是否为0,

- CF:是否进位/借位(只对无符号数有意义)

2.4 大小端存储

地址从0开始,大端正序,小端逆序,对于0x00ABCDEF

| 地址 | 0 | 1 | 2 | 3 |

|---|---|---|---|---|

| 大端 | 00 | AB | CD | EF |

| 小端 | EF | CD | AB | 00 |

2.5 边界对齐

只发生在 小类型+大类型时候

长度为x,则起始地址一定为x的倍数

2.6 符号数和非符号数转化

绝对值之和是65536,记住绝对值最后2位相加是6

2.7 IEEE754浮点数

- 符号位(1)+阶码(8)+尾数(23)

- 阶码:

- 计算:对于给定一个2进制数,去掉最高位的1,然后+1

- 范围:1~254

- 浮点数求和:先对阶(小阶码变大)再相加

- 浮点数溢出:右归上溢(出现异常),左归下溢(当作0)

- 特殊负号:

- 无穷:阶码全1,尾数全0:正无穷(7F000000) 负无穷(FF000000)

- 0:阶码和尾数全部为0:+0: (000000),-0: (800000000)

- 规格化

- 补码:小数点后一位和符号位不同

- 原码

- 基数为2:小数点后最高位为1

- 基数为4:小数点最高2位不为00

3 存储系统

3.1 存储分类

-

RAM和ROM区别:

- RAM易失性存储,掉电后数据消失

- ROM非易失性存储,掉电后数据保存

-

SRAM和DRAM区别:

SRAM DRAM 实现方式 二极管(触发器) 电容 价格 高 低 存储密度 小 大 刷新 不需要刷新 需要动态刷新 用处 cache和TLB 主存 -

其他存储器:

- SAM:顺序存取,磁带

- DAM:直接存取,磁盘、光盘

- ROM:SROM, DROM, EPROM(可多次写入)

3.1 DRAM

- 刷新:由于使用电容,每读一次需要刷新(死时间),不允许读写

- 刷新方式

- 集中刷新:每隔一段时间后刷新一次

- 分散刷新:前半周期读,后半周期刷新,不存在死时间

- 异步刷新

- 刷新按照行,因此减小刷新的负担=> 减少行数

- 刷新方式

3.2 四体低位交叉存储

- 每个体由独立的控制电路、地址寄存器、数据寄存器

- 低地址为体号

- 数据连续存放在相邻体内

- 存取周期为T, 传输周期为r,体数(模块数)>= T/r

- 总线宽度=一个体数(默认)

- 计算数据带宽:每个体为32位,则

- 存储周期平均分给每个体,这是理想的情况

- 传输时间=存取周期/体数,带宽=4B/传输时间

- 计算具体传输时间:如果是按顺序访问4个体,且总线一次只能传输一个体

- t=T+(m-1)r,r是传输时间,m是体数,T是存取周期,而顺序存储为mT

- 传输时间如果没给,则按照T/r计算

- 计算访问冲突次数

- 有可能和传输时间一起考

- 对于m体交叉存储,对同一个体的访问必须隔m次,否则需要等待

- 计算数据带宽:每个体为32位,则

- 总线宽度=四个体总宽度

- 一个存储周期可以获得4*每个体的宽度 的数据

- 但是只能顺序访问0,1,2,3,如果访问序列为2,3,0,1需要分为两个周期,每个周期访问2,3和0,1

3.3 ROM芯片引脚计算

- 如果是X*Y位的芯片:

- 数据线根数:Y

- 地址线根数:log2X

- 控制线根数:1或者2(读+写信号可以2根可以1根)

- 采用地址复用技术:

- 地址线/2,额外增加2根控制线

- 控制共4根

- DROM必须采用地址复用技术!

3.4 片内最小地址

地址结构:

- 交叉编址:片号在低位

- 顺序编址:片号在高位

| 编址方式 | ||

|---|---|---|

| 交叉编址 | 片内地址 | 片地址 |

| 顺序编址 | 片地址 | 片内地址 |

-

正常情况下计算的是一行的最小地址:

- 看编址方式,顺序还是交叉

- 根据字扩展结果,写地址线位数,圈出片号部分

- 将除了片号的部分全部取0或者取1可以得到最小地址

-

对于顺序编址,如果发生了字扩展,那么字扩展芯片地址在片内地址最后几位

3.5 芯片扩展

- 字扩展:扩展地址线

- 位扩展:扩展数据线,片地址在高位

3.6 虚拟存储

-

虚拟存储分类:

- 页式

- 段式:内存分段,与程序段相互对应,易于编译管理,和多道程序一起使用

- 段页式:内存分段,段内分页,按段实现共享和保护,需要访问两次内存

-

页面大小:

- 页面太大:导致缺页严重

- 页面太小,导致页表过大

-

TLB和page

- TLB放在cache中,使用全相连

- 页表放在主存中,使用替换算法

-

TLB和cache

- TLB和cache都使用SRAM实现,均由硬件实现,对程序员透明

- page由操作系统实现

- TLB的地址:无offset,TLB的数据块:存放了物理页号

-

访存过程:TLB->page(主存)->cache->主存->修改cache

3.7 Flash和SSD和磁盘

- Flash:

- 写入前先擦除,写比读慢

- SSD:

- 由flash芯片构成,

- 易磨损,需要使用磨损算法(总是选择读写次数最小的写入)

- 擦除单位:页

- 磁盘:

- 读写单位:块/扇区

- 传输速率:转速*磁道数据量

- 磁盘周期:传输时长+延迟+寻道时间

- 传输时长=数据/传输速率

- 延迟:旋转半周的时间

3.8 cache

-

替换策略

- write hit

- wirte back: 硬件需要增加dirty位

- write through:常和write buffer一起使用

- write miss

- write allocate

- not write allocate

- write hit

-

计算题

- 首先画出cache地址结构(tio)和块结构,边读题边填入长度:

tag index offset - - - D V R tag data - - - - - - 要小心index是组号,就是行数/组数

- 题目中说了替换算法或者write back等,提示ref位和dirty位

- 主存块默认是cache块大小

-

缺失计算:

- 如果是缺失率,则不用管循环次数

- 看一个cache块装入了几个Int,说明后面几次不会失配

- 看语句的访存次数,a[i]+=1访存两次,sum+=a[i]访存一次

3.9 LRU替换算法

- 模拟时使用:向前寻找访问过的序列,决定不替换它的方法

- 计算计数时:

- 对于每组4个块,需要2位,每组8个块需要3位

- 如果访问过或者替换的,则放到队头,其他下标跟着边

- 下标就是访问次数,或者是引用位

访问2:0123 => 2013 => 替换4 => 4201

4 指令

4.1 扩展操作码指令

假设地址结构为:

| op | 地址1 | 地址2 | 地址3 |

|---|---|---|---|

| 6 | 5 | 5 | 5 |

- 三地址码x条,二地址码y条,一地址码z条:

- x最多:26条

- y最多:(26-x)*25

- z最多:((26-x)*25-y)*25

- 指令总长必须是字节的整数倍

4.2 寻址

- 立即数寻址->直接寻址->间接寻址

- 寄存器寻址->寄存器间接寻址

- 相对寻址(pc+2+offset)

看清题目问的是值还是有效地址

4.3 RISC和CISC

RISC

- 必须使用流水线

- 指令条数少,指令长度短,指令格式和寻址模式少

- 只有load和store指令访存

- 通用寄存器多

- 硬布线,不使用微程序控制器

- 大多数指令在一个周期内完成

4.4 流水线

- 适合流水线的条件:

- 指令规整

- 指令和数据对齐存放

- 只有load和store指令访存

- 流水线五个周期:取指、移码、执行、访存、写回

- 流水线冲突

- 结构冒险:取指和访存冲突,解决方法:数据cache和指令cache分离

- 数据冒险:RAW, WAR, WAW 解决方法:旁路技术or插入nop指令or流水线停顿

- 控制冒险:条件转移指令,进行分支预测

- 高级流水线技术

- 超标量技术:发射多条指令,使得CPI<1

- 超长指令:将多条指令合并成一条超长指令字

- 超流水线:划分多段流水线,提高主频

- 计算流水线时间:第一条指令完成流水线+n-1条指令流过一个流水级

- 无旁路的5级流水:

- 只有RAW冲突

- 每隔两条指令才不冲突

4.5 位数计算

- MAR:主存地址空间位数/总地址线条数

- MDR:数据线条数

- PC:主存空间地址位数

- IR:指令长度

4.6 指令执行周期

- 取指、间址、执行、中断(只有响应中断请求时才进入)

- PC修改次数问题

- 取指时一定修改PC,

- 如果是跳转指令,则再次修改PC

4.7 微操作

4.8 内存计算

- 内存偏移:直接加减偏移量

- 内存长度:大-小+1

4.9 控制信号

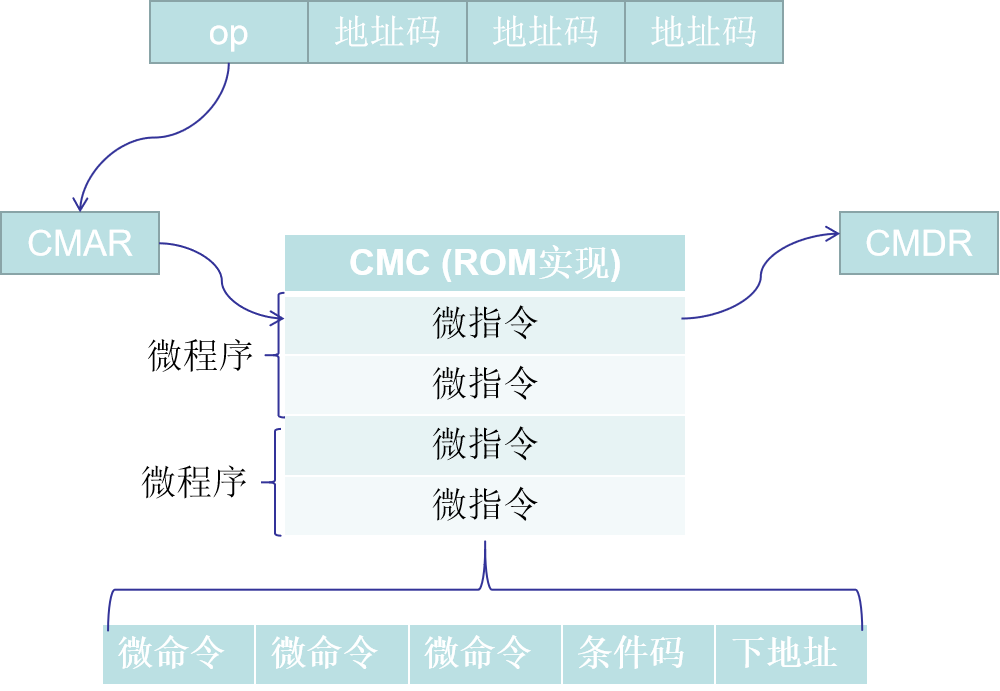

- 微程序控制器:

- 微指令:存放在MC中,包含了多个微命令

- 微命令:由一位或者几位组成,执行过程就是微操作

- 微操作:最小的操作,表示寄存器赋值等

- 微程序:一段微程序对应一条指令

- 指令的op是微程序的入口地址,CMAR是微指令地址,CMDR是微指令取指结果

- 微指令取指:op->CMAR->CM->CMDR

- 下一条微指令地址由微指令的下地址段确定

- 一个op就对应一个微程序

- 硬布线

由组合逻辑直接产生控制信号

4.10 微指令编码

- 水平型:

- 直接编码:微指令每位代表一个微命令

- 字段直接编码:

- 微指令分为若干段,每段m位,可以表示2n-1-1条微命令,

- 因为每个段需要一条微指令表示不进行任何操作

- 垂直型:

- 设置op,只能定义一种操作

- 微指令较短,但是微程序较长

5 异常处理

5.1 异常分类

- 异常

- 程序性异常

- 故障(缺页,除0)

- 自陷(trap指令)

- 终止(硬件故障)

- 程序性异常

- 中断

- 可屏蔽

- 不可屏蔽

5.2 中断和异常区别

| 中断 | 异常 | |

|---|---|---|

| 响应时间 | 指令周期结束时检测 | 在指令执行过程中出现 |

| 返回时 | 执行下一条指令 | 可能重新执行该指令(缺页异常) |

5.3 中断流程

- 中断请求:中断源发送中断请求

- 中断判优

- 使用排队电路和中断请求标记寄存器实现

- 常见的顺序

- 硬件>软件

- 非屏蔽>可屏蔽

- 高速>低速,DMA>IO

- 输入>输出

- 实时>非实时

- 访管指令>程序指令

- 重启最低

- 是否关中断:关中断后只能响应非屏蔽中断

- 中断隐指令(硬件完成):

- 关中断

- 保存断点(保存PC)

- 形成中断服务程序入口地址送PC(引出终端服务程序入口)

- 中断服务程序

- 保护现场

- 执行中断服务

- 恢复现场

- 开中断

- 中断返回

- 如果是可嵌套中断,则在中断服务之前开中断,在中断服务之后关中断

- 中断向量:中断服务程序的入口地址

- 中断向量地址:中断服务程序地址的地址

5.4 多重中断

- 单重中断:中断处理时不响应新的中断

- 多重中断

- 在中断服务前关中断,在中断服务之后开中断

- 屏蔽字:

- 如果屏蔽该中断,则该位为1。中断处理时必须屏蔽同类型中断

- 1越多,则中断优先级越高

- 和排队电路比较

- 排队电路改变了中断响应的优先级

- 中断屏蔽字改变了中断服务程序的优先级

5.5 常见的异常和中断

- cache不发生异常

- 浮点数上溢发生异常,浮点数下溢作为0处理,不发生异常

- 用户输入输出:访管中断

5.6 CPU响应中断条件

- 中断源发出中断请求且未被屏蔽

- CPU允许中断(处于开中断状态)

- CPU指令周期结束

6 总线

6.1 概念

- 总线:就是几根信号线,同一个时刻只允许一个主设备写,多个从设备读

- 突发传送:传送一个地址以后传送多个值

6.2 总线分类:

-

串行:数据一次只能发1bit,但是工作频率很高,可以使用数据包

-

并行:同时发送多bit数据(各总线存在干扰,工作效率不高)

-

串行总线:USB、RS323C、PCIE、SATA(you are ps)

6.3 总线分类1

- 数据总线:控制字,状态字,命令字,数据等等

- 控制总线:读/写控制信号,中断信号,时钟信号

- 地址总线:地址

6.4 总线分类2

- 片内总线:连接ALU,寄存器等各个片内部件

- 系统总线:连接CPU和主存,外部设备等

- 单总线

- 双总线(主存总线,IO总线)

- 三总线(主存总线。IO总线,DMA总线)

- IO总线

- 设备总线:连接低速设备

- 局部总线:连接高速设备

- 通信总线:连接不同计算机(网线)

6.5 总线分类3

- 同步总线

- 采用时钟信号(CPU时钟信号或者控制信号)

- 传送速度快,可靠性差

- 不同速度设备也可以实现(选速度慢的)

- 异步总线

类型 请求信号撤销 回复信号撤销 不互锁 自动撤销 自动撤销 半互锁 等待回复后撤销 自动撤销 全互锁 等待回复后撤销 请求信号撤销后撤销 - 按需分配时间

- 握手信号定时

- 半同步

- 增加一个wait信号,主设备请求后等待从设备准备数据

- 各部件存取时间接近

- 不需要应答,总线长度短

- 分离式通信

- 主设备:请求总线->发送地址->放弃总线

- 从设备:收到请求->准备数据->请求总线->发送数据

- 提高了总线的利用率(准备数据时不占用总线)

7 IO接口

7.1 IO接口组成

- 组成

- 数据寄存器:CPU读写数据

- 控制和状态寄存器:

- 写命令字,读取状态字,中断类型号

- 由于控制寄存器和状态寄存器使用时间错开,所以合二为一

- 地址线:指明端口

- 控制线:读写信号、中断请求信号、握手信号、时钟信号

- 寄存器又称为端口

- 一个IO接口可以连接多个设备,分辨:通过多组寄存器 or 在地址中指令

7.2 IO控制方式

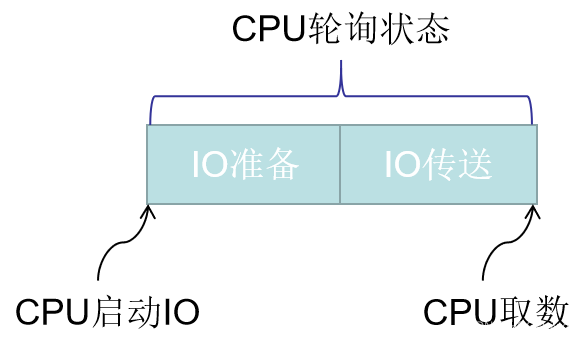

- 程序查询:

- 独占查询:100%占用

- 定时查询:每隔一段时间查询一次

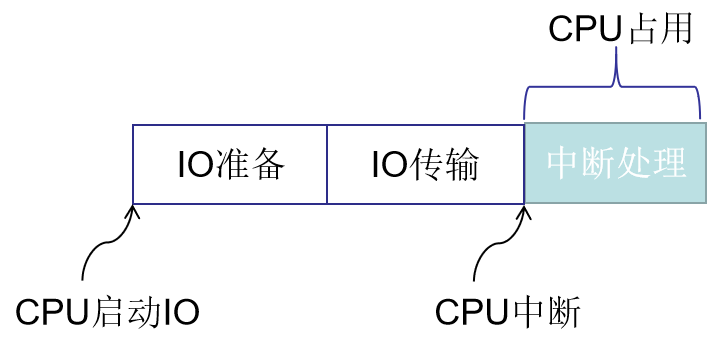

- 程序中断:CPU启动IO->IO传输完成->发出中断请求->CPU中断处理

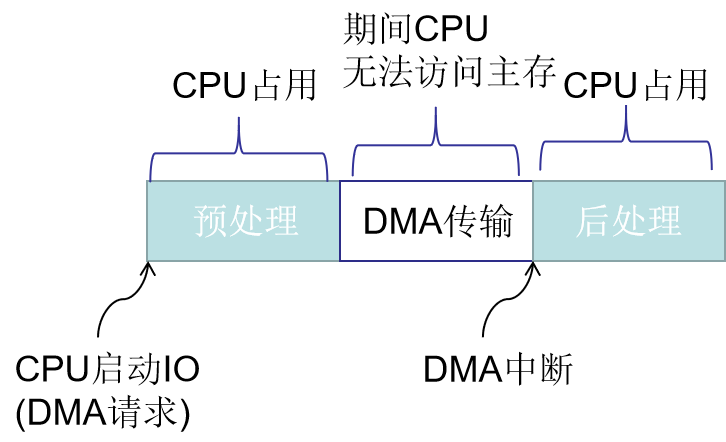

- DMA方式

- CPU启动IO->向DMA发送信息->DAM传输完成->发出中断->CPU处理

- 周期窃取:当CPU和DMA同时发送请求时,优先响应DMA请求

- 如果DMA访问时,总线被CPU占用,则等待CPU完成

- DMA响应时间:每个机器周期后、每个存取周期后、总线事务完成后

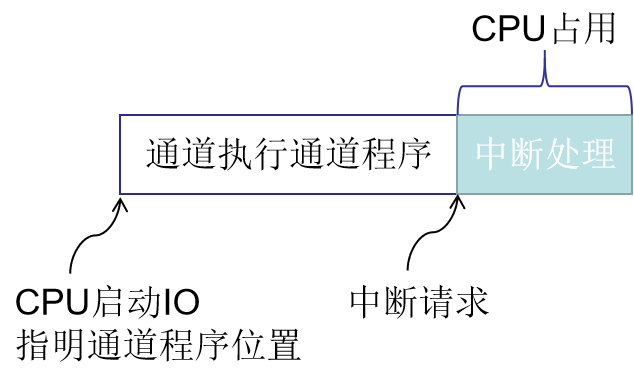

- 通道方式

- IO控制方式比较:

- DMA方式中中断的目的:报告传输完成

- DMA请求的目的:外设请求数据传输(只有有DMA控制器的外设才可以发出DMA请求)

- 程序中断传输方式中中断的目的:请求CPU处理时间

7.3 IO软件

- IO指令

- 分为操作码,命令码,设备码

- 属于CPU指令,特权指令,比如8086:IN rd, rs和 OUT rd, rs

- 通道指令

- 通道识别指令

- 编制好放入内存中

7.4 显存计算

- 显存大小:分辨率*颜色位数(一帧大小)

- 显存带宽:分别率*颜色位数*频率

7.5 字符显示

- 在VROM中存放ascii码

- 在ROM中得到字形码

- 每个字按照一个16*16的点阵进行存储(32B)

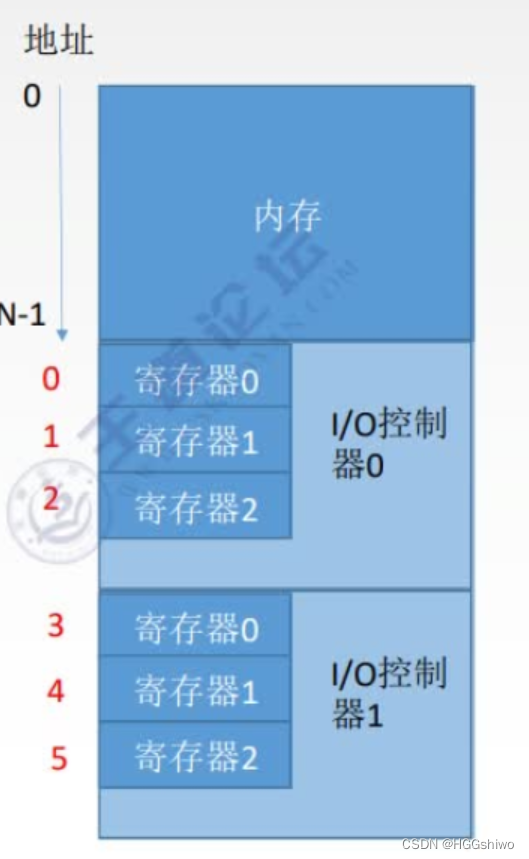

7.6 IO编址

- 统一编址:通过不同的地址码区分内存和设备

- 访存类指令可以访问IO端口

- RISC常用

- 也叫做存储器映射

- 独立编址

- 靠不同的指令区分内存和IO设备

- 只能用IO指令访问IO设备

7.7 DMA大题

- 如果问每秒需要占用CPU多少时间,每秒查询多少次等:

- 按1s传输多少数据计算,1s中断多少次

- (DMA中断单位是DMA传输块长,程序中断单位是内存块大小)

- 否则:

- DMA:画图,按一个周期计算(分为预处理+传输时间+后处理,传输时间不占用CPU)。传输时间按照DMA大小/设备速率计算

- 程序查询次数:按照设备1s传输多少数据,得到寄存器1s被填满几次,就是查询速率

1305

1305

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?