AG32最新发布——极简架构的光端机参考设计

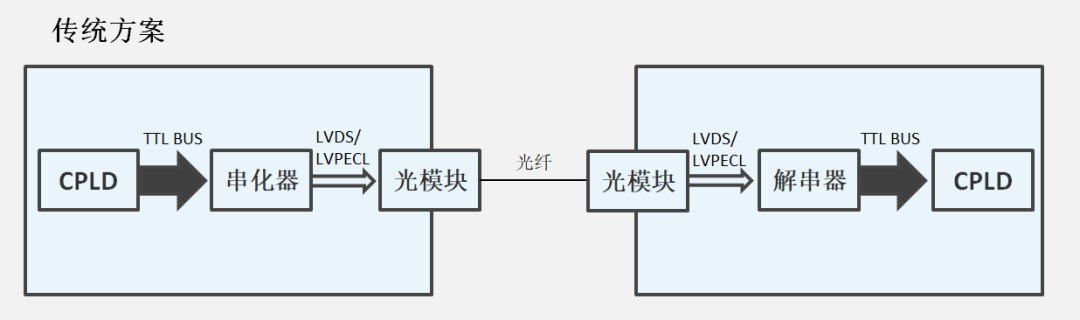

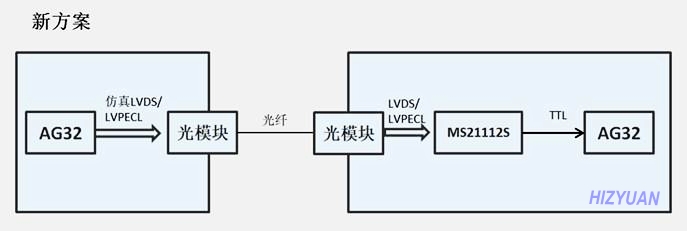

一、新方案与传统方案的对比

传统光端机方案中,采用CPLD+串化器+解串器等外围电路实现信号处理是常见选择。

现在我们推出全新替代方案——只需AG32(内置2k CPLD 的MCU) + MS21112S(差分接收芯片),差分发送用电阻网络,即可完美实现光模块150M稳定收发。

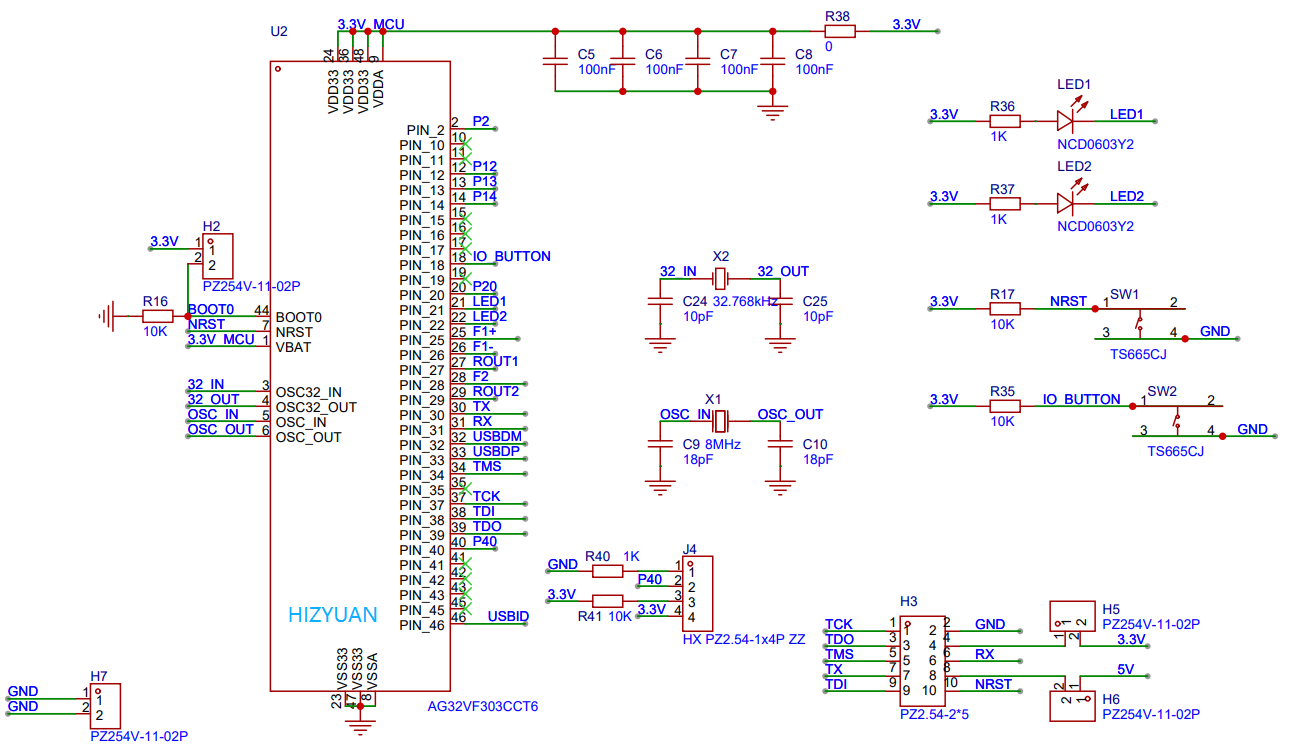

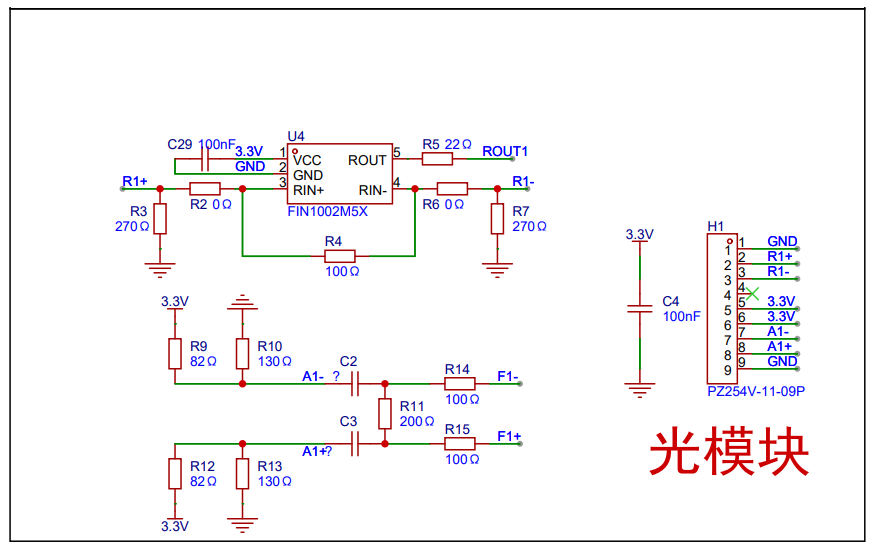

二、硬件参考设计

三、代码参考设计

以下分享部分参考设计代码,如需要了解更多设计内容,欢迎联系我们。

tech#hizyuan.com (发邮- 件请用 @ 替代 # )

- AHB通信的模块参考代码

//------hizyuan 2025.9 -------------------

module ahb2reg #(parameter READ_WAIT = 0)(

input ahb_clock,

input ahb_resetn,

input [1:0] ahb_htrans,

input ahb_hready,

input ahb_hwrite,

input [31:0] ahb_haddr,

input [2:0] ahb_hsize,

input [2:0] ahb_hburst,

input [31:0] ahb_hwdata,

output reg ahb_hreadyout,

output ahb_hresp,

output reg [31:0] ahb_hrdata,

output [31:0] reg_addr,

output reg_write,

output [31:0] reg_wrdata,

output reg_read,

input [31:0] reg_rddata

);

assign ahb_hresp = 1'b0;

reg [31:0] haddr_reg;

reg hwrite_reg;

reg ahb_data_phase;

reg [$clog2(READ_WAIT+1)-1:0] read_counter;

wire ahb_sel = ahb_htrans[1] && ahb_hreadyout;

wire ahb_write = ahb_data_phase && !ahb_hreadyout && hwrite_reg;

wire ahb_read = ahb_data_phase && !ahb_hreadyout && !hwrite_reg && read_counter == 0;

always @(posedge ahb_clock or negedge ahb_resetn) begin

if (!ahb_resetn) begin

haddr_reg <= 32'h0;

hwrite_reg <= 1'b0;

end else if (ahb_sel) begin

haddr_reg <= ahb_haddr;

hwrite_reg <= ahb_hwrite;

end

end

always @(posedge ahb_clock or negedge ahb_resetn) begin

if (!ahb_resetn) begin

ahb_data_phase <= 1'b0;

end else if (ahb_hreadyout) begin

ahb_data_phase <= ahb_htrans[1];

end

end

always @(posedge ahb_clock or negedge ahb_resetn) begin

if (!ahb_resetn) begin

ahb_hreadyout <= 1'b1;

end else if (ahb_sel) begin

ahb_hreadyout <= 1'b0;

end else if (!ahb_read || read_counter == READ_WAIT)begin

ahb_hreadyout <= 1'b1;

end

end

always @(posedge ahb_clock or negedge ahb_resetn) begin

if (!ahb_resetn) begin

read_counter <= 0;

end else if (!ahb_read) begin

read_counter <= 0;

end else begin

read_counter <= read_counter + 1;

end

end

always @ (posedge ahb_clock or negedge ahb_resetn) begin

if (!ahb_resetn) begin

ahb_hrdata <= 32'h0;

end else if (ahb_read || read_counter > 0) begin

ahb_hrdata <= reg_rddata;

end

end

assign reg_addr = haddr_reg;

assign reg_write = ahb_write;

assign reg_wrdata = ahb_hwdata;

assign reg_read = ahb_read;

endmodule

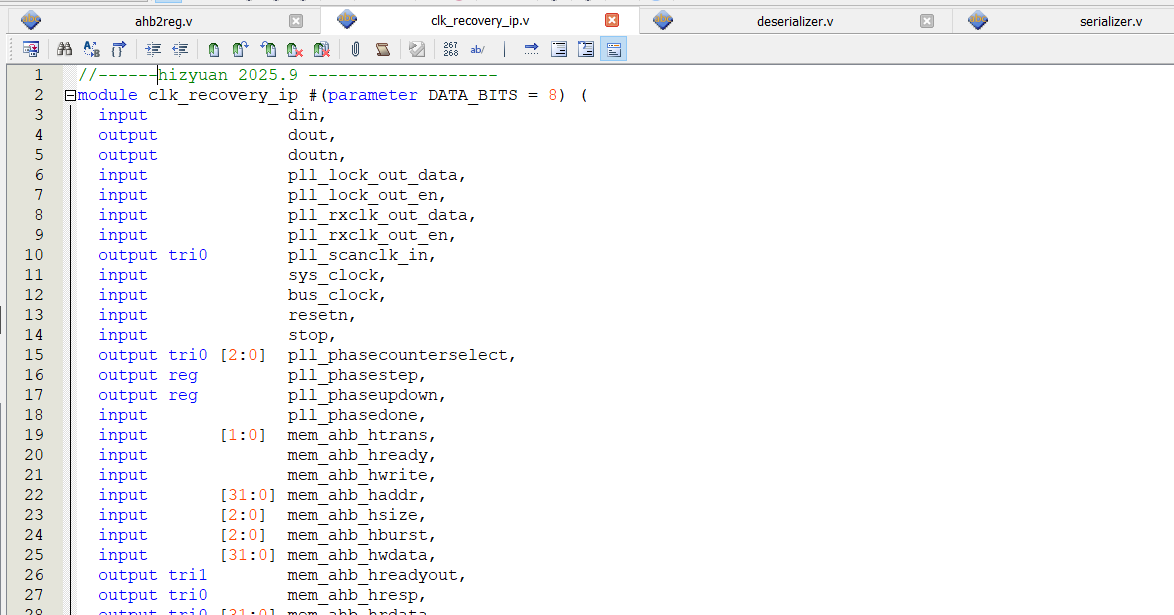

- 以下是clk_recovery_ip.v模块的部分代码:

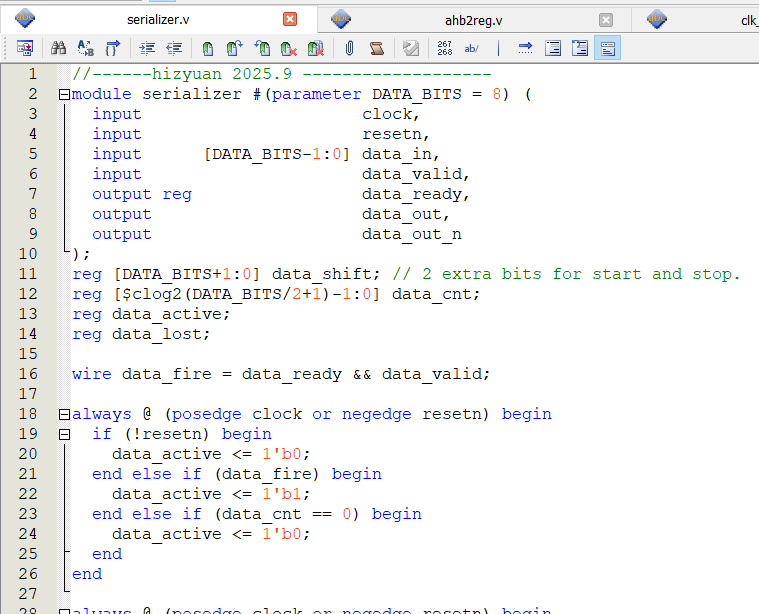

- 以下是serializer.v模块的部分代码:

四、方案优势

- 性能更优:AG32 内置2K cpld,资源更丰富;

- 成本更低:减少外围元件数量,简化电路布局,提升PCB空间利用率;

- 设计更灵活:AG32 MCU + CPLD架构,拓展接口丰富,满足更多功能需求。AG32具有多种封装(32/48/64/100)可供选择。

- 提供方案定制开发: 对量大的需求,AGM可以提供方案定制开发。

3001

3001

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?