点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材什么引入interface?

将设计和验证从逻辑上和时间上分开,使得两个小组可以相对独立;

IC 设计的复杂度逐渐增加,模块之间的连接也逐渐复杂,传统的 Verilog 信号连接方式代码量太大,容易出错,且不易于复用。

Interface的优势

简洁:

1、使用 Interface 在验证中添加、删除和修改信号时只需要修改 Interface 和使用该 Interface 的模块,怎么理解?

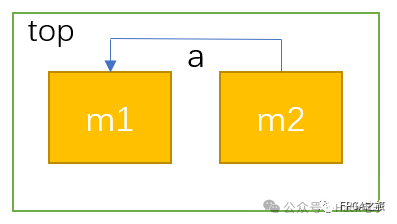

如图所示:顶层模块top例化了模块m1和m2,a信号从m2经过顶层模块到m1。假设现需将信号a修改为b,不使用接口的情况下,m1、m2及top模块都应该做出相应的修改;若使用接口,top例化的是接口,接口内的信号修改只需要修改m1、m2相关部分即可。

2、两个块之间有两个以上的信号连接,并且使用特定的协议时,使用接口更利于复用。

软硬件域的桥梁:

Interface 是硬件域( module、设计中使用)和软件域( class、验证环境中使用)交互的唯一方式。

定义要点

Interface 的定义与 Module 类似,可以参考 Module 的定义方法;由于接口直接与DUT打交道,因此变量建议声明为四值逻辑logic;同时为了防止验证环境带来的竞争问题,驱动硬件的信号应使用非阻塞赋值;Interface端口列表中只需要定义时钟、复位等公共信号,或者不定义任何端口信号。

使用示例

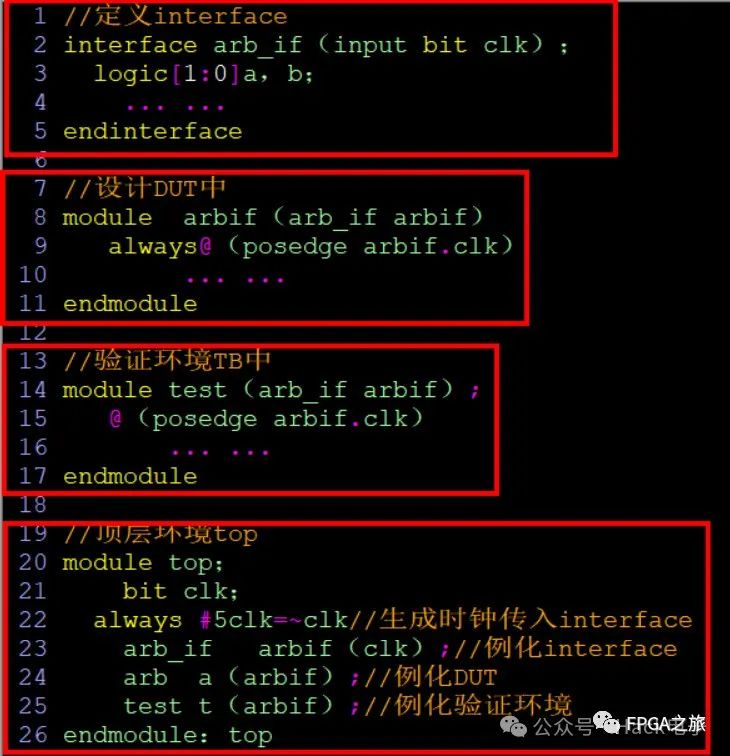

首先定义interface,然后在顶层例化后作为module的端口列表分别传入DUT和TB中。

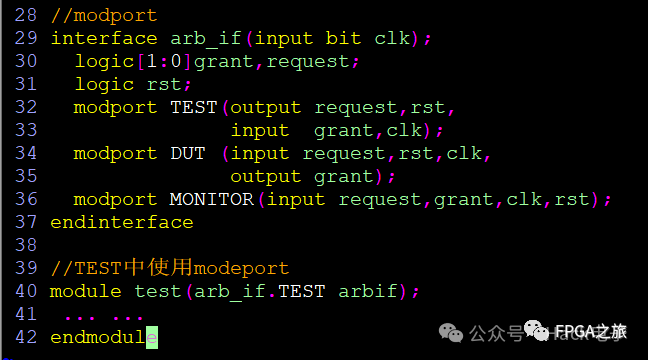

接口中的modport

前一个例子中使用了点对点无信号方向的连接方式。在使用该端口的原始网单里包含了方向信息,编译器依次来检查连线错误。也可以通过modport来进一步限定信号传输的方向,避免端口连接的错误。

需要注意的是modport中的input和output方向是调用该modport模块的输入输出方向,比如TEST的modport内声明的方向,就是调用它的test模块输入输出。

事实上modport在验证环境中使用并不多,因为下文提到的不但clocking块包含了modport的方向信息,同时clocking块也可作为同步信号的驱动。

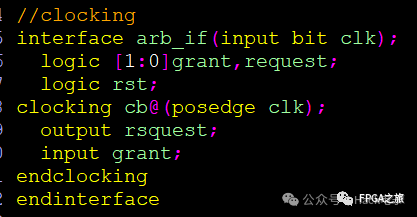

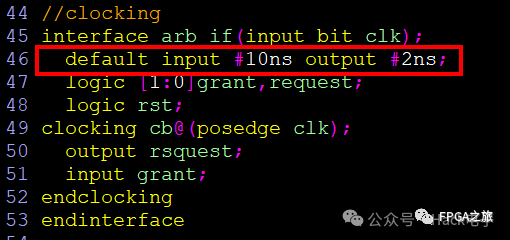

接口中的clocking块

clocking 块,用来对同步信号进行采样和驱动,可以避免设计和验证的竞争。clocking block需要指定一个触发时钟,比如posedge clk、negedge clk。

同若验证环境中需要同步驱动,利用“arb_if.cb.*” 的方式利用clocking块中的信号进行驱动即可。

同时可以为clocking块中信号设置建立和保持时间,若未设置建立时间或保持时间时则会默认在clocking事件前1step输入采样,在事件后#0对输出驱动。

标注的语句表示在时钟上升沿前10ns进行采样,在时钟上升沿2ns后进行驱动。怎么理解?事实上这个步骤主要是为了模拟实际的硬件行为,感兴趣的可以自己画几级触发器来分析,TB对DUT的驱动一侧相当于DUT的上一级触发器,采样DUT数据一侧的TB相当于DUT的下一级寄存器。

几点注意:clocking不是interface独有的,module、program也可以声明clocking模块;clocking中列举的信号都是由interface、module、program等声明了clocking的模块定义的,cloking自身不声明信号;一个interface中可以定义多个clocking,同一个变量可以在多个clocking块中被应用,且可以声明不同的输入输出方向。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

7960

7960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?