----------------------感谢移知的SV课程------------

在芯片的验证过程中,实施验证通常需要经过以下几个步骤:生成输入激励、捕获输出响应、决定对错、衡量进度、反复迭代。

Verilog模块互联

对Verilog来说,主要通过模块的端口(例化)实现模块之间的互联。例如:

Verilog模块的端提供了一种描述设计中模块之间连接关系的方式, 但不适用与芯片验证,在验证中有很多缺点:

在多个模块中必须重复声明端口

在不同模块中有声明不匹配的风险

设计规范中的一个改动需要修改多个模块

限制了抽象的自顶向下的设计

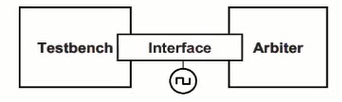

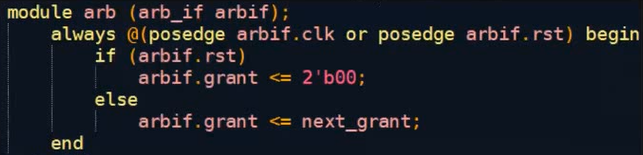

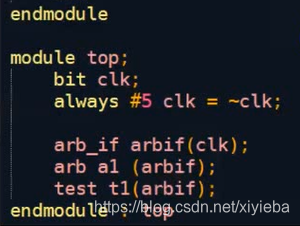

SystemVerilog在Verilog语言基础上扩展了"接口” (interface) 结构,接口给模型提供了一种新的方式,通过使用接口可以简化大型复杂设计的建模和验证。

SystemVerilog增加了新的端口类型—接口,接口允许许多信号合成一组由一个端口表示,只需在一个地方对组成接口的信号进行声明,使用这些信号的模块只需一个接口类型的端口。

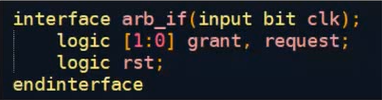

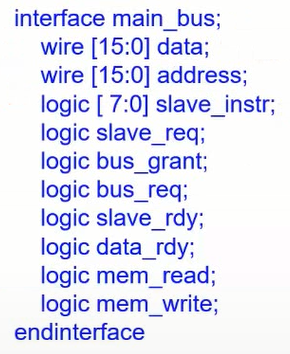

接口使用interface… endinterface声明,将信号包含在其中,封装起来。

接口可以包含类型声明、任务、函数、过程块、程序块和断言。

接口与模块之间有三个不同点: (1) 接口不可以包含设计层次,接口不可以包含模块或原语的实例; (2) 在接口中使用模块则是非法的(3)接口可以包含"modport" ,这使得每个连接到接口上的模块以不同的方式访问接口。

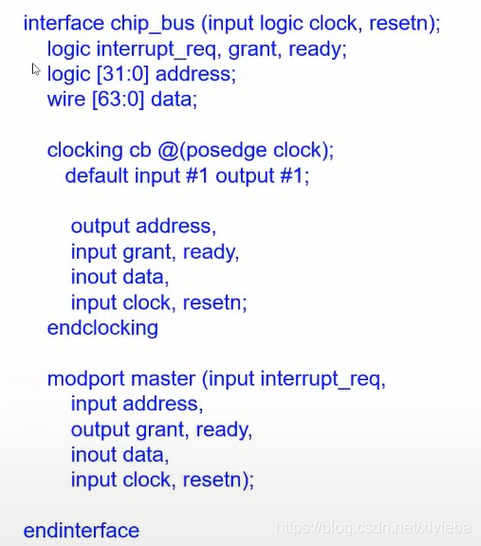

clocking

在interface中,clocking是一个很重要的模块,数字电路很多都是同步的,在clocking中定义时钟触发条件,里面的信号就跟随触发条件同步

其中驱动信号 chip_bus.cp.address <= 32’h8;

引用信号 if(chip_bus.cb.ready)…

重复几个时钟的事件推进repeat(2)@chip.bus.cb;

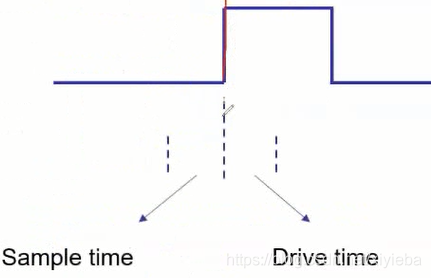

如何理解上面的default input #1 output #1

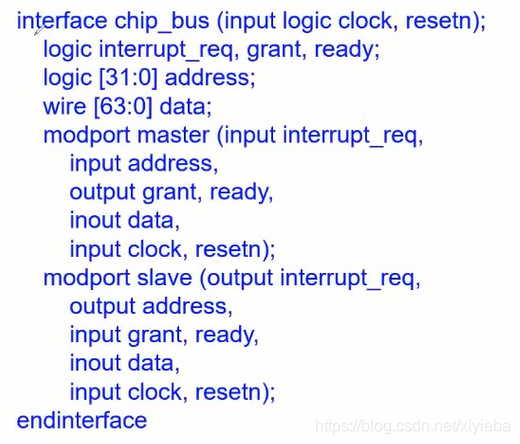

modport

SystemVerilog定义接口时,可以定义接口信号的不同接入方式,以处理不同模块连接到接口端口的方向问题。modport的定义从模块角度描述了接口表示的端口的接入方式,接口中可以有任意数量的modport定义,每个定义描述了各个模块访问接口中的信号。

modport定义中不包含向量位数和类型,这些信息在接口的信号类型声明中定义。事实上modport声明只是使相互连接的模块将信号看成是input、output, inout还是ref。

在复杂设计的接口中,不是每个模块需要访问相同的接口信号,modport为每 个模块创建自己的接口。

通过modport使得模块只可以直接访问在modport定义中列出的信号,达到接口中的某些信号对某些模块隐藏的目的。

接口中可以定义对任何modport都不可见的内部信号,这些信号只能由接口中的协议检查器或其它功能模块使用。

如果连接到接口的模块没有指定modport,模块则可以访问接口中定义的所有信号.

783

783

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?