关注、星标公众号,精彩内容每日送达

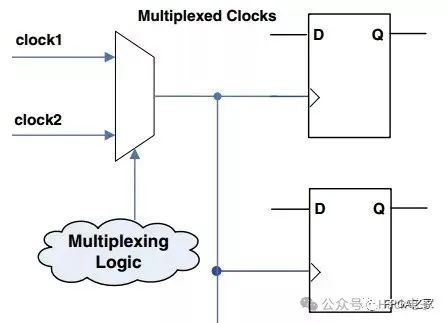

来源:网络素材时钟多路器用于使同一个逻辑功能具有不同的时钟,比如在通信系统中,为了适应不同的数据速率要求,经常要进行时钟切换。有时为了节约功耗,也会把高速时钟切换到低速时钟,或者进行时钟休眠操作。下图是某一类型的时钟多路器:

虽然在时钟信号上引入多路逻辑会产生毛刺等问题,但是在不同的应用中,对多路时钟的要求区别很大。时钟切换的最佳途径是使用FPGA内部的专用Clock MUX,这些MUX的反应速度快,锁定时间短,切换瞬间带来的冲击和抖动小。如果器件内没有专用的Clock MUX,应尽量满足如下几点:

时钟切换控制逻辑在配置后将不再改变。

在时钟切换后,对相关电路复位,以保证寄存器等电路状态不会锁死或者进入死循环。

所设计的系统对时钟切换过程发生的短暂错误不敏感。

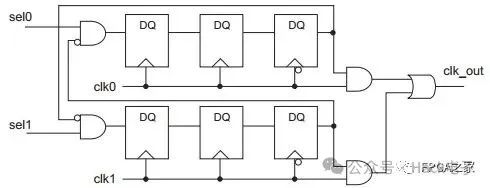

如果设计中时钟切换很频繁,并且不在复位时切换,设计中也不能允许出现短暂的错误,就必须使用同步设计以确保寄存器没有违背时序,时钟信号上不会出现毛刺等问题。下图是一个无毛刺的时钟多路复用器:

上图的结构适用于任意数量的时钟通道,而且在切换的过程中,可以容许极端的竞争冒险。

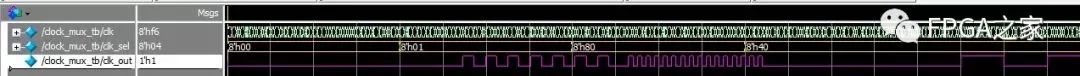

以下是时钟多路复用器功能仿真波形图,具体代码请参考下方参考代码链接,同时Altera也提供了对应的IP核,详情请参考Clock Control Block (ALTCLKCTRL) Megafunction User Guide

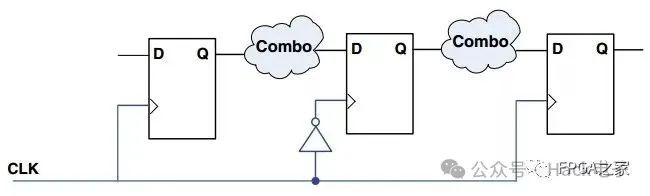

双沿时钟是指在时钟的上升沿和下降沿都传输数据,这样使得数据传输在给定的时钟速率下能达到双倍的吞吐率,下图是一个由双沿时钟触发电路:

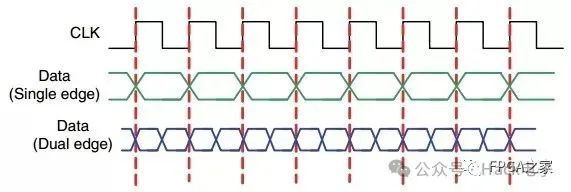

使用双沿时钟可能存在一些问题,时钟的非对称占空比可能导致违背建立和保持时钟,而且很难确定关键信号的路径。下图是时钟驱动的单沿数据传输和多沿数传输波形图:

在对性能和速度要求很高的情况下,并且无法承受使用等效同步电路在DFT和验证方面所带来的额外开销外,可使用双沿时钟。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

617

617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?