14天学习训练营导师课程:周贺贺《ARMv8/ARMv9架构-快速入门》

1. 定义

Cache是ARM中一块可高速访问的内存块,每块cache包含:

- 主要的内存地址信息;

- 缓存数据。

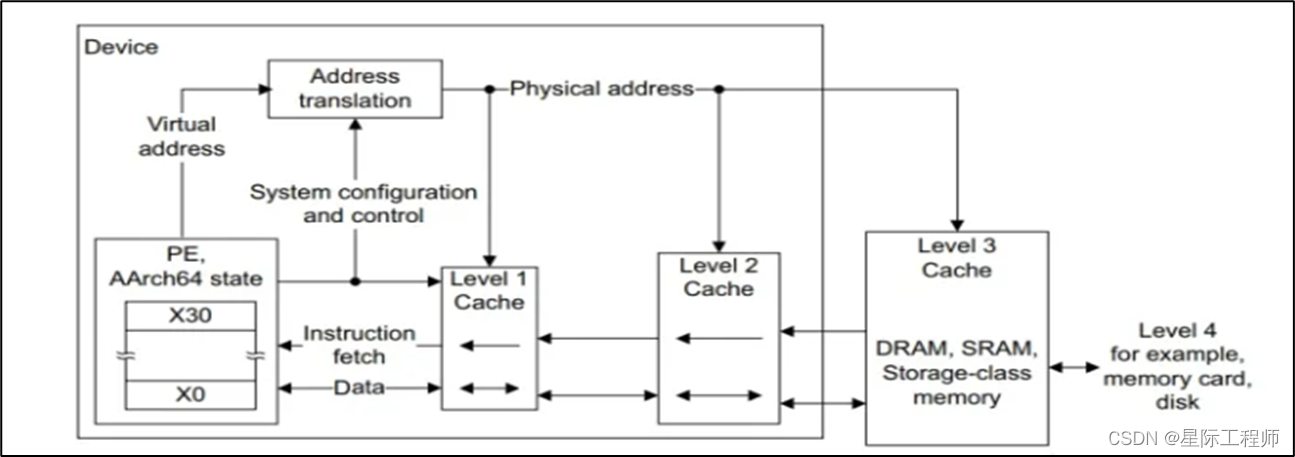

2. Cache模型

速度方面:L1 cache > L2 cache > L3 cache

容量方面:L1 cache < L2 cache < L3 cache

多级Cache工作流程:

当CPU试图从某地址载入数据时,首先从L1 cache中查询是否命中,如果命中则把数据返回给CPU,如果L1 cache缺失,则继续从L2 cache中查找。当L2 cache命中时,数据会返回给L1 cache及CPU。如果L2 cache中也缺失,很遗憾,我们需要从主存中加载数据,将数据返回给L2 cache、L1 cache和CPU。这种多级cache的工作方式称为inclusive cache(某一地址的数据可能存在多级缓存中)。与inclusive cache对应的是exclusive cache,这种cache保证某一地址的数据缓存只会存在于多级cache的其中一级,也就是说任意地址的数据不可能同时在L1和L2 cache中。

3. 术语和基本概念

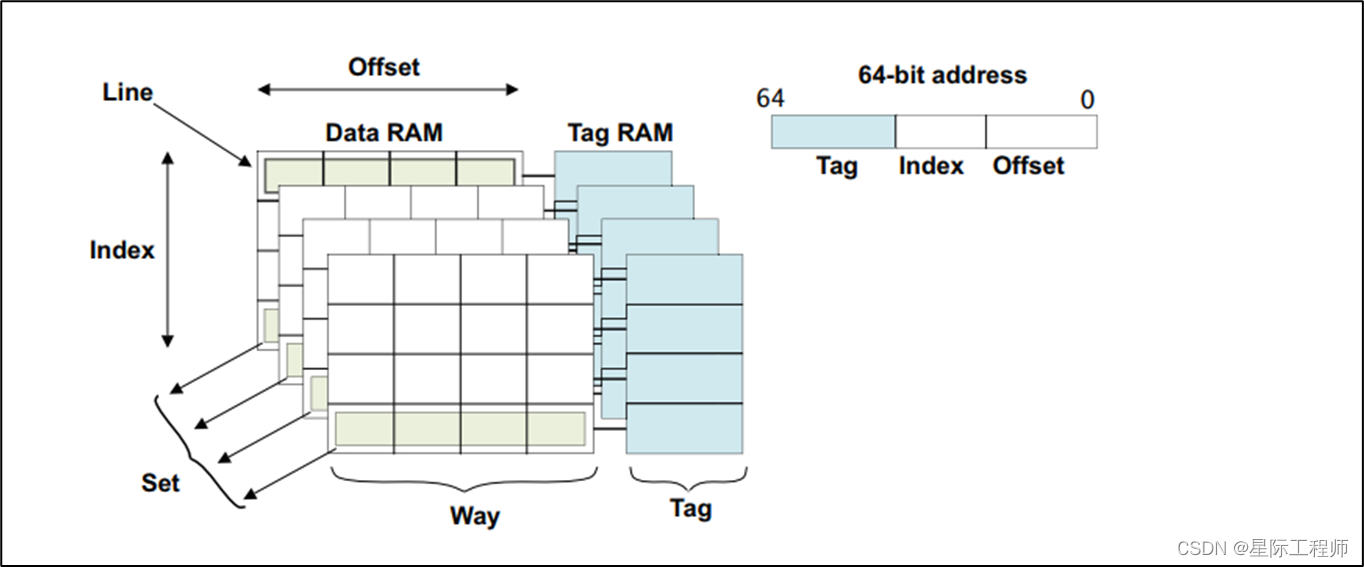

Tag是存储在缓存中的内存地址的一部分,用于标识与一行数据关联的主内存地址。64位地址的顶部位告诉缓存信息来自主存的位置,称为标记。虽然计算中不包括用于保存标记值的RAM,但总缓存大小是它可以保存的数据量的度量。但是,标记确实会占用缓存中的物理空间。

为每个标记地址保存一个字的数据效率很低,因此通常会将多个位置分组在同一个标记下。这个逻辑块通常被称为Cache Line,指的是缓存中最小的可加载单元,即来自主存的连续字块。缓存线包含缓存数据或指令时称为有效,不包含缓存数据或指令时称为无效。

与每行数据关联的是一个或多个状态位。通常,您有一个有效位,将该行标记为包含可使用的数据。这意味着地址标签代表一些实际值。在数据缓存中,还可能有一个或多个脏位,用于标记缓存线(或缓存线的一部分)是否包含与主内存内容不同(更新)的数据。

索引是内存地址的一部分,用于确定可以在缓存的哪些行中找到地址。地址或索引的中间位标识行。索引用作缓存RAM的地址,不需要存储作为标记的一部分。本章后面将详细介绍这一点。

路径是缓存的细分,每条路径大小相同,索引方式相同。一个集合由共享特定索引的所有方式的缓存线组成。

这意味着地址底部的几个位(称为偏移量)不需要存储在标记中。需要一整行的地址,而不是该行中的每个字节的地址,因此五或六个最低有效位始终为0。

183

183

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?