McBSP(多通道缓冲串口)

McBSP(多通道缓冲串口)是德州仪器(TI)C55x系列DSP芯片中一种高度灵活的串行通信接口,可以理解为 DSP的“多功能数据收发站”。

一、初识McBSP

1. McBSP是什么?

想象你有一个快递站(DSP),需要和外界收发包裹(数据)。McBSP就是这个快递站的“智能分拣系统”:

- 多通道:支持多个独立的“快递通道”(比如同时收发语音、传感器数据、控制信号)。

- 缓冲:自带临时仓库(缓冲区),包裹可以暂存,避免快递车(DSP)被频繁打扰。

- 串口:通过“串行传输”一根一根传递包裹(数据位),节省线路成本。

2. McBSP有什么用?

核心作用:让DSP高效地与外部设备“对话”。比如:

- 连接其他DSP:多个DSP协同工作(如音频处理阵列)。

- 连接编解码器(Codec):比如将麦克风的模拟声音转为数字信号给DSP处理,或把DSP处理后的音乐送给扬声器播放。

- 工业控制:连接传感器(温度、压力)或执行器(电机、LED屏)。

- 通信系统:传输调制解调后的无线信号、网络数据等。

3. 如何利用McBSP?

使用McBSP就像配置快递站的规则,分三步:

步骤1:配置通信规则

通过DSP的寄存器设置参数:

- 时钟:数据收发节奏(类似快递车的发车频率)。

- 数据格式:每个“包裹”的大小(比如16位音频数据)。

- 通道选择:启用哪些通道(比如只用通道0和1传语音)。

步骤2:数据收发

- 发送数据:把数据写入McBSP的发送缓冲区,它会自动按规则串行发出。

- 接收数据:McBSP接收外部数据后,存入接收缓冲区,DSP直接读取。

步骤3:高效处理

- 用DMA辅助:让DMA控制器自动搬运数据,解放DSP核心去算数学(比如滤波、编码)。

- 中断通知:当数据收/发完成时,McBSP触发中断,提醒DSP处理。

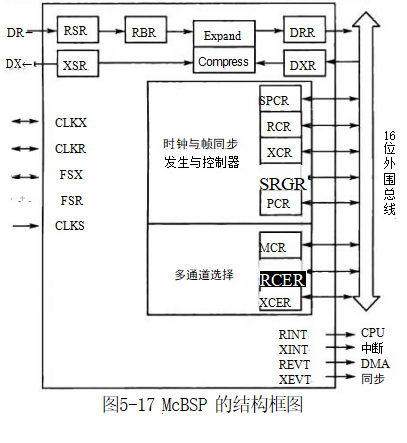

二、McBSP组成框图

- McBSP 的结构框图可以分为数据通道和控制通道两部分,如图5-17所示。数据发送引 脚DX 负责数据的发送,数据接收引脚 DR

负责数据的接收,发送时钟引脚CLKX 、接收时 钟引脚CLKR、发送帧同步引脚FSX 和接收帧同步引脚FSR 提供串行时钟和控制信号。 - CPU 和 DMA 控制器通过外设总线与McBSP 进行通信。当发送数据时,CPU 和 DMA 将数据写入数据发送寄存器(DXR1,DXR2), 接着复制到发送移位寄存器(XSR1,XSR2), 通过发送移位寄存器输出至DX 引脚。同样,当接收数据时,DR 引脚上接收到的数据先移位到 接收移位寄存器 (RSR1,RSR2), 接着复制到接收缓冲寄存器(RBR1,RBR2),RBR再将数 据复制到数据接收寄存器(DRR1,DRR2) 中,并通知串口事件通知 CPU 或 DMA 读取数据。这种多级缓冲方式使片内数据通信和串行数据通信能够同时进行。

三、McBSP的采样率发生器

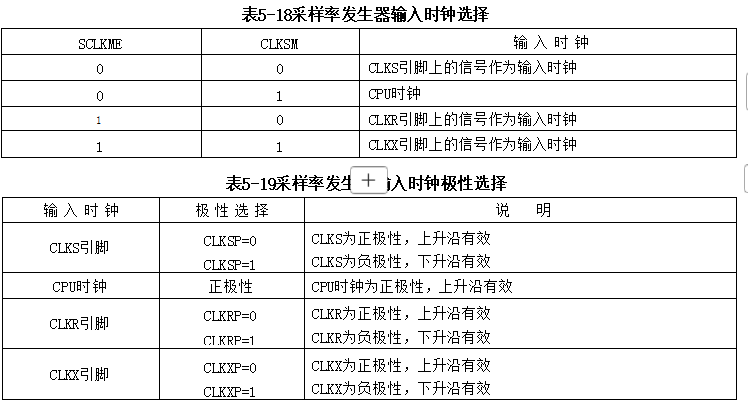

- McBSP 包括一个采样率发生器 SRG, 用于产生内部数据时钟CLKG 和内部帧同步信号 FSG, 如图5-18所示。CLKG控制DR 上数据的移位和DX 上的数据发送;FSG 控制DR 和 DX 上的帧同步。

- 采样率发生器的时钟源可以由CPU 时钟或外部引脚 (CLKS,CLKX 或 CLKR) 提供,时钟源的选择可以通过引脚控制寄存器 PCR 中的 SCLKME 字段和采样率发生寄存器 SRGR2 中的CLKSM字段来确定,参见表5-18。输入信号的极性由 SRGR2 中的CLKSP 字 段、PCR 中 的CLKXP 字段或CLKRP 字段确定,参见表5-19。

我们可以将 采样率发生器(SRG) 的工作机制比作一个 “智能节奏控制中心”,它通过分频和同步,精确控制数据收发的时钟和帧同步信号。

1. 输出时钟 CLKG:分频与占空比

(1) 分频原理

- 输入时钟 → 像“心脏跳动”,提供基础节奏(例如 100 MHz 的 CPU 时钟或外部时钟)。

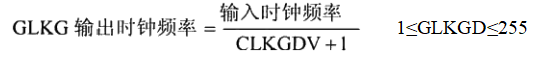

- 分频值 CLKGDV → 决定将输入时钟“减速”多少倍,生成 CLKG,分频值由采样率发生寄存器 SRGR1中的CLKGDV 字段确定:

-

公式:

-

范围:CLKGDV = 1~255 → 分频后最低频率为输入时钟的 1/256。

-

极限:当 CLKGDV=1 时,CLKG 频率为输入时钟的一半(最高频率)。

-

(2) 占空比规则

-

CLKGDV 为奇数:

→ CLKG 的 高电平和低电平时间相等(占空比 50%)。- 例如:CLKGDV=3 → 每 4 个输入时钟周期为一个 CLKG 周期,高低电平各占 2 周期。

-

CLKGDV 为偶数(2p):

→ 高电平比低电平多 1 个输入时钟周期。- 例如:CLKGDV=4(即 p=2)→ 高电平占 3 周期,低电平占 2 周期。

- 意义:适应某些外部设备对非对称时钟的需求。

2. 帧同步信号 FSG:分频与脉宽

FSX 和 FSR 是 McBSP 的同步指挥官,确保数据收发在正确的时间点开始。

核心功能:定义帧边界,对齐发送端和接收端的时序。

场景模拟:DSP 连接音频编解码器(Codec)

FSX(发送):DSP 通过 FSX 告诉 Codec:“我要开始发送音频数据了!” → Codec 开始接收。

FSR(接收):Codec 通过 FSR 告诉 DSP:“我要开始发送麦克风数据了!” → DSP 开始接收

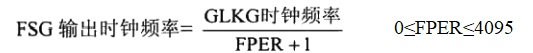

(1) 帧同步分频(FPER)

- 分频值 FPER → 决定 多少 CLKG 周期触发一次帧同步(FSG)。

-

公式:

-

范围:FPER = 0~4095 → 最大帧周期为 4096 个 CLKG 周期。

-

示例:

- 若 CLKG=1 MHz,FPER=99 → 每 100 μs 触发一次 FSG(即帧率 10 kHz)。

-

(2) 脉冲宽度(FWID)

- FWID → 控制 FSG 脉冲的 持续时间。

-

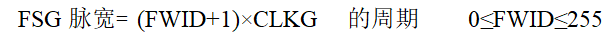

公式:

-

范围:FWID = 0~255 → 最大脉宽为 256 个 CLKG 周期。

-

示例:

- 若 CLKG=1 MHz,FWID=1 → 脉宽为 2 μs(高电平持续 2 个 CLKG 周期)。

-

3. 同步控制(GSYNC)

(1) 自由运行模式(GSYNC=0)

- SRG 独立工作:

→ CLKG 和 FSG 完全由分频参数(CLKGDV、FPER、FWID)控制,无视外部时钟。 - 应用场景:

- DSP 作为主设备,主动控制时序(如驱动麦克风、传感器)。

(2) 同步模式(GSYNC=1)

- SRG 与外部时钟同步:

→ CLKG 和 FSG 的相位会与外部输入时钟对齐,避免累积误差。 - 应用场景:

- DSP 作为从设备,需与外部主设备(如 FPGA、其他 DSP)严格同步。

4. 配置示例:音频传输

目标:

- 实现 48 kHz 采样率,16 位数据帧,CLKG 频率 1.536 MHz(48k × 32)。

步骤:

-

CLKG 配置:

- 输入时钟 = CPU 时钟 24 MHz。

- CLKGDV = 15 → CLKG 频率 = 24 MHz / (15+1) = 1.5 MHz。

- CLKGDV 为奇数(15),占空比 50%。

-

FSG 配置:

- FPER = 31 → 每 32 个 CLKG 周期触发一次 FSG(1.5 MHz / 32 = 46.875 kHz ≈ 48 kHz)。

- FWID = 0 → 脉宽为 1 个 CLKG 周期(0.67 μs)。

-

同步模式:

- 若使用外部主设备时钟,设置 GSYNC=1,确保相位对齐。

附:参数配置速查表

| 功能 | 寄存器字段 | 公式/规则 | 示例 |

|---|---|---|---|

| CLKG 分频值 | SRGR1.CLKGDV | CLKG 频率 = 输入频率 / (CLKGDV+1) | CLKGDV=15 → 分频 16 倍 |

| CLKG 占空比 | CLKGDV 奇偶性 | 奇数为 50%,偶数为 (p+1)/p | CLKGDV=4 → 高 3 周期,低 2 周期 |

| FSG 周期(FPER) | SRGR2.FPER | 周期 = (FPER+1) × CLKG 周期 | FPER=31 → 32 CLKG 周期 |

| FSG 脉宽(FWID) | SRGR1.FWID | 脉宽 = (FWID+1) × CLKG 周期 | FWID=1 → 2 CLKG 周期 |

| 同步模式 | SRGR2.GSYNC | 0=自由运行,1=同步外部时钟 | GSYNC=1 用于多设备级联 |

通过合理配置这些参数,可以让 McBSP 像精准的“节奏大师”,确保数据收发与外部设备完美同步! 🎶

四、McBSP多通道选择

- McBSP 属于多通道串口,每个 McBSP 最多可有128个通道。如图5-17所示,其多通道 选择部分由多通道控制寄存器MCR、接收使能寄存器 RCER 和发送使能寄存器XCER 组成。 其中,MCR 可以禁止或使能全部128个通道,RCER 和 XCER 可以分别禁止或使能某个接收 或发送通道。每个寄存器控制16个通道,因此128个通道共有8个通道使能寄存器。

- 我们可以将 McBSP 的多通道选择机制 想象成一个 “多车道高速公路管理系统”,通过寄存器控制哪些车道(通道)允许车辆(数据)通行。

1. 接收多通道选择(接收方向:外部 → DSP)

(1) 控制寄存器与模式

- MCR1 中的 RMCM 位:总开关,决定是否启用通道选择模式。

- RMCM=0:所有 128 条接收车道 全开放(默认模式)。

- RMCM=1:启用 通道选择模式,由 RCER 寄存器 精细控制每条车道。

(2) RCER 寄存器的作用

- 每个 RCER 控制 16 个通道,共 8 个 RCER 覆盖 128 个通道。

- 某位=1 → 允许该通道数据进入接收缓冲区(RBR → DRR)。

- 某位=0 → 禁止该通道数据(数据仍会进入 RBR,但不会复制到 DRR,且不触发 DMA 事件)。

2. 发送多通道选择(发送方向:DSP → 外部)

(1) 控制寄存器与模式

- MCR2 中的 XMCM 字段:决定发送通道的全局管理模式。

| XMCM 值 | 模式 | 通俗解释 |

|---|---|---|

| 00b | 所有 128 个发送通道全开放 | 所有车道无条件开放,无限制 |

| 01b | 由 XCER 选择允许的通道 | 只开放 XCER 指定的车道 |

| 10b | 由 XCER 选择禁止的通道 | 关闭 XCER 指定的车道,其余开放 |

| 11b | 发送通道与接收通道联动 | 发送车道是否开放,取决于对应的接收车道是否开放 |

(2) XCER 寄存器的作用

- 每个 XCER 控制 16 个通道,共 8 个 XCER 覆盖 128 个通道。

- 某位=1 → 在 XMCM=01b 时允许该通道发送;在 XMCM=10b 时禁止该通道。

(3) 模式对比与示例

-

XMCM=01b(白名单模式):

- 示例:仅允许通道 4~7 发送数据 → 设置 XCER0 = 0x00F0(二进制

0000 0000 1111 0000)。

- 示例:仅允许通道 4~7 发送数据 → 设置 XCER0 = 0x00F0(二进制

-

XMCM=10b(黑名单模式):

- 示例:禁止通道 8~15 发送数据 → 设置 XCER1 = 0x00FF(二进制

0000 0000 1111 1111)。

- 示例:禁止通道 8~15 发送数据 → 设置 XCER1 = 0x00FF(二进制

-

XMCM=11b(联动模式):

- 发送通道 N 的开启条件:对应的接收通道 N 被 RCER 允许,且 XCER 未屏蔽该通道。

- 应用:全双工通信中,仅当接收端允许某通道时,发送端才启用该通道(避免资源浪费)。

4. 关键配置步骤

(1) 接收通道配置

- 设置 MCR1.RMCM=1(启用通道选择模式)。

- 根据需要,配置 RCER0~RCER7,允许特定通道(某位=1)。

(2) 发送通道配置

- 设置 MCR2.XMCM 选择模式(如 01b 白名单)。

- 根据模式,配置 XCER0~XCER7:

- XMCM=01b:允许的通道对应位设为 1。

- XMCM=10b:禁止的通道对应位设为 1。

5. 注意事项

- 数据覆盖风险:若未及时读取 DRR 数据,新数据会覆盖旧数据。

→ 通过中断或 DMA 及时处理数据。 - 通道冲突:避免同时启用过多通道超出 DSP 处理能力。

→ 根据实际需求精简通道数量。 - 同步问题:在联动模式(XMCM=11b)下,需确保接收和发送通道配置一致。

六、McBSP寄存器

- McBSP 的寄存器主要包括3部分:收发通道寄存器、时钟和帧同步寄 存器、多通道选择寄存器。

1. 收发通道寄存器

- 收发通道中CPU 或 DMA 控制器可以访问的寄存器包括数据接收寄存器DRR 和数据发 送寄存器 DXR 。由 于McBSP 支持8位、12位、16位、20位、24位或32位的字长,当字 长等于或小于16位,只使用DRR1/DXR1, 当字长超过16位, DRR1/DXR1 存放低16位, DRR2/DXR2 存放其余数据位。

2. 时钟和帧同步寄存器

- 时钟和帧部分寄存器主要用于控制时钟和帧同步信号的产生、收发数据帧格式和串口 状态的检测等。

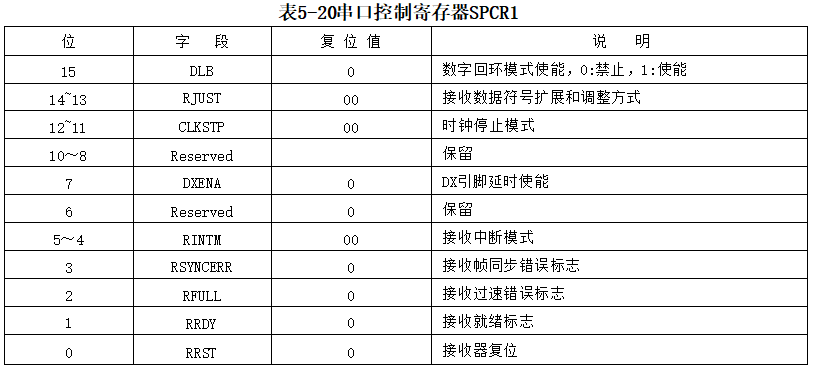

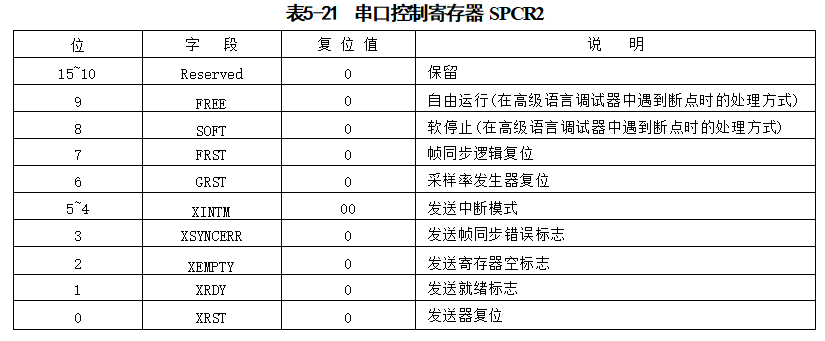

(1)串口控制寄存器

- 每个 McBSP 有两个串口控制寄存器SPCR1 和 SPCR2, 用于控制McBSP 的工作模式、检测收发操作的状态和对McBSP 的各部分复位,如表5-20和表5-21所示。

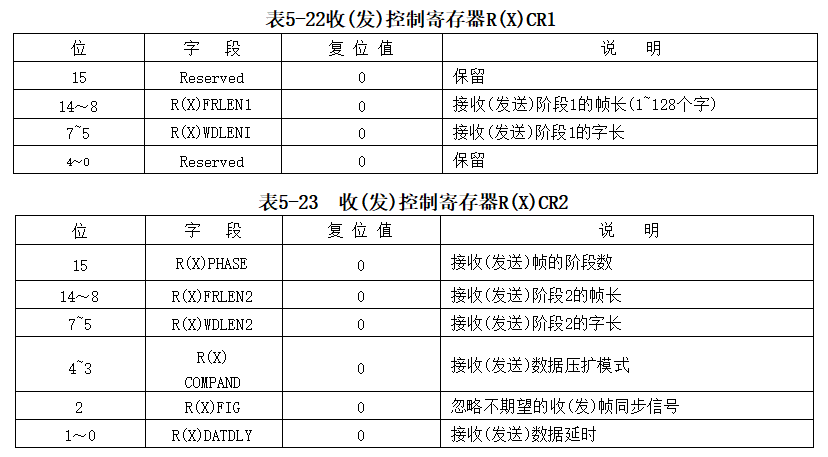

(2)收发控制寄存器

- 每个 McBSP 有两个接收控制寄存器 R(X)CR1 和 R(X)CR2, 以及两个发送控制寄存器 XCR1 和XCR2, 用于选择或使能数据延时和帧同步忽略等参数,如表5-22和表5-23所示。

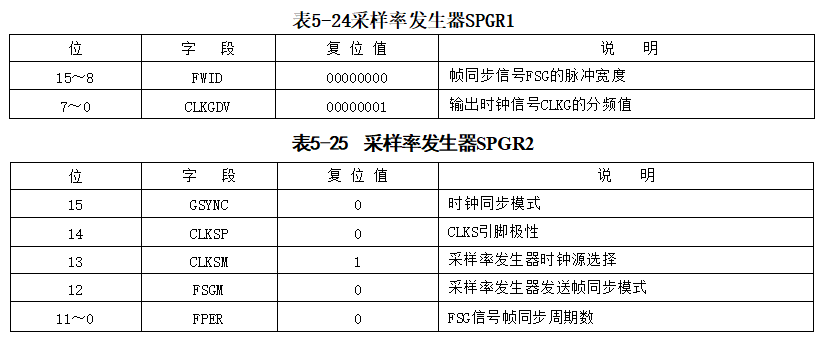

(3)采样率发生寄存器

- 每个 McBSP 有两个采样率发生寄存器 SPGR1 和 SPGR2, 用于选择与时钟和帧同步有 关的参数,如表5-24和表5-25所示。

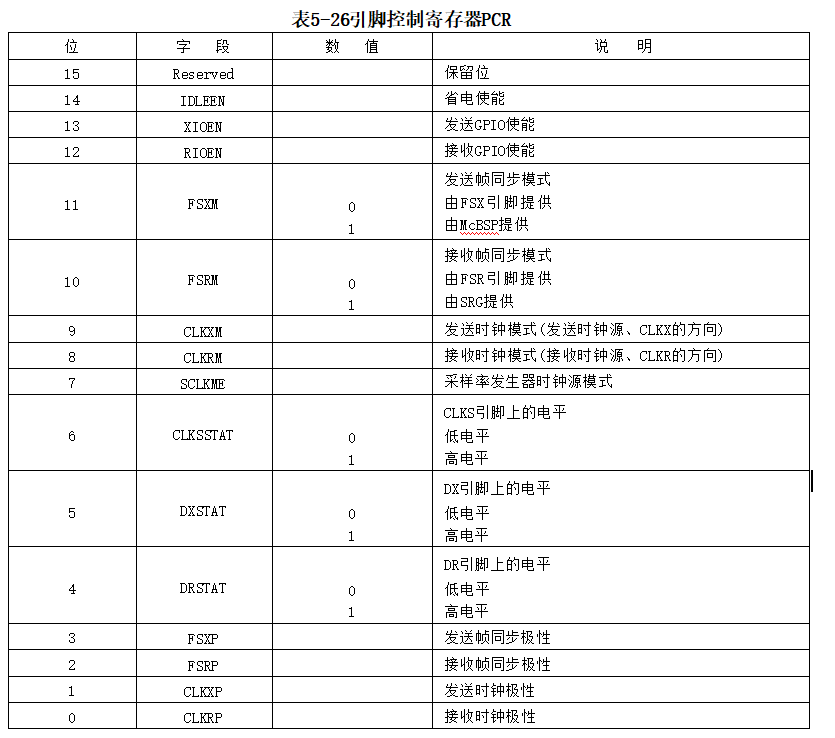

(4)引脚控制寄存器

- 每个 McBSP 有一个引脚控制寄存器 PCR, 用 于McBSP 省电模式控制和接收(发送) 帧同步模式的选择,如表5-26所示。

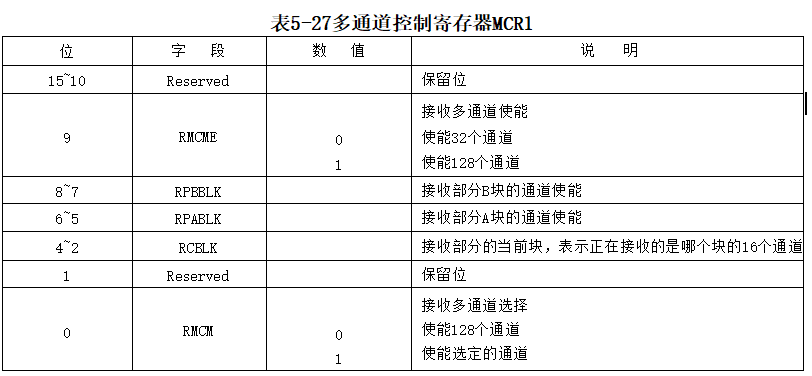

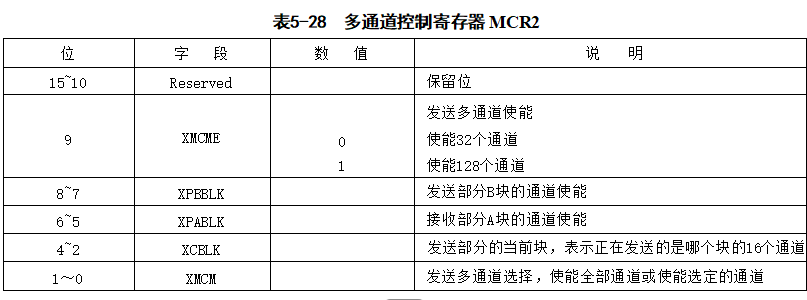

3. 多通道选择寄存器

- 多通道选择寄存器包括多通道控制寄存器和收发通道使能寄存器。

(1)通道控制寄存器

- 每个McBSP 有两个多通道控制寄存器MCR1 和 MCR2, 用于使能所有通道和选择通道 等,如表5-27和5-28所示。

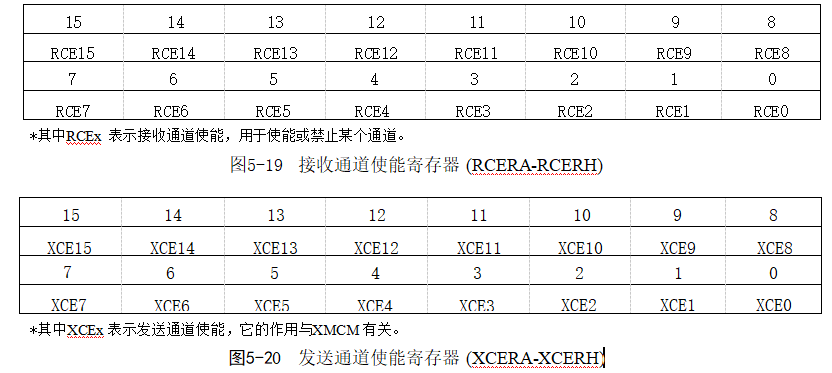

(2)收发通道使能寄存器

- 每个 McBSP 有8个接收通道使能寄存器RCERA 到 RCERH 和8个发送通道使能寄存 器 XCERA 到XCERH, 如图5- 19和图5-20所示。

七、McBSP使用代码示例

C55x DSP 的 McBSP 串口初始化,核心步骤包括:

- 声明配置结构体:定义 McBSP 寄存器参数。

- 打开 McBSP 端口:获取句柄并初始化。

- 配置寄存器:设置时钟、帧同步、数据格式等。

- 启动 McBSP:使能收发功能。

- 设置中断:接收数据就绪时触发中断。

二、关键代码解释

1. 声明 McBSP 句柄和配置结构体

MCBSP_Handle myhMcbsp; // 声明 McBSP 句柄

MCBSP_Config Config_MCBSP = { // 定义 McBSP 配置结构体

0x4000, /* SPCR1 */ // 接收控制寄存器1

0x0040, /* SPCR2 */ // 发送控制寄存器2

0x0020, /* RCR1 */ // 接收参数寄存器1

0x0025, /* RCR2 */ // 接收参数寄存器2

0x0000, /* XCR1 */ // 发送参数寄存器1

0x0004, /* XCR2 */ // 发送参数寄存器2

0x01CB, /* SRGR1 */ // 采样率发生器寄存器1

0x300E, /* SRGR2 */ // 采样率发生器寄存器2

0x0001, /* MCR1 */ // 多通道控制寄存器1

0x0001, /* MCR2 */ // 多通道控制寄存器2

0x0B03, /* PCR */ // 引脚控制寄存器

0x0001, /* RCERA */ // 接收通道使能寄存器A

0x0000, 0x0000, 0x0000, 0x0000, // 其他接收通道使能寄存器B~H(全禁用)

0x0000, 0x0000, 0x0000, 0x0000,

0x0001, /* XCERA */ // 发送通道使能寄存器A

0x0000, 0x0000, 0x0000, 0x0000, // 其他发送通道使能寄存器B~H(全禁用)

0x0000, 0x0000, 0x0000, 0x0000

};

2. McBSP 初始化和启动

// 打开 McBSP 端口0,复位状态

myhMcbsp = MCBSP_open(MCBSP_PORTO, MCBSP_OPEN_RESET);

// 应用配置

MCBSP_config(myhMcbsp, &Config_MCBSP);

// 脱离复位状态(启动采样率发生器)

MCBSP_RSET_H(myhMcbsp, SPCR2, 0x0040);

// 启动 McBSP:接收、发送、采样率发生器、帧同步

MCBSP_start(myhMcbsp,

MCBSP_RCV_START | MCBSP_XMIT_START | MCBSP_SRGR_START | MCBSP_SRGR_FRAMESYNC,

0x300u);

// 设置接收中断

IRQ_plug(IRQ_EVT_RINTO, &RINT_Isr); // 注册中断服务函数

IRQ_enable(IRQ_EVT_RINTO); // 使能中断

9577

9577

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?