前言

最近在一个项目中发现了一个挺有意思的小工具——iverilog,一个verilog编译器,这款verilog编译器的编译速度超快,很适合用于一些小型项目中,也不用特地去安装quartus或者是vivado,像我这样的小白,是真滴香!!!

一、获取Iverilog

从该网址进入,Iverilog官网,选择最新版的Iverilog软件进行下载,教程使用的是windows操作系统。

二、安装

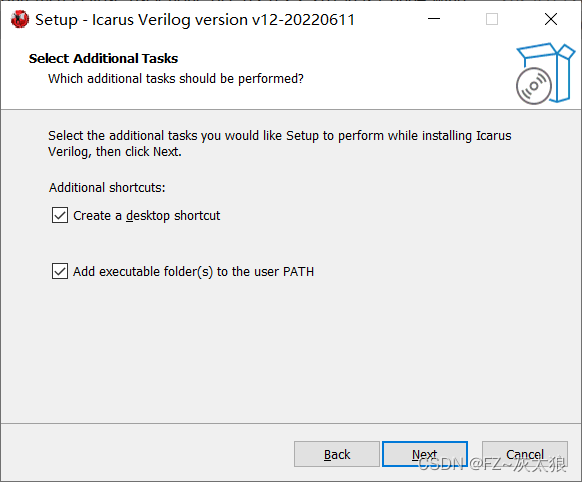

这个软件跟着流程安装就行,不过在安装的时候需要注意一下下面这一步,勾选下面两个勾勾。

检测软件有无安装好,可以在命令行中分别输入下述代码:

where iverilog

where vvp

where gtkwave

运行成功后,命令行会分别显示三个工具的路径。

三、命令行方法

1、编译文件(使用iverilog)

iverilog -o [生成的文件名] [verilog文件]...

对于不在同一目录中的文件,可以使用-y [文件绝对路径]替代文件名,具体将在后述演示中说明。

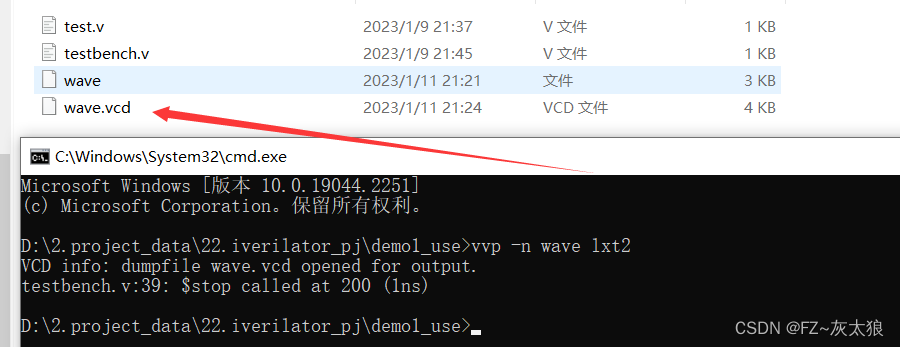

2、生成波形文件(使用vvp)

vvp -n [上一步编译的文件名] -lxt2

testbench中需要加上下述代码才能够生成波形文件

initial begin

$dumpfile("生成波形文件命名.vcd");

$dumpvars(0, testbench名称);

end

3、绘制波形文件(使用gtkwave)

gtkwave [上一步生成的波形文件,需要加上后缀]

四、演示

1、verilog代码

module test (

input clk,

output dout

);

assign dout = ~clk;

endmodule

2、testbench代码

/*

incentive document

*/

`timescale 1ns / 1ns

module testbench();

reg clk;

/* define the wire below */

wire dout;

parameter CYCLE = 2;

parameter END_TIME = 200;

/* init the module below */

test mod(

.clk (clk),

.dout (dout)

);

/***************************************************/

initial begin

$dumpfile("wave.vcd"); //生成的vcd文件名称

$dumpvars(0, testbench); //tb模块名称

end

/***************************************************/

/* init the state */

initial begin

clk = 0;

end

/***************************************************/

/* genrate clock */

always begin

#(CYCLE / 2) clk = ~clk;

end

/***************************************************/

/* stop the simulation */

initial begin

#END_TIME;

$stop;

end

endmodule

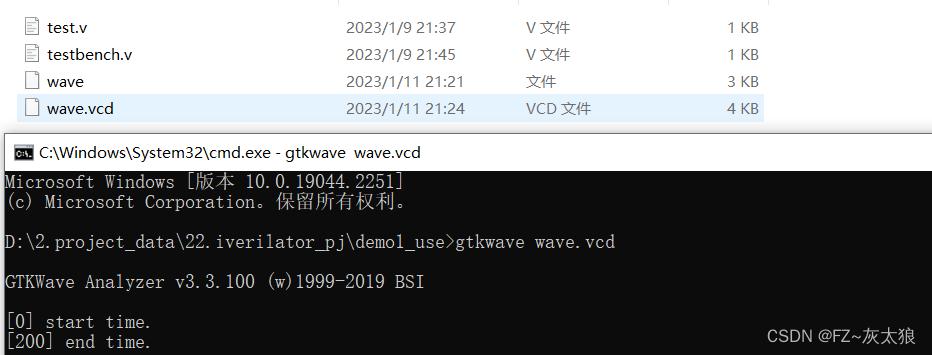

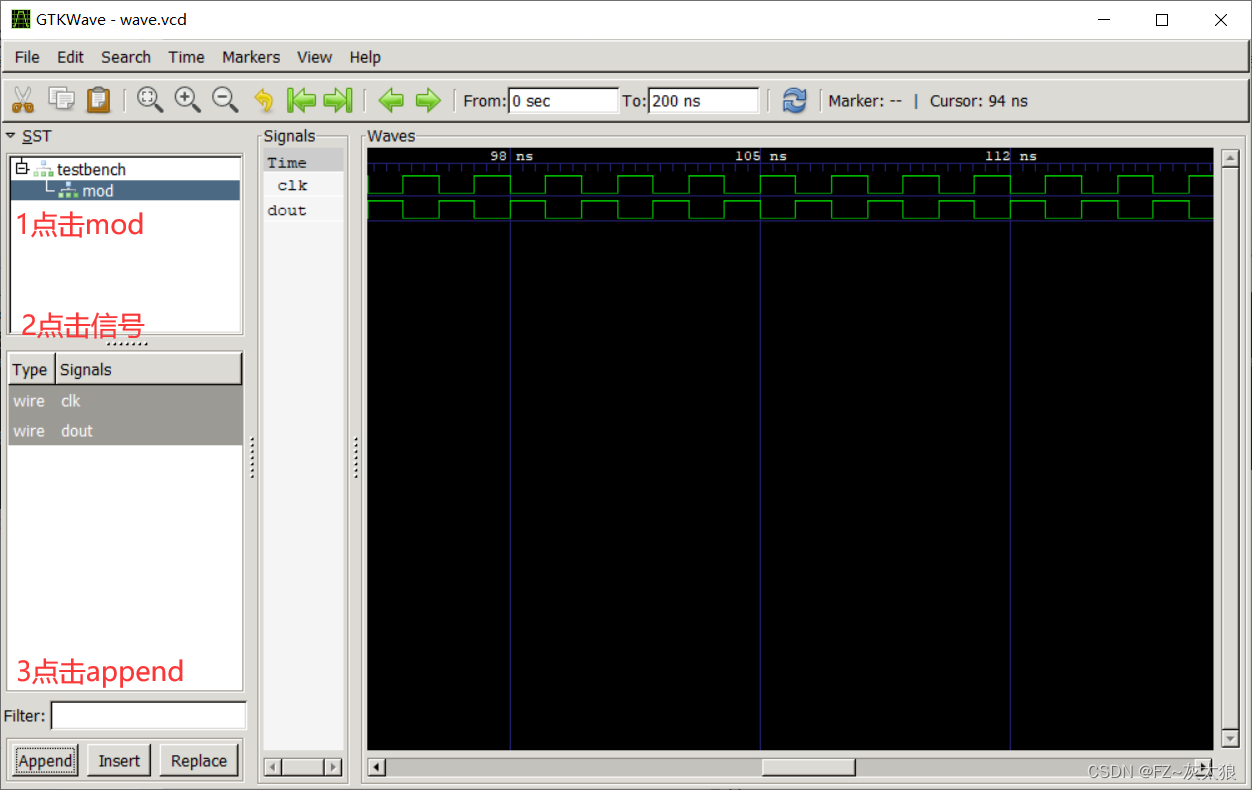

3、步骤

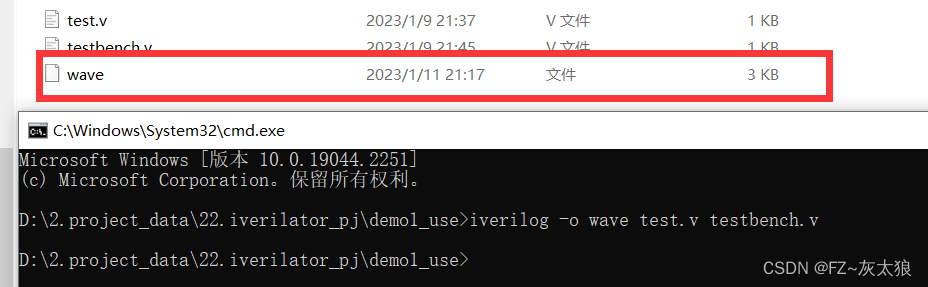

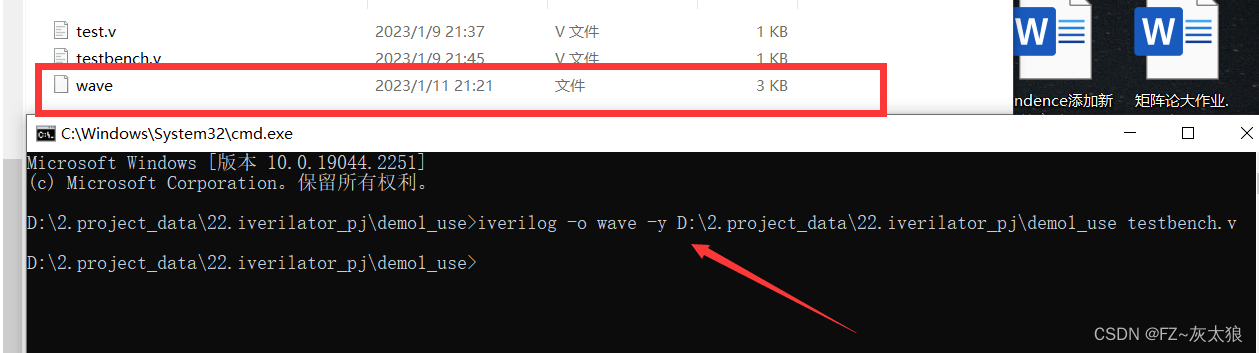

a.下面两种编译方式均可。

使用了-y [文件绝对路径]

b.生成波形文件

c.绘制波形图

**

快捷操作:1、命令行可以使用tab键快速补全文件的名称;

2、命令行中可以使用上下键切换曾经使用的命令。

**

总结

happy去吧!!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?