本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

一、 FPGA&CPLD 的下载

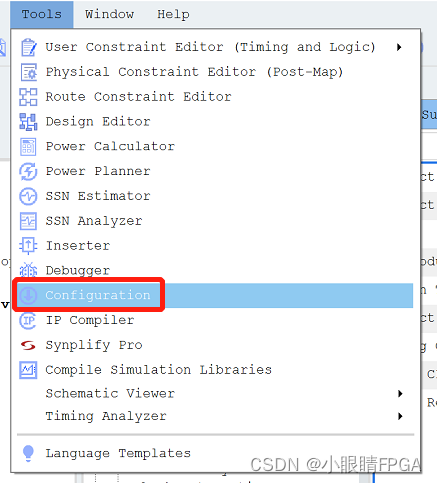

(1)生成位流文件(.sbit)后,可以把.sbit 文件下载到 FPGA 或 CPLD 中,首先将 JTAG 下载器与 PCB 板连接并上电,点击菜单栏中【tools】 下的【Configuration】。

Configuration

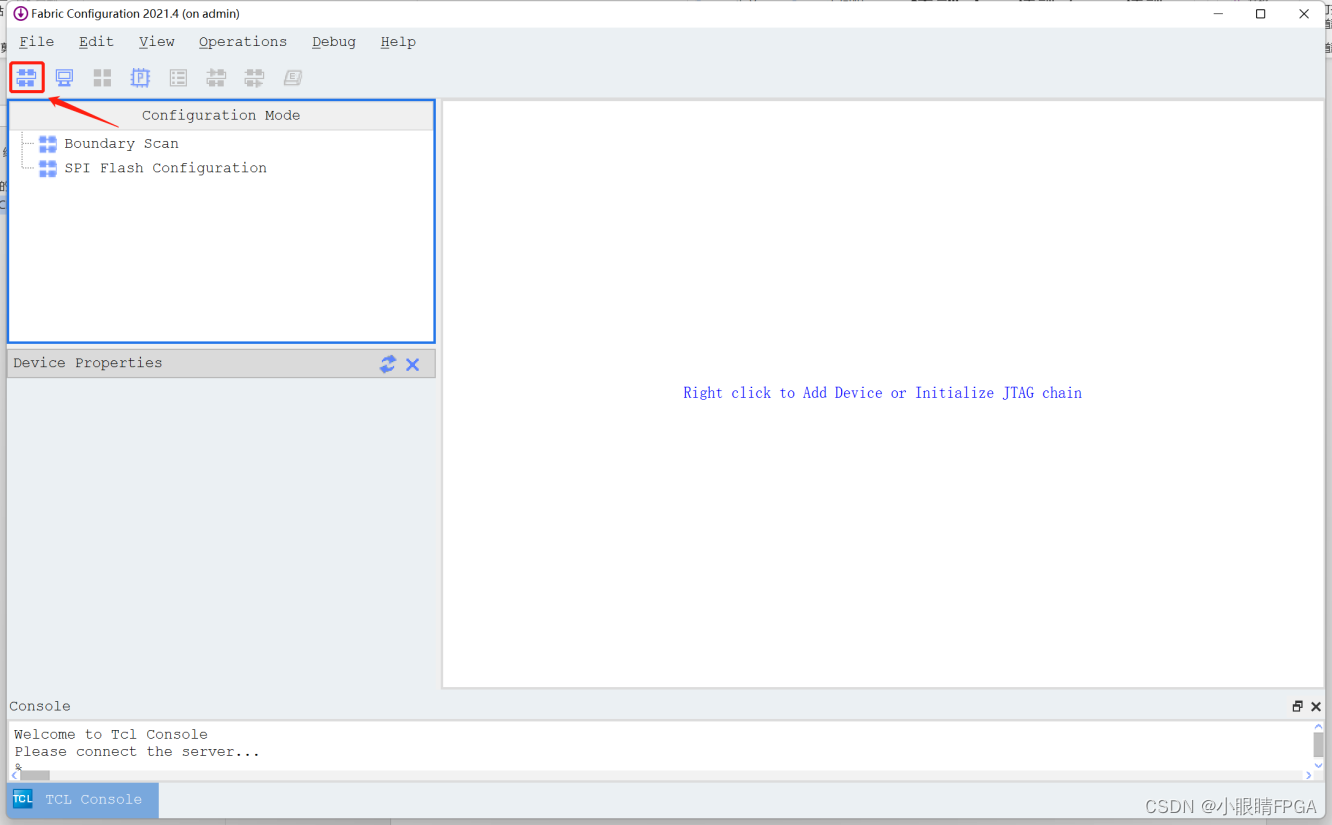

(2)在弹出的界面中单击【Scan Devive】。

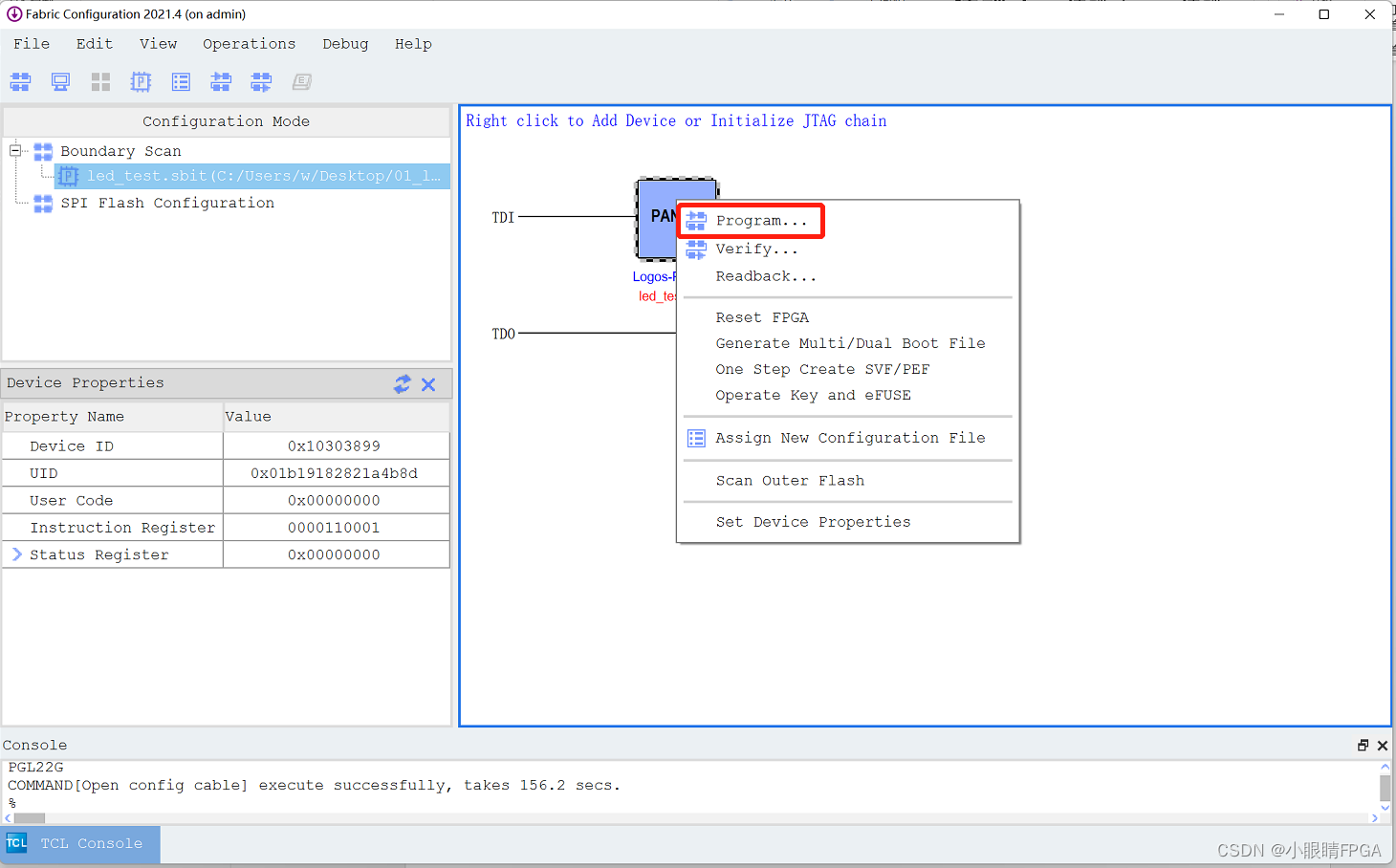

(3)在扫描到器件后,会弹出加载.sbit 文件界面,按要求添加即可。

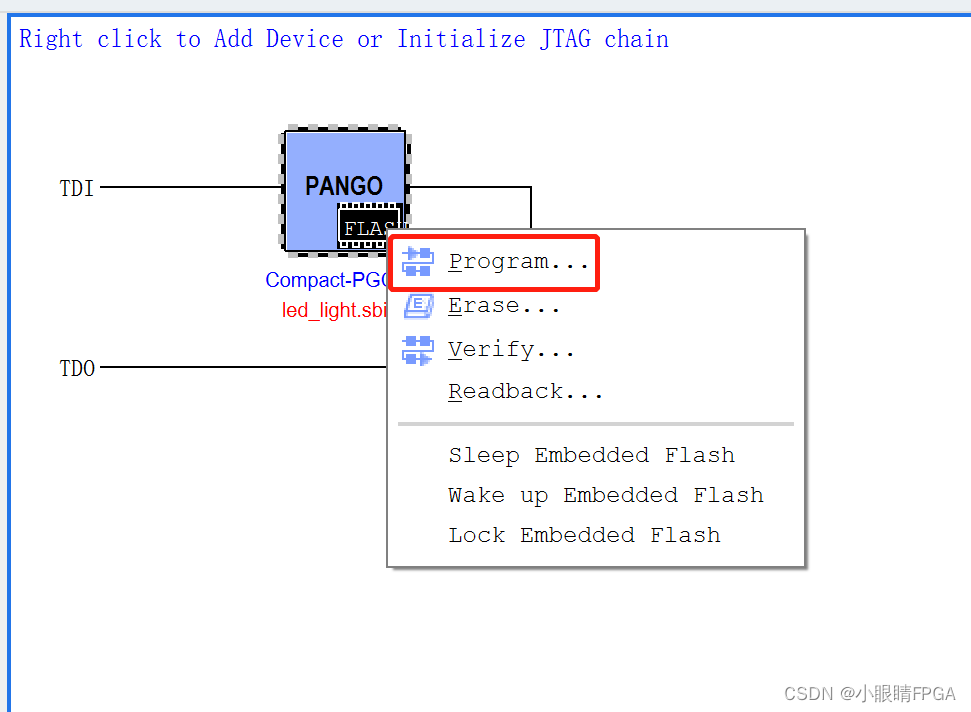

(4)添加好.sbit 文件后,选中器件并右击,在弹出的菜单中选择【Program】。

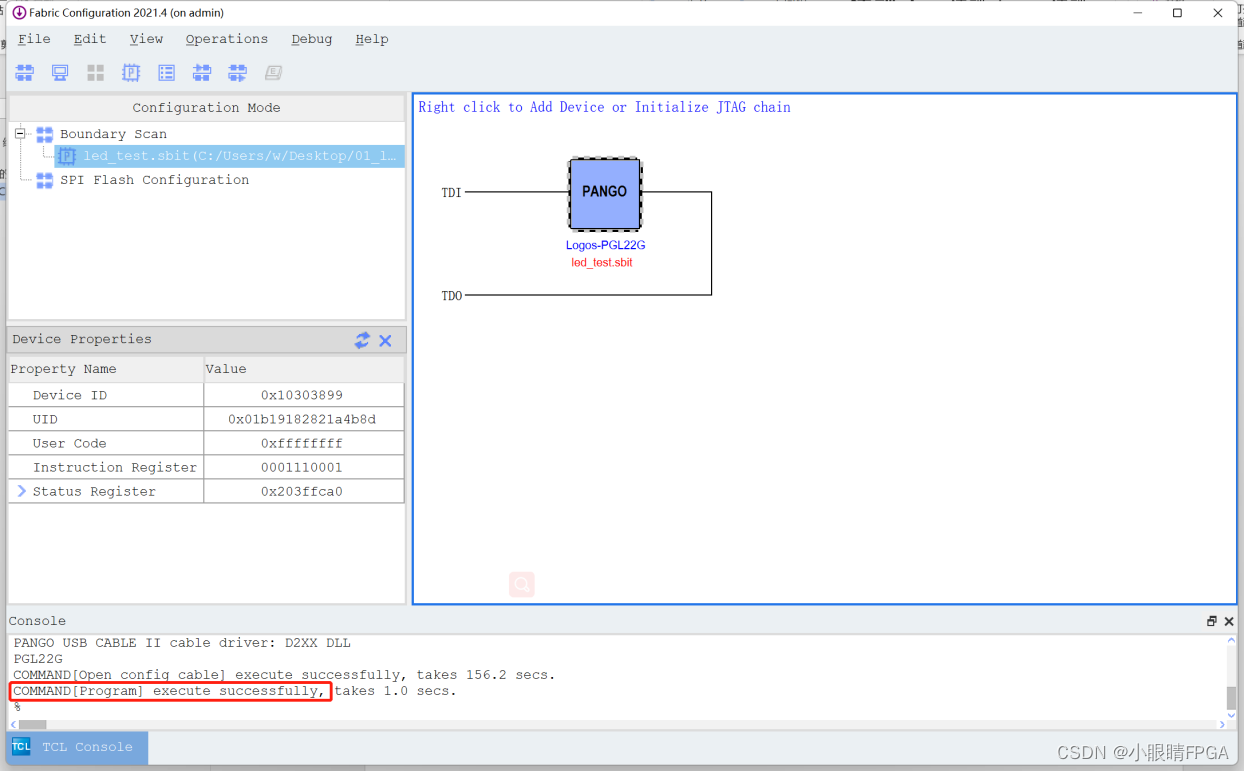

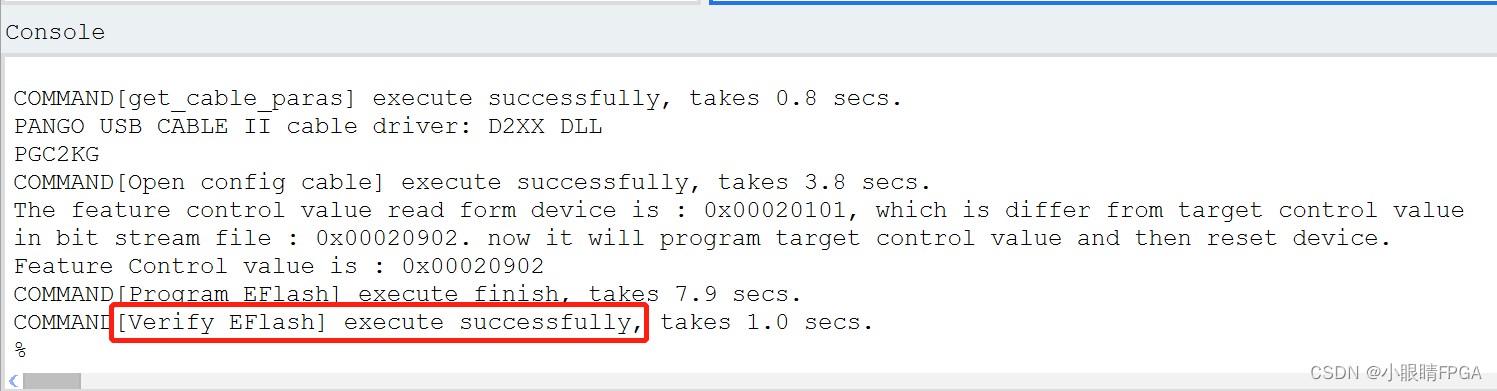

(5)信息区:显示“COMMAND[Program] execute successfully..”即已完成 FPGA 或 CPLD 的下载。

二、FPGA 的 Flash 固化

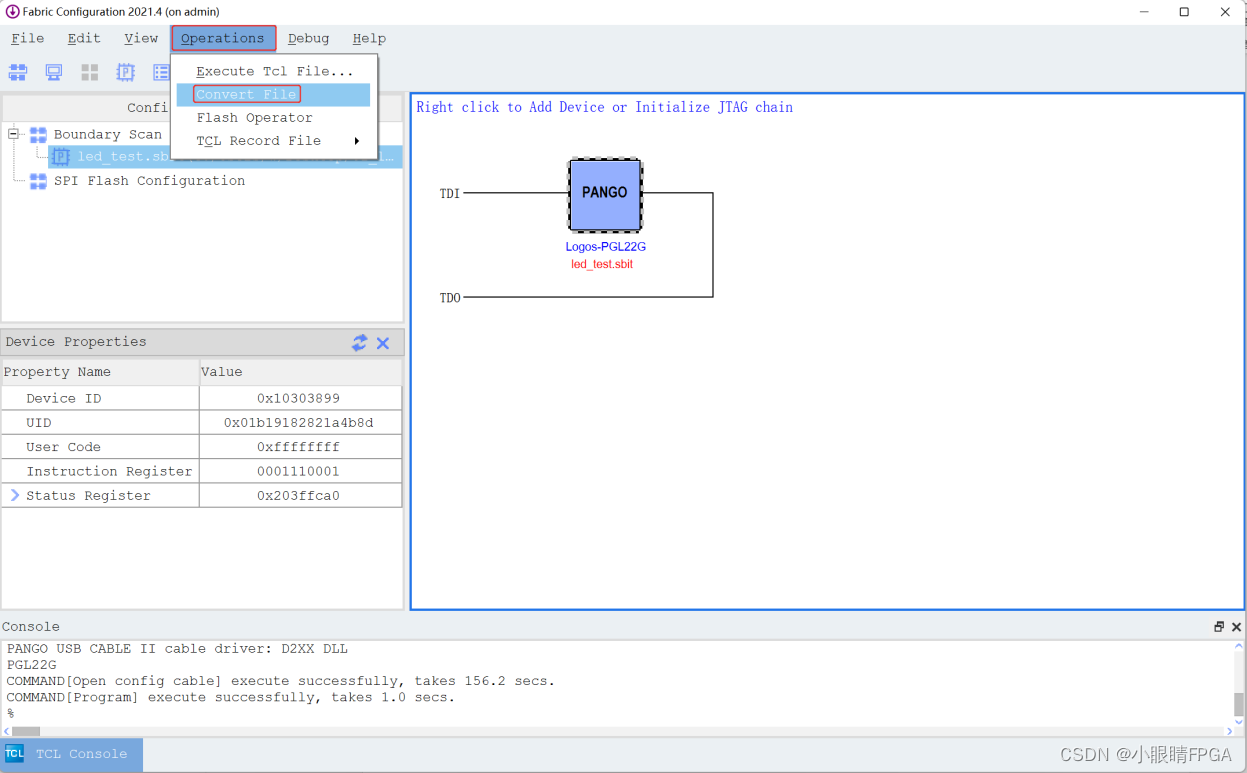

(1)FPGA 的 flash 固化需要先将.sbit 文件转换成 flash 的.sfc 文件。点击菜单栏的 【Operations】选择【Convert File】。

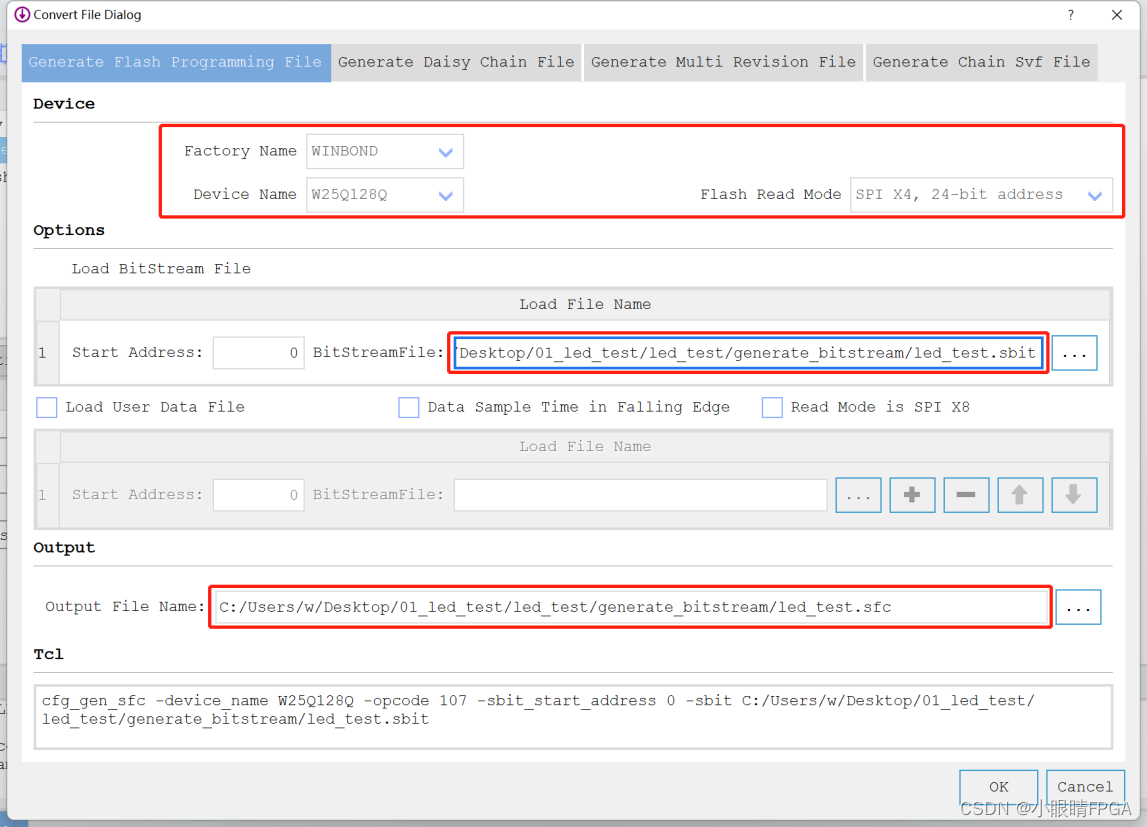

(2)在弹出的界面中,根据使用的 flash 型号选择厂家和设备型号,选择要转换的.sbit 文件,自动显示.sfc 文件位置,点击 OK。

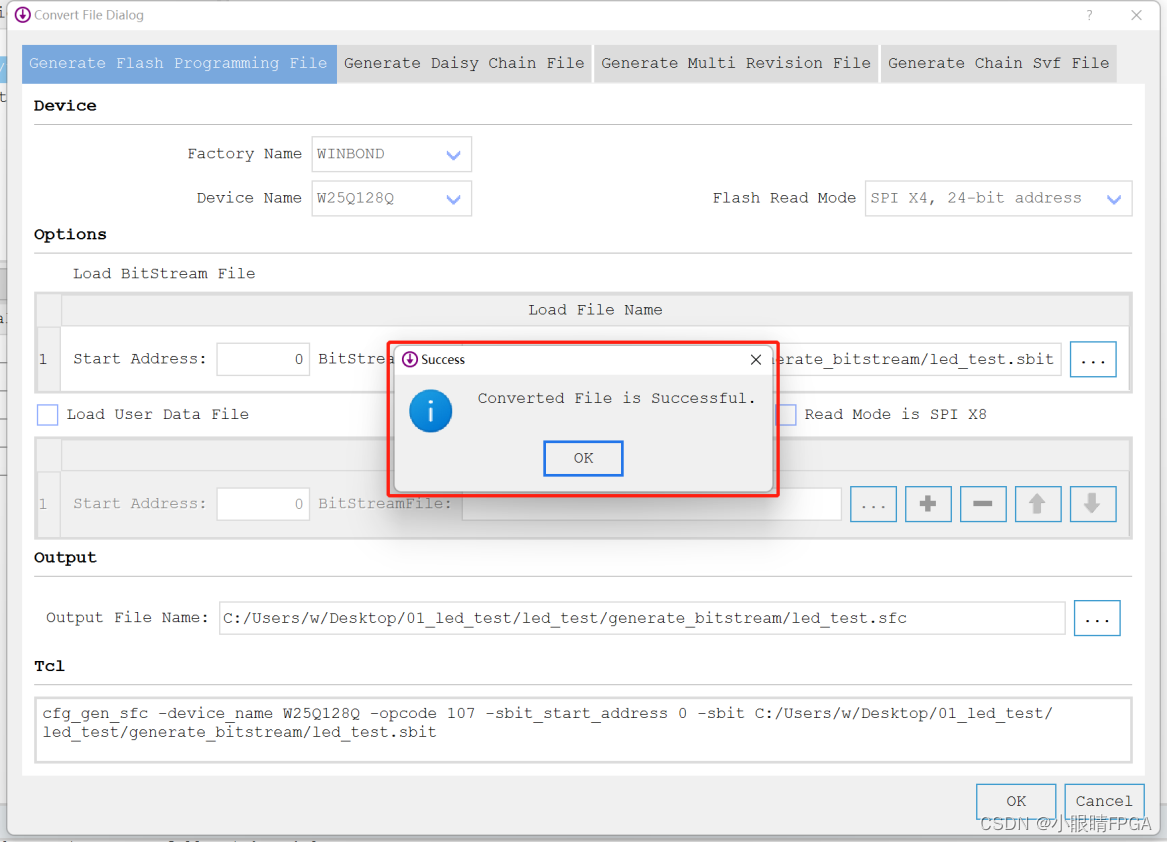

(3)转换成功后,显示如下界面,点击 0K 退出:

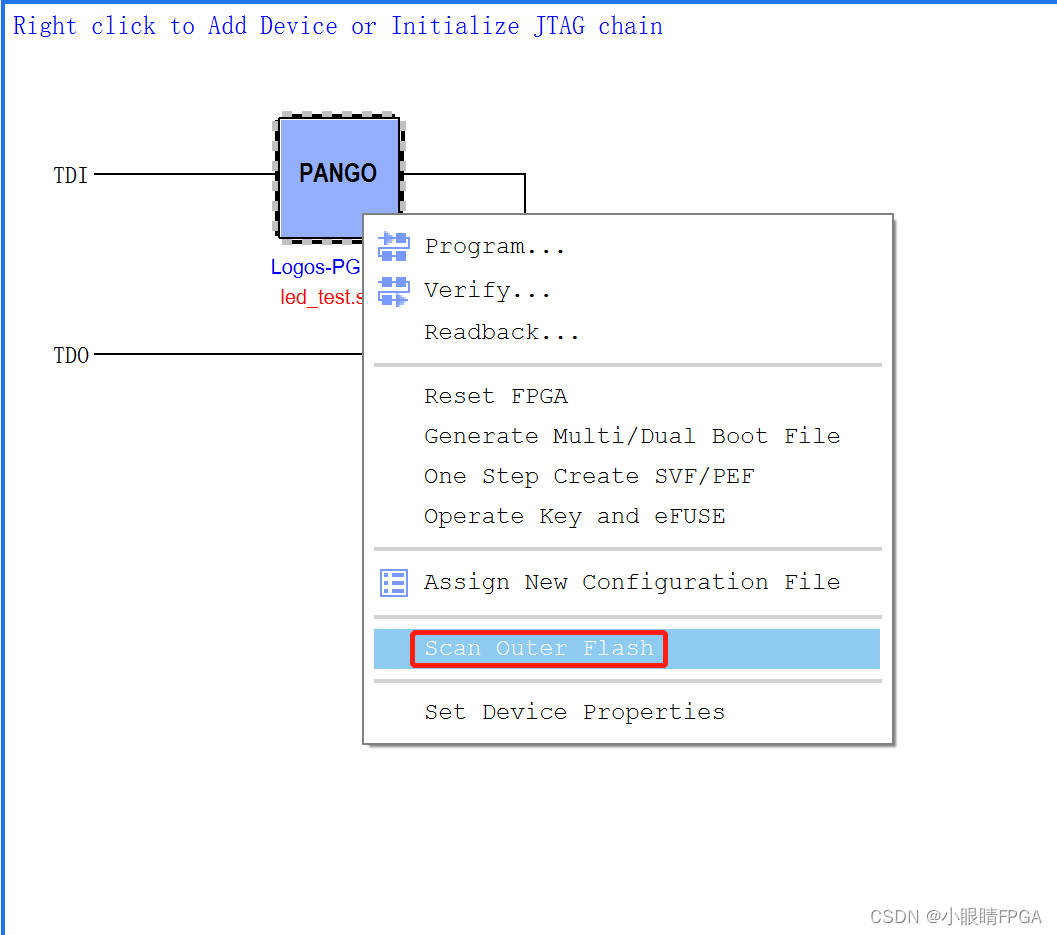

(4)选中器件右击,选择下拉菜单中的【Scan Outer Flash】

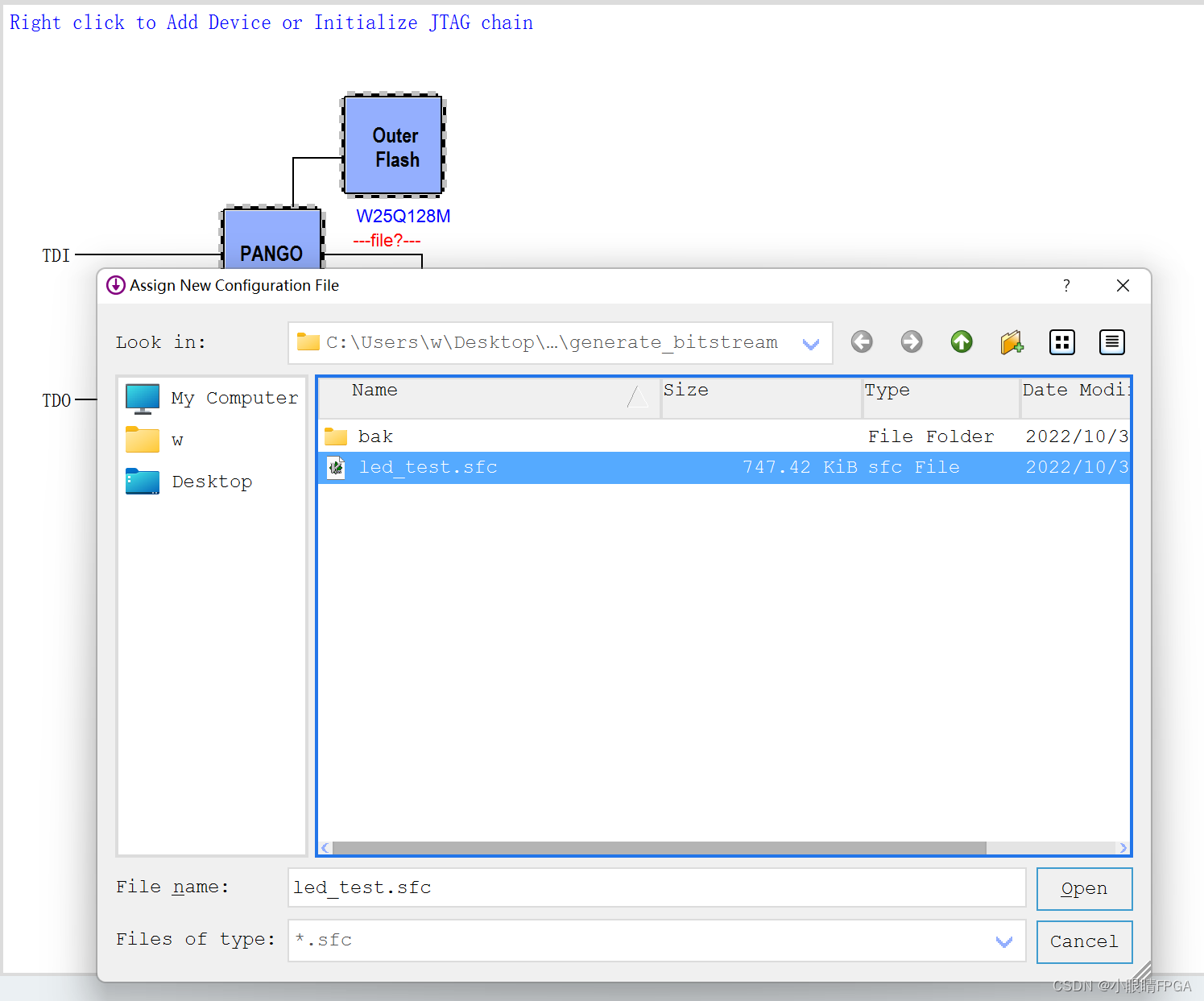

(5)在弹出的界面中选择.sfc 文件,点击【Open】

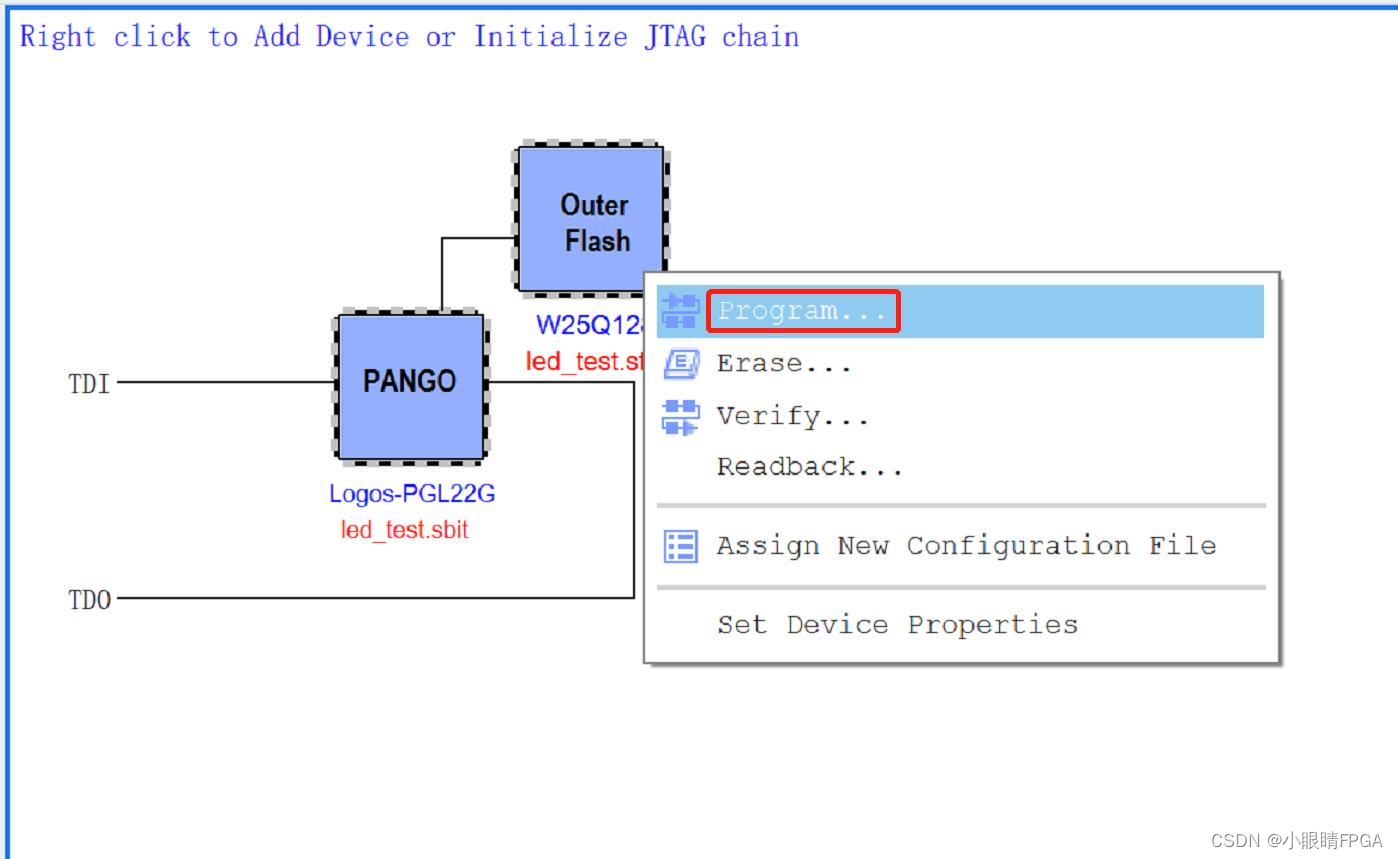

(6)右击【Outer Flash】,在下拉菜单中点击【Program…】

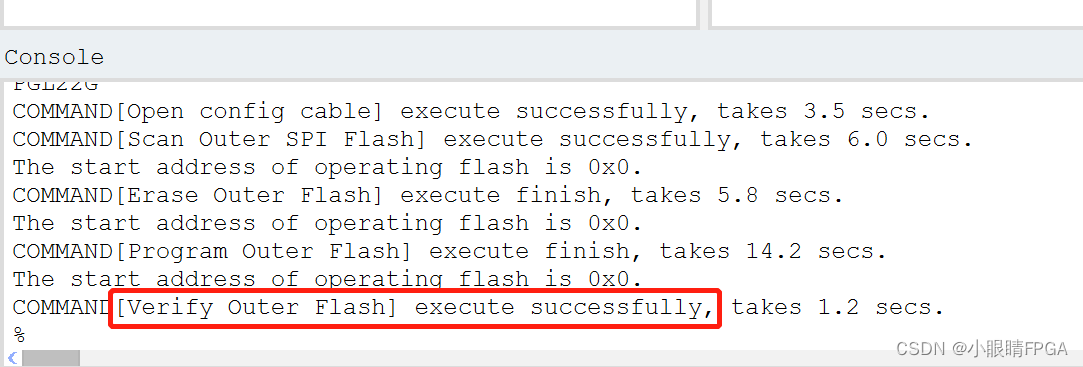

(7)进度条消失并出现下图,至此 FPGA 的 Flash 固化完成。

三、 CPLD 的 Flash 固化

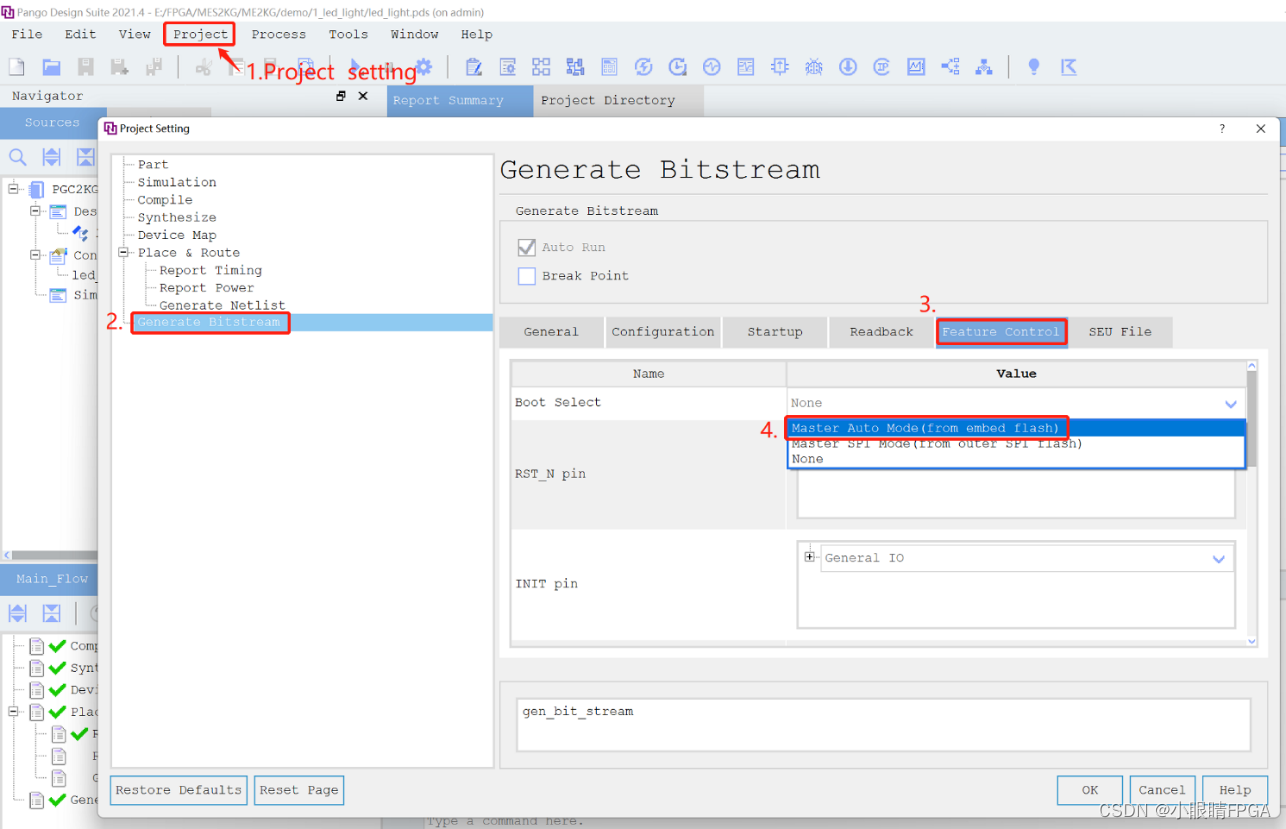

Compa 系列 CPLD 器件内置 eFlash,勿需外挂 Flash。首先按照下图设置 CPLD 器件的启动 方式【Master Auto Mode(from embed flash)】,重新生成新的位流文件.sbit。

(2)按照“1.FPGA&CPLD 的下载”流程进入到下载界面,选择新的.sbit 文件,右击器件 中的【Flash】,在下拉菜单中选择【Program】,等待进度条消失出现“[Verify Eflash]execute successfully…”,自此 CPLD 的 eFlash 固化完成;

1631

1631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?