本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

盘古PGX-MINI 4K开发板属于Compa系列的,此次就Compa系列CPLD器件展开介绍。

Compa系列器件是采用55nm工艺制造的低成本、高密度IO并具有非易失性的CPLD产品,采用先进的封装技术,提供上电瞬间启动功能;其中LUT4容量涵盖1300~9900;包括有专用存储模块(DRM),多样的片上时钟资源,多功能的I/O资源,丰富的布线资源,并集成了SPI、I2C和定时器计数器等硬核。Compact系列CPLD还支持多种配置模式,支持远程升级和双启动功能,同时提供UID Unique Identification)等功能以保护用户的设计安全。

Compa系列CPLD器件 包含G(通用型)、L(低功耗)和D支持主自加载双启动功能三种版本,支持两个速度等级5和6,其中6为最快等级。G型和D型器件支持外部供电电压VCC为2.5V或3.3V经过内部LDO电路产生内核电压,内核电压VCC CORE是1.2V L型器件只支持VCC为1.2V VCC CORE与VCC相同。CPLD器件的每个I/O Bank电源由其对应的VCCIO单独供电,支持1.2V、1.5V、1.8V、2.5V和3.3V。

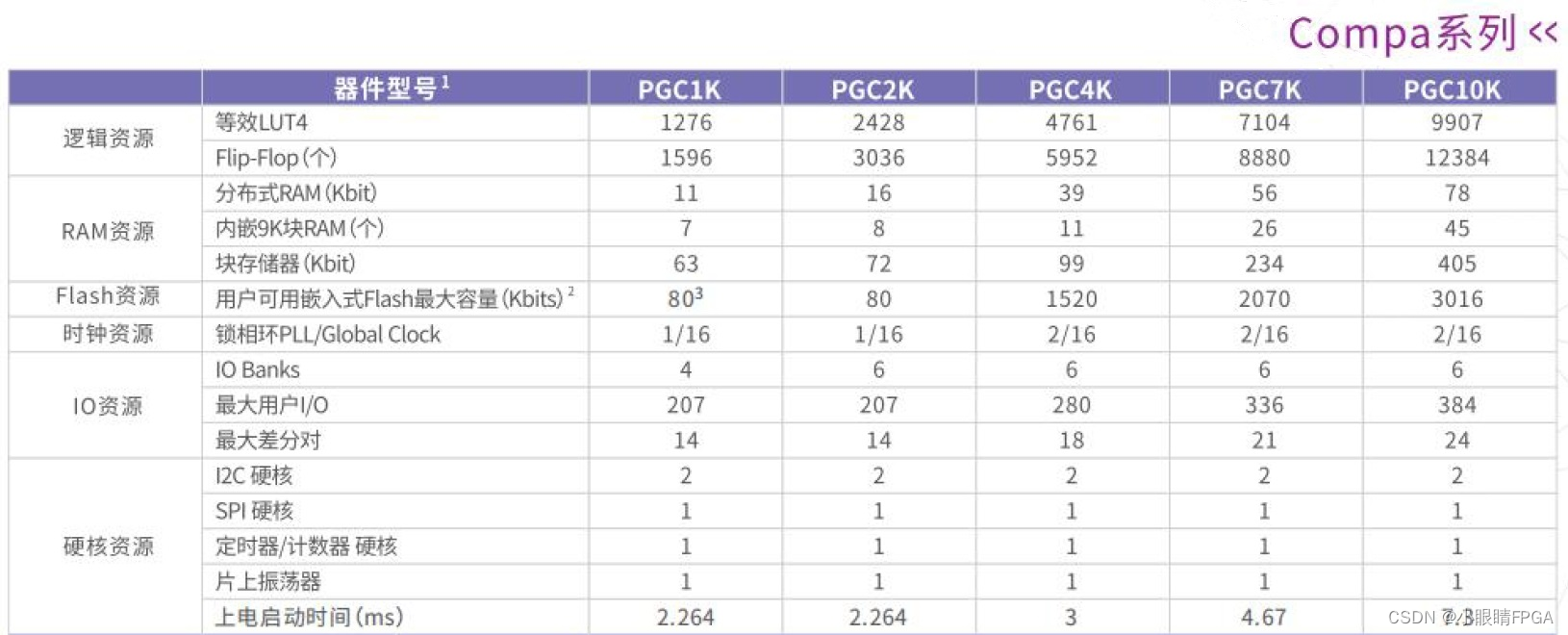

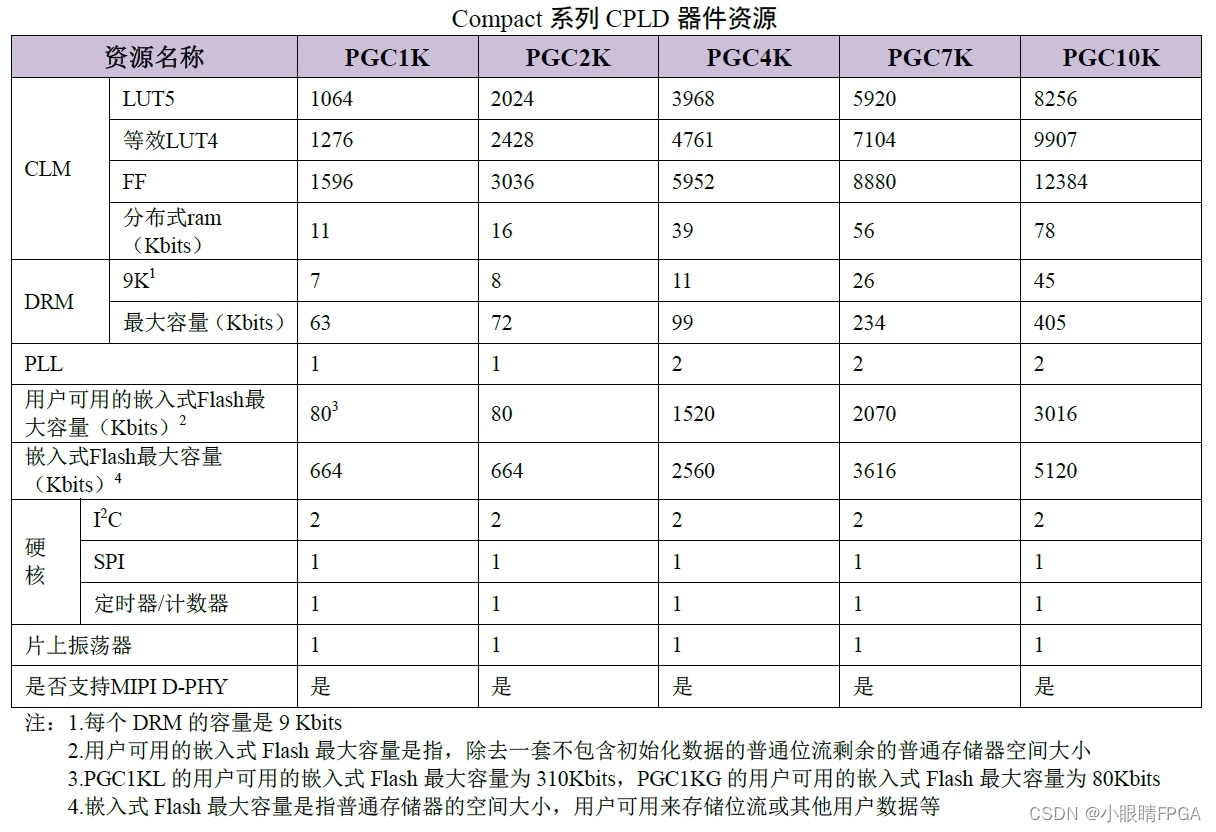

Compa系列CPLD器件的资源列表对比如下:

盘古PGX-MINI 4K开发板是一套基于紫光同创compa系列PGC4KD-6ILPG144芯片为核心的开发套件,支持主自加载双启动功能,集成板载jtag调试接口,预留两组20PIN扩展IO、数码管、按键、led灯等硬件资源,展示其优越性能。

时钟方面

Compa系列CPLD器件有最多8对专用时钟差分输入管脚,这些管脚可以接收差分输入信号也可以接收单端输入信号。当单端时钟信号接入时,使用差分信号的P端。作为时钟输入,这些管脚用来驱动时钟线,当这些管脚不需要驱动时钟线时,也可以作为通用I/O使用。全局时钟网络:支持8个全局时钟以及8个全局信号8个全局信号也可用作全局时钟使用。全局时钟可以为器件内的各种资源提供时钟,如CLM DRM和IO Logic。全局时钟支持400MHz的时钟频率。全局时钟支持时钟动态使能和动态切换功能。全局信号用来作为全局控制信号,如时钟使能信号,同步异步清零、复位或者输出使能信号。I/O时钟网络:有4个,BANK0和BANK2附近各有2个。时钟信号可以通过I/O时钟到达IO Logic作为信号的高速采样时钟。I/O时钟具有频率高(600MHz)和频偏小的特点。I/O时钟支持动态使能的功能。

PLL

Compa系列CPLD器件最多有2个PLL。PLL是CPLD提供时钟资源的核心子系统,主要功能有时钟频率综合,降低时钟偏移,调整时钟相位以及低功耗管理等。

PLL的输入时钟支持从外部I/O输入和内部互联输入时钟。支持两个输入时钟进行动态切换。PLL的反馈时钟支持从外部I/O输入和内部互联输入。

PLL支持多个时钟输出,每个时钟输出具有独立的分频器,支持1-128分频;每个时钟输出可以级联,PLL之间也可以级联;每个时钟输出具有可选的动态时钟使能控制;PLL还支持精度为16位的小数分频时钟输出,可以让用户产生非整数的输出时钟。

PLL支持静态配置和动态控制时钟相位两种方式。其中,动态调节PLL的相位时,可以用APB接口改写,或者通过端口来控制。PLL可以动态连续实现相位逐渐递增或者递减,且相位调节过程中,被调节的时钟输出没有毛刺。

PLL支持待机(Standby模式,即在设计中不需要用到PLL时,可以让PLL处于下电状态,以节省功耗。PLL支持用户通过APB接口对PLL工作参数进行动态地改变,为用户动态配置PLL提供另一种方式。

693

693

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?