- 路由器微体系结构

路由器微体系结构

路由器的设计必须能够在有限的面积和功率限制下满足延迟和吞吐量要求;随着多核系统规模的扩大,这是设计人员面临的主要挑战。路由器的复杂性随着带宽需求的增加而增加;当不需要高吞吐量时,可以构建具有低面积和功率开销的非常简单的路由器(无流水线、支持虫洞(译文中此处为不支持虫洞,但原文中应为支持虫洞路由,虫洞路由以flit为粒度分配buffer和带宽,面积开销较小)、无 VC、有限的小缓冲区)。当片上网络的延迟和吞吐量需求提高时,就会出现挑战。路由器的微架构决定了其关键路径延迟,这会影响每跳延迟和整体网络延迟。路由、流量控制和实际路由器流水线的实现会影响缓冲区和链路的使用效率,而缓冲区和链路控制着整体网络吞吐量。路由器微架构还会影响网络能量(动态能量和泄漏能量),因为它决定路由器中的电路组件及其活动。最后,微架构和底层电路直接影响片上网络的面积开销。

6.1 虚拟通道路由器微体系结构 VC Router MicroArchitecture

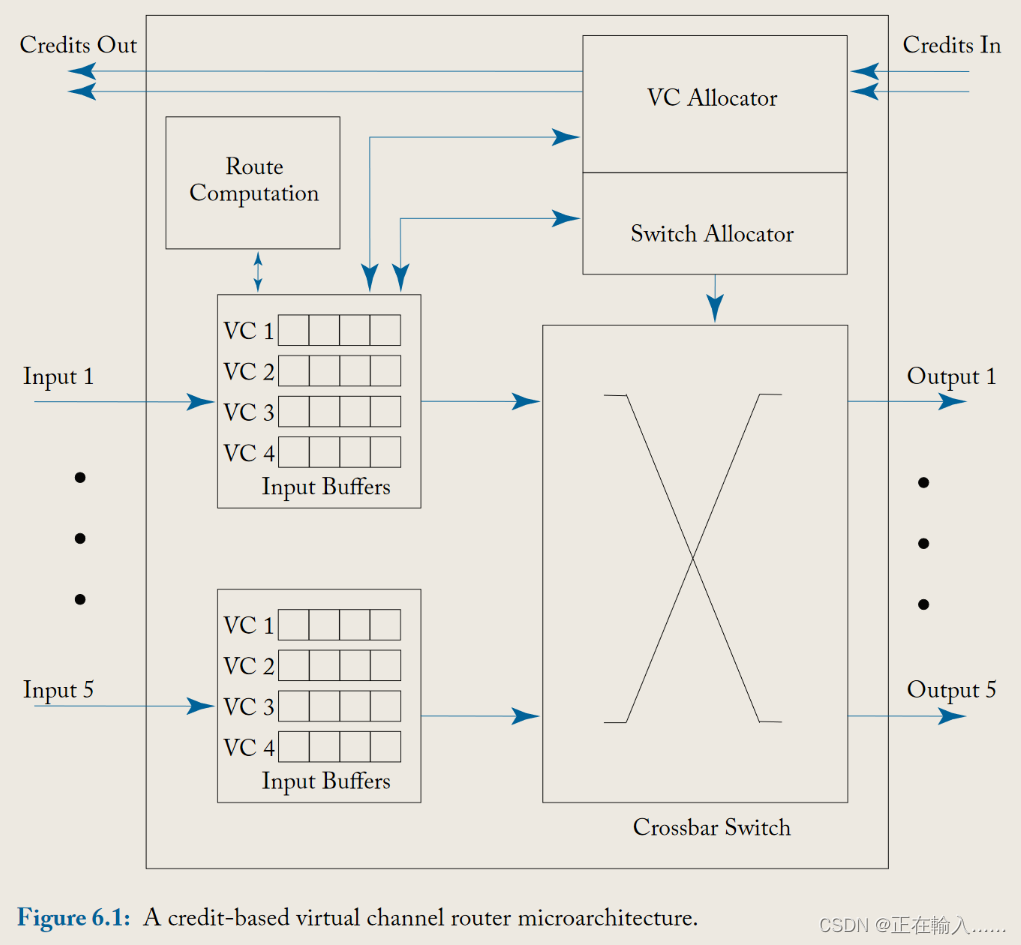

图 6.1 显示了当时最先进的基于信用的虚拟通道 (VC) 路由器的微体系结构,以解释典型路由器的工作原理。该示例假设为 2-D Mesh,因此路由器有五个输入和输出端口,分别对应于四个相邻方向和本地处理元件 (PE) 端口。构成路由器的主要组件是输入缓冲器、路由计算模块、虚拟通道分配器、交换机分配器和交叉开关。大多数片上网络路由器都在输入端设置了缓冲区。数据包经过输入存储在输入端口的缓冲区中。假设每个输入端口有4 个 VC,每个 VC 都有自己的 4 个 flits 深度的缓冲区队列。

缓冲区负责在flit进入路由器时存储它们,并在它们在路由器期间进行存储。如果不使用源路由,路由计算模块将计算(或查找)该数据包的正确输出端口。分配器(虚拟通道分配器和开关分配器)确定选择哪些 flits 进入交叉开关以及从什么端口进出交叉开关。最后,交叉开关负责将flit从输入端口物理移动到输出端口。在接下来的几节中将讨论路由器内部的各种组件。

6.2 缓冲区和虚拟通道 buffer and vc

当数据包或flit无法立即转发到输出端口时,缓冲区用于容纳数据包或flit。 Flits 可以在输入端口和输出端口上进行缓冲。当交换机的分配速率大于通道的速率时,会发生输出缓冲。交叉开关加速(第 6.3.2 节中讨论)需要输出缓冲,因为多个 flits 可以在同一周期中分配给单个输出通道,所以也需要输出端口的缓冲区。

所有先前提出的片上网络路由器都在输入端口处具有缓冲区,因为输入缓冲器组织允许面积紧凑和功率高效的单端口存储器。因此,我们将在这里重点讨论采用了输入缓冲的路由器,剖析如何在每个输入端口内组织此类缓冲。

6.2.1 缓冲区的组织方式

缓冲区的组织方式对网络吞吐量有较大影响,因为它在很大程度上影响着数据包共享链路带宽的效率。

-

单输入定长队列

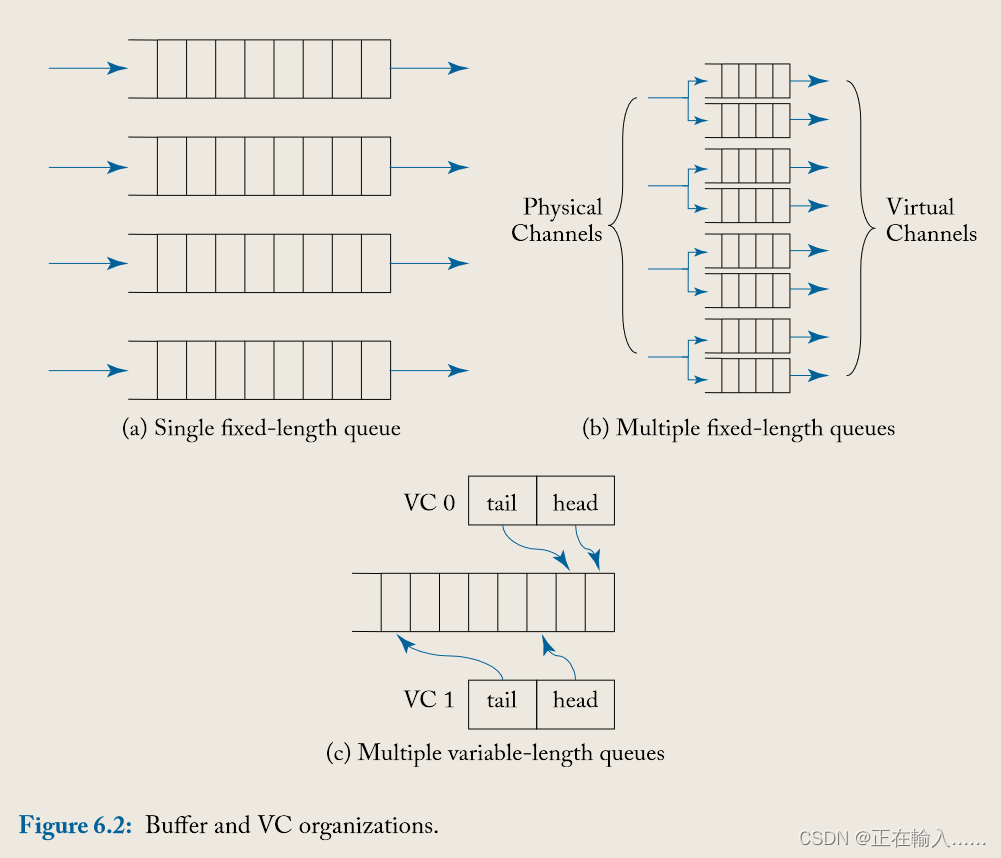

图 6.2a 显示了一个输入缓冲路由器,其中每个输入端口中有一个队列,即没有 VC。传入的flit被写入队列的尾部,而队列头部的flit被读取并通过交叉开关发送到输出链路(当它赢得仲裁时)。单个队列具有固定长度,因此上游路由器可以跟踪缓冲区可用性并确保仅当下游有空闲缓冲区时才转发 flit。

而单个队列极可能会导致队列头部的数据包被阻塞(因为其输出端口被另一个数据包占用),而队列中较靠后且输出端口可用的数据包无法前进。因为它必须等待队列的头部被发送。这种不必要的阻塞称为队头阻塞(head of line blocking)。

-

多输入定长队列

每个输入端口有多个队列(VC)有助于缓解队头阻塞。每个队列都称为虚拟通道,多个虚拟通道复用并共享物理通道/链路带宽。图 6.2b 显示了一个输入缓冲路由器,其中每个输入端口中有两个单独的队列,对应于具有 2 个 VC 的路由器。 -

多输入变长队列

在上面的缓冲区组织中,每个 VC 都有一个固定长度的队列,大小为图 6.2b 中的 4 个 flits。如果流量不平衡,则可能有一个 VC 已满,而当另一个 VC 为空时无法接受更多的 flits,从而导致缓冲区利用率较差,网络吞吐量较低。为了解决这个问题,每个 VC 队列可以是可变长度的,共享一个大缓冲区,如图 6.2c 所示。这允许更好的缓冲区利用率,但是以更复杂的电路为代价来跟踪队列的头部和尾部。另外,为了避免死锁,需要为每个 VC 保留一个 flit 缓冲区,这样其他 VC 就不会填满整个共享缓冲区,从而确保数据包能够向前传递。

-

最小虚拟通道数量

VC 在 NoC 中有两个用途:避免死锁(协议或路由)和提高性能。对于前者,需要一定数量的 VC 来避免协议死锁(例如共享内存一致性协议中的请求与响应需要在不同的通道中传输)。这些 VC 通常称为虚拟网络(Virtual Network)。在每个虚拟网络中,可能需要额外的 VC 来充当逃逸 VC,以避免路由死锁(即可能需要多个VC来构成虚拟网络)。除了这些必需的 VC 之外,还可以添加额外的 VC,以通过消除/减轻队头阻塞来提高性能。在每个端口的缓冲总量相同的情况下,设计人员可以选择使用数量多且深度小 VC 或使用数量少且深度大的 VC。更多 VC 进一步缓解队头阻塞,从而提高吞吐量。然而,它是以更复杂的 VC 分配器和 VC 缓冲区管理为代价的。在负载较小的流量模式下,数量多且深度小的 VC 将导致额外 VC 的利用率不足。在负载较大的流量模式下,数量少且深度大的 VC 的效率会降低,因为数据包将由于缺少可用的 VC 而被阻塞。

-

最小缓冲区队列(虚拟通道)长度

为了确保功能正确性,路由器的每个虚拟通道至少需要一个缓冲区以避免死锁。这是因为两个不同 VC 中的数据包决不应该无限期地相互阻塞。除此之外,为了维持完整的吞吐量,需要有一定数量的缓冲区(在每个 VC 内或总共,取决于缓冲区组织)来覆盖缓冲区周转时间,这在第 5 章中讨论过。

6.2.2 输入虚拟通道状态

每个虚拟通道都与其中的 flits 有以下状态。

- 全局 (G):空闲状态/路由状态/等待分配输出 VC(下游路由器输入端口的虚拟通道)/等待输出 VC 的Credit返回/激活Active。avtive VC可以执行开关分配。

- 路由 ®:计算数据包的输出端口。该字段用于开关分配。输出端口在由 head flit 进行路由计算后填充。在具有前瞻路由(稍后将在第 6.5.2 节中描述)或源路由的设计中,头 flit 到达当前路由器,并且输出端口已指定。

- 输出 VC (O):该数据包的输出 VC(即下游路由器的 VC)。这是在头 flit 进行 VC 分配后填充的,并由数据包中的所有后续 flit 使用。

- Credit Count ©:输出端口 R 处的输出 VC O 中的 Credit 数量(即下游路由器的 flit 缓冲区)。该字段由 body 和 tail flit 使用。

- 指针 §:指向头部和尾部的指针。如果缓冲区被实现为多个可变长度队列的共享池,则这是必需的。

6.3 开关设计 Switch Design

路由器的交叉开关crossbar switch是路由器数据路径的计算核心。它执行路由器功能的本质:将数据包/flit从输入端口传输到输出端口。

6.3.1 交叉开关设计

高频和低功耗交叉开关的设计是 VLSI(超大规模集成电路)设计中的一个挑战,例如 Intel TeraFLOPs 芯片中使用的位交错或双泵定制交叉开关。这里仅提供一些基本交叉开关设计的背景知识,并讨论交叉开关的微架构组织。

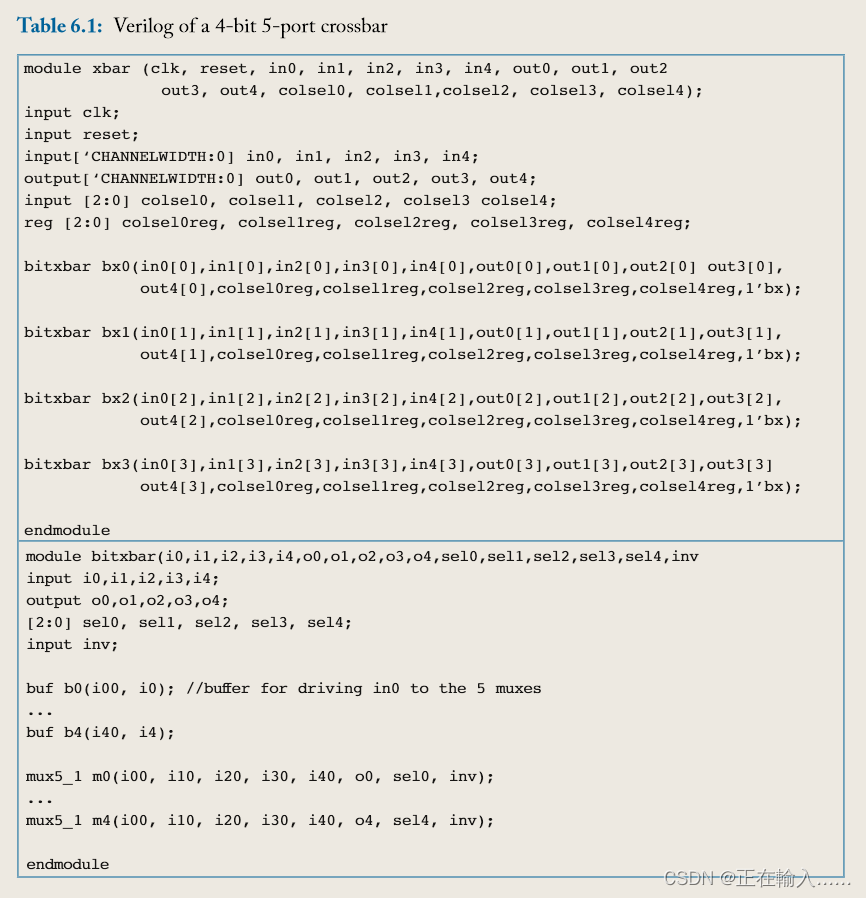

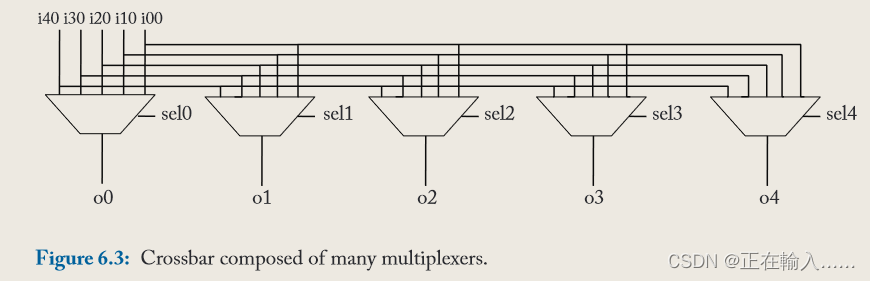

表 6.1 显示了描述crossbar switch的 Verilog 模块,其中每个多路复用器的输入选择信号(即图中的sel信号)设置哪个输入端口应连接到哪个输出端口。综合起来将得到一个由多个多路复用器组成的交叉开关,如图 6.3 所示。

大多数低频路由器设计将使用这种合成交叉开关。

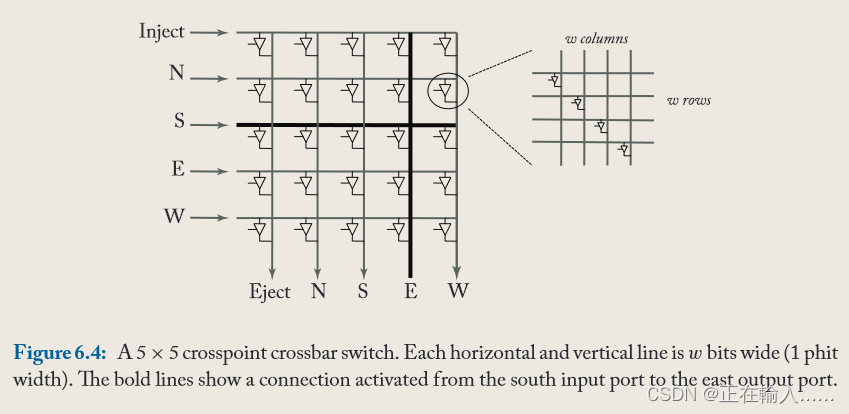

随着设计向 GHz 时钟方向发展并面临更严格的功率预算,往往会使用定制设计的交叉开关。如图 6.4 所示展示了基于交叉点的5x5的交叉开关,其中水平线和竖直线上的位宽均为w位(即传输一个phit所需的位宽),所以每个交叉点上有w个小开关,由选择信号控制。通过激活水平线S和垂直线E的交叉点处的开关,就可以激活南向东的连接,如图粗线所示。

无论采用哪种设计,交换机的面积和功率均为 O[(pw)^2],其中 p 是交叉开关端口的数量,w 是交叉开关端口宽度(以位为单位),从而影响数据包的能量延迟乘积(Energy-Delay Production, EDP),这是度量CMOS电路能量效率的常用指标。因此,设计时必须权衡q和w。

6.3.2 交叉开关加速

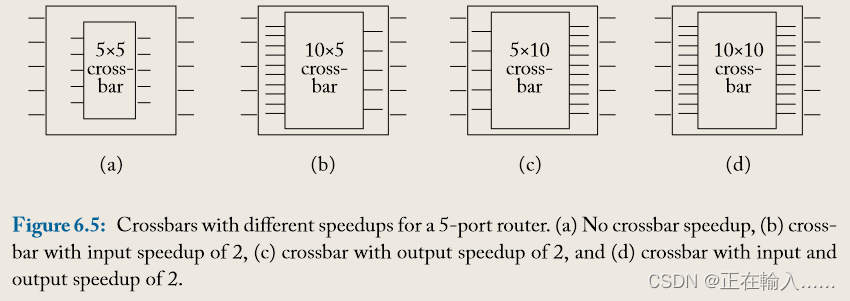

设计路由器微架构需要决定交叉开关加速比(crossbar speedup),即交叉开关中输入/输出端口的数量与路由器输入/输出端口的数量,其中输入端口之比称为输入加速比,输出称为输出加速比。

图6.5显示了具有不同加速系数的5个端口的路由器。分别为无加速比、输入加速比为2、输出加速比为2、输入输出加速比均为2。具有更高加速系数的交叉开关在路由器输入和输出端口之间提供更多的内部带宽,从而缓解分配问题并改善流量控制。

通常每个路由器的每个输入端口有多个虚拟通道,这些虚拟通道竞争同一个输入端口,如果提高加速比使每个VC都有专用的交叉开关输入端口,那么就可以省去复杂的竞争仲裁电路,简化资源分配(资源通常指VC和交叉开关端口)。数据流控制也将得到改善。

图b中输入加速比为2的交叉开关使用简单的分配器,也将实现接近 100% 的吞吐量。通过提供更多输入端口可供选择,每个输出端口在每个周期匹配(使用)的可能性更高。使用输出加速允许每个周期将多个 flit 发送到同一输出端口,从而减少争用。因此具有输出加速功能的交叉开关需要输出缓冲区队列(即在输出端口处增加虚拟通道)来将 flits 复用到单个输出端口上。

也可以通过交叉开关实现比路由器其余部分更高的频率来实现交叉开关加速。例如,如果交叉开关的时钟频率是路由器频率的两倍,那么它可以在一对输入输出端口之间每个周期发送两个 flits,从而实现与输入和输出加速比为 2 的交叉开关相同的性能。但在片上网络中,这种实现过于精细和激进。

6.3.3 交叉开关切分 Slicing

由于交叉开关占据了路由器占用空间和功率预算的很大一部分,因此已经提出了许多旨在优化交叉开关功率性能的微架构技术。

在二维 Mesh中对交叉开关进行维度切分,使用两个 3x3 交叉开关替换一个 5x5 交叉开关,其中第一个交叉开关用于分配在 X 维度中的流量,第二个交叉开关用于分配在 Y 维度中的流量。方面。第一个交叉开关上的端口与第二个交叉开关上的端口连接,因此从 X 维度转向 Y 维度的流量会穿过两个交叉开关,而留在某个维度内的流量仅穿过一个交叉开关。这特别适合维度排序路由协议,其中流量大部分停留在一个维度内。

也可以采用w位的位交织交叉(bit interleaving)开关,即在每个线路上的一个时钟周期的两个相位上分别发送w位的一半,从而将位宽需求 w 减半。Intel TeraFLOPS 架构采用位交错技术,这将在第 8 章中讨论。

6.4 分配器和仲裁器 Allocators and Arbiters

在路由器中,存在多个flit竞争同一个资源的情况,比如多个输入虚拟通道的flit可能需要从交叉开关的同一个输入端口输入,但是没有优化的情况下,每个资源一次只能由一个flit使用。因此这种情况下需要裁判来决定哪一个flit可以使用资源。裁判就是分配器(allocator)/仲裁器(arbiter)。

分配器和仲裁器的输入是请求,输出是请求可以占用资源的批准。如在交叉开关输入端口的仲裁中:请求是路由器输入端口的多个输入虚拟通道,资源是交叉开关的输入端口。这个仲裁中的分配器/仲裁器的工作流程是:当有多个输入虚拟通道的flit想使用交叉开关的同一个输入端口时,这些虚拟通道会向分配器/仲裁器发送请求,分配器/仲裁器需要在这些请求中根据设定好的优先级判断方式仲裁和授予批准(分配器仲裁多个资源的多个请求,而仲裁器只仲裁一个资源的多个请求)。只有在仲裁中获胜的请求,即获得批准后,所对应的虚拟通道可以将flit送入交叉开关的输入端口,而未获得批准的请求等待下一轮仲裁。从多个竞争相同资源的请求中批准一个的过程叫“将请求匹配到资源”。

片上网络存在多个仲裁过程,不同的仲裁过程的请求和资源所代表的含义不同。

分配器将 N 个请求匹配到 M 个资源,而仲裁器将 N 个请求匹配到 1 个资源。在路由器中,资源是 VC(虚拟通道路由器)和开关交换机端口。

在没有 VC 的虫洞路由器中,每个输出端口的开关仲裁器负责将发出请求的输入端口匹配到这个输出端口。因此,存在 P 个仲裁器,每个输出端口一个,每个仲裁器将 P 个输入端口请求与争用的单个输出端口相匹配。

在具有多个 VC 的路由器中,我们需要一个虚拟通道分配器 (VA),用于解决输出虚拟通道的争用(即flit传输到下一跳路由器哪一个输入虚拟通道),并保证输出虚拟通道和输入虚拟通道相连接。同时需要一个开关分配器 (SA),用于将交叉开关端口连接到输入虚拟通道。只有数据包的头部 flit 需要访问虚拟通道分配器(之后的flit继承头部flit的路径),而开关分配器由所有 flit 访问,并逐周期授予对交换机的访问权限。

提供高匹配概率的分配器/仲裁器可为更多的数据包成功获得虚拟通道并通过开关交换机批准,从而导致更高的网络吞吐量。在大多数 NoC 中,路由器中的分配逻辑决定时钟周期长度(分配器和仲裁器逻辑往往是路由器的关键路径,从而决定了路由器的工作频率)。因此,分配器和仲裁器必须快速且可流水线化,以便它们可以在高时钟频率下工作。

6.4.1 round-robin 仲裁器

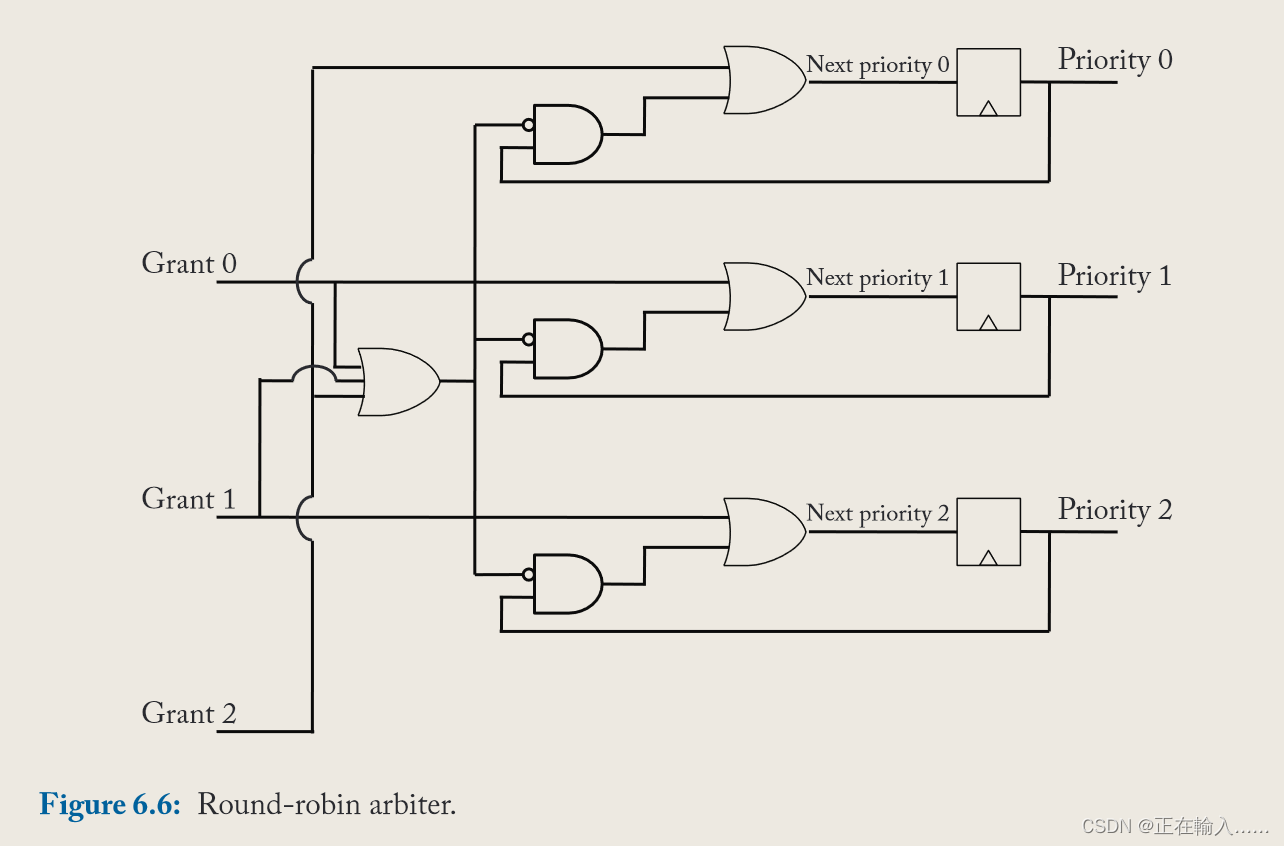

round-robin仲裁器:使最后赢得仲裁的请求下一轮仲裁中优先级最低,没有新请求时,原有优先级不发生变化。其中赢得仲裁的请求的批准信号为高电平,而下一轮的优先级由当前的批准信号计算而得。图 6.6 显示了round-robin仲裁器所需的电路。

如果当前i请求的批准信号是高电平,即i请求在这轮仲裁中赢得,那么i+1请求的优先级在下个周期变为高电平,并且所有其他请求优先级输出均为低电平。

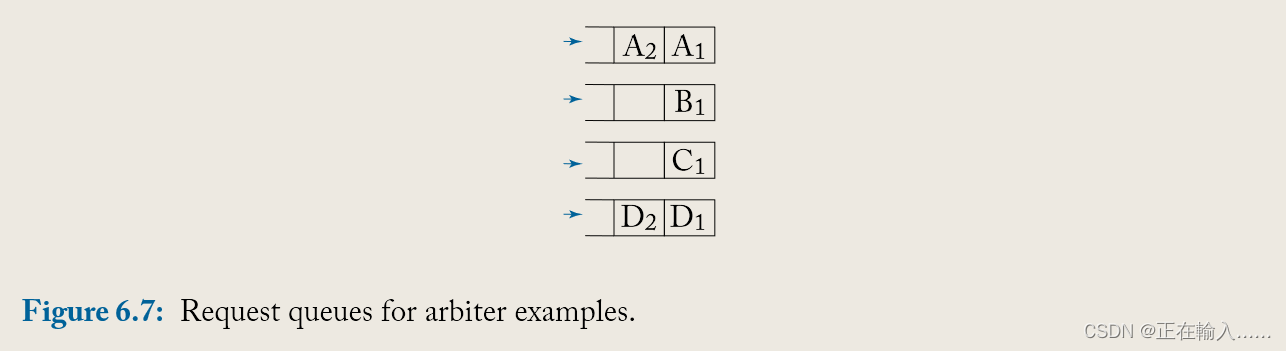

图 6.7 显示了来自 4 个不同请求者的一组请求。假设在这组请求之前服务的最后一个请求来自请求者 A。那么,B 在示例开始时具有最高优先级。使用循环仲裁器,请求按以下顺序满足:B1、C1、D1、A1、D2、A2。

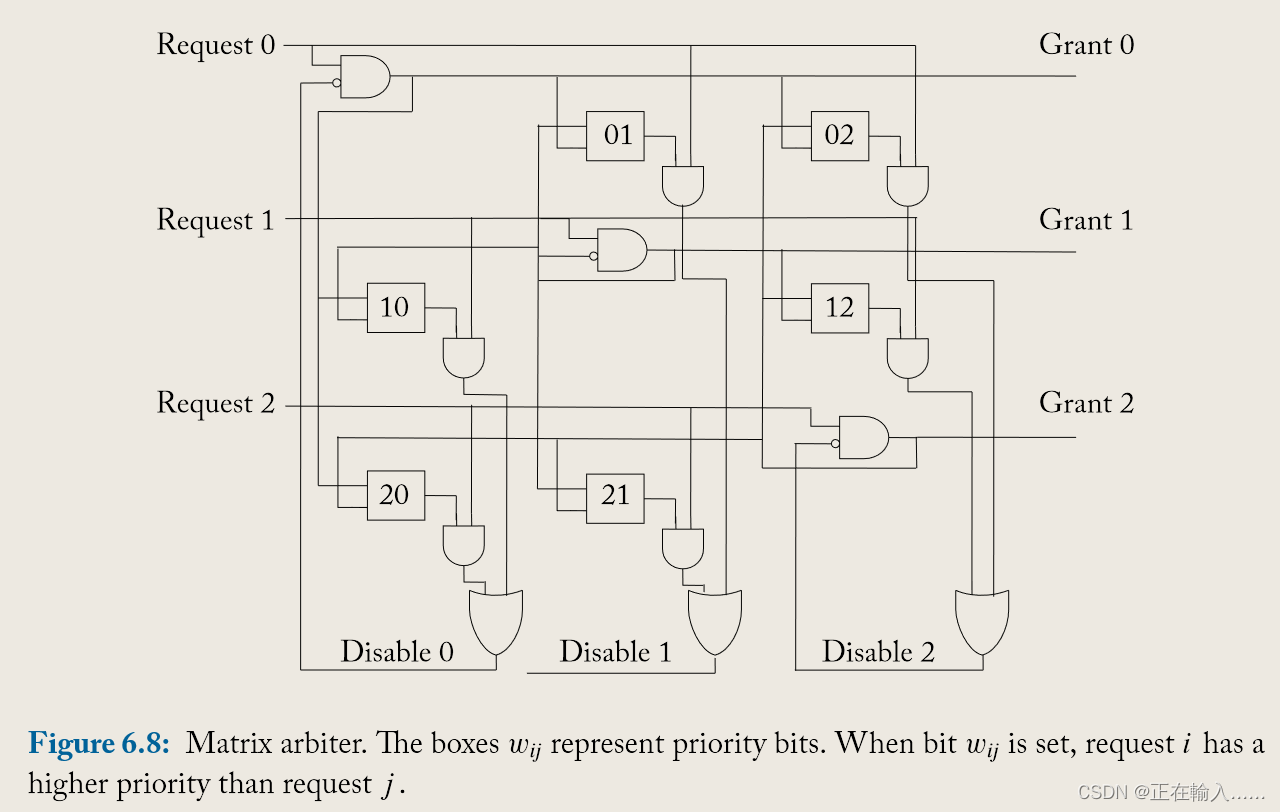

6.4.2 矩阵 仲裁器

矩阵仲裁器工作原理是使得最近最少服务的请求者具有最高优先级。

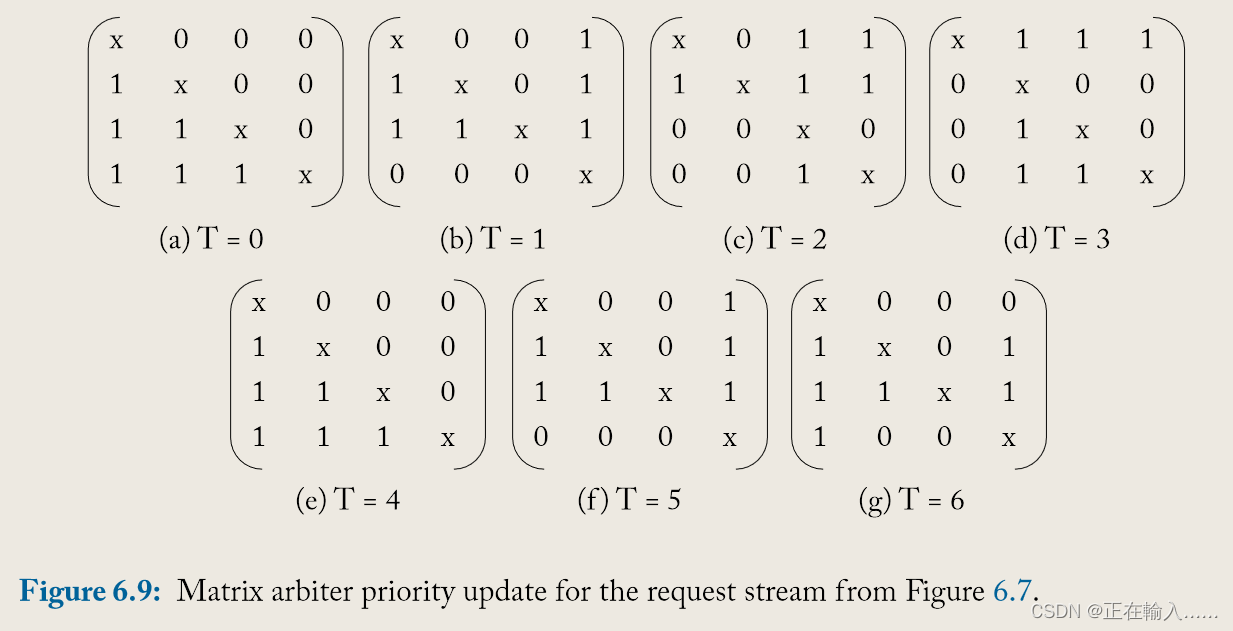

矩阵仲裁器的实现如图 6.8 所示,实现了一个能够处理4个请求的仲裁器,它使用图6.9所示的矩阵来记录这些请求的优先级顺序,在这个矩阵中第i行第j列的状态记为wij。当位 wij 被设置时(i小于j),请求 i 具有比请求 j 更高的优先级。当请求线被置位时,该请求与该行中的状态位进行“与”运算以禁用任何较低优先级的请求。每次授予请求 k 时,都会通过清除第 k 行中的所有位并设置第 k 列中的所有位来更新矩阵的状态。

从矩阵的初始状态可以看出,请求者 D 的优先级最高,其次是 C,其次是 B,最后是 A。这是因为 [1,0]、[2,0]、[3,0]、[2,1]、[3,1]和[3,2]均设置为1。在T=1时,授予D1。结果,第 4 行中的位被清除,第 4 列中的位被设置(图 6.9b)。 C 现在具有最高优先级。在 T=2 时,请求 C1 被授予,第 3 行被清除,第 3 列被设置,得到图 6.9c 中的矩阵。现在B具有最高优先级。继续以这种方式进行,最终的处理顺序为 D1、C1、B1、A1、D2、A2。

6.4.3 分离式分配器 SEPARABLE ALLOCATOR

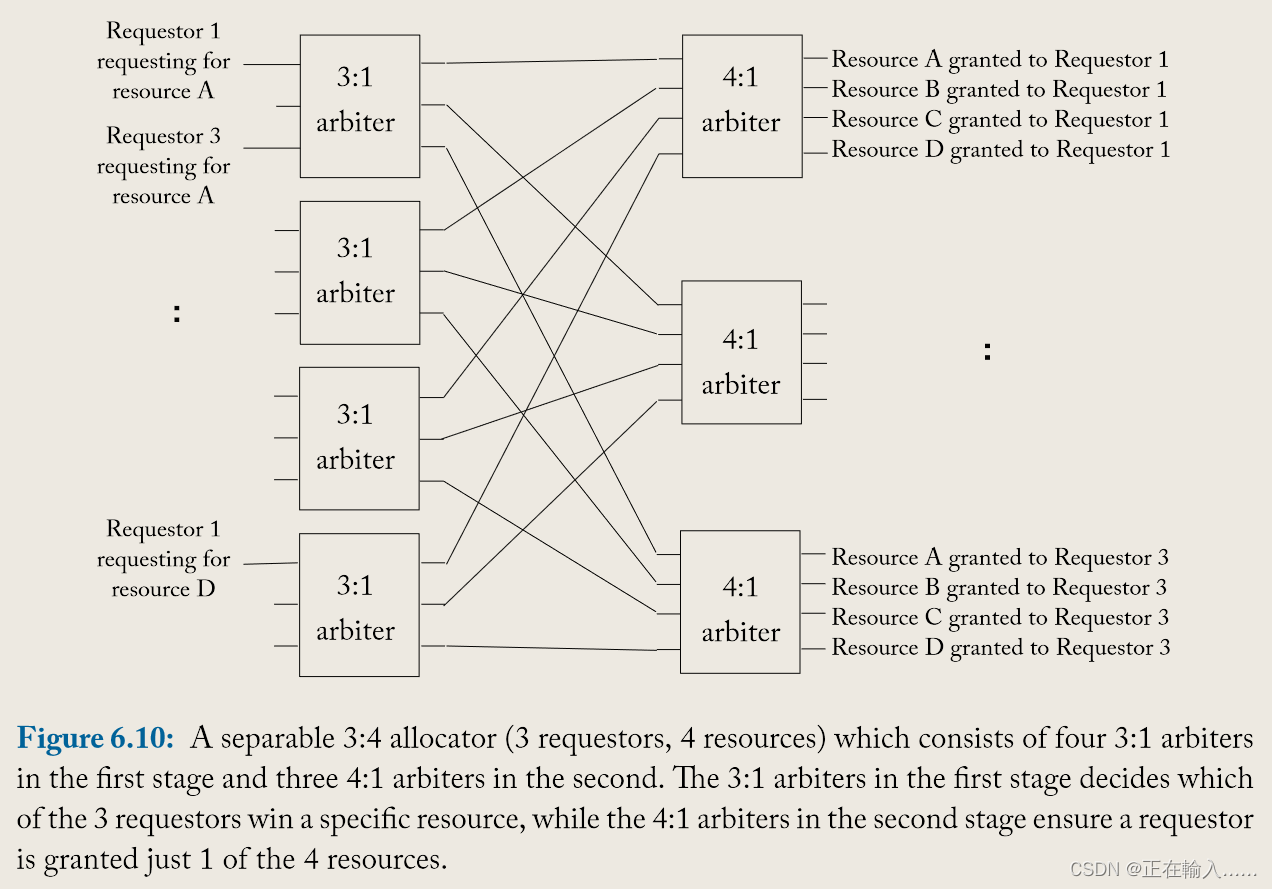

仲裁器是将多个请求中的一个匹配到某个资源。而分配器是处理多个资源多个请求,因此分配器的复杂性较高。为了降低分配器的复杂性并使其可流水线化,分配器可以构建为多个仲裁器的组合。仲裁器从对单个资源的多个请求中选择一个。例如,可以将一个 N:M 分配器替换为两级仲裁器(N为请求总数,M为资源总数)。其中第一级为M个K:1仲裁器,即从N个初始请求中获得N/M个请求;第二级为N/M个N/K:1仲裁器,即最多产生N/M个批准。K是具体设计决定的参数。

对于一个用于具有四个输入输出端口和每个输入端口3个 VC 的路由器的可分离交换机分配器,需要12:4的分配器。这个分配器可以分离为两级仲裁器。如图6.10所示,在分配器的第一阶段(由四个3:1仲裁器组成)选择vc,每个仲裁器对应一个输入端口,并选择三个输入VC中的一个作为获胜者。第一阶段获胜的 VC 随后在第二阶段(包括三个 4:1 仲裁器)仲裁输出端口。每个仲裁器从这些输入 VC 中选择一个作为输出端口的获胜者。实践中使用了不同的仲裁器,其中循环仲裁器round-robin由于其简单性而最受欢迎。

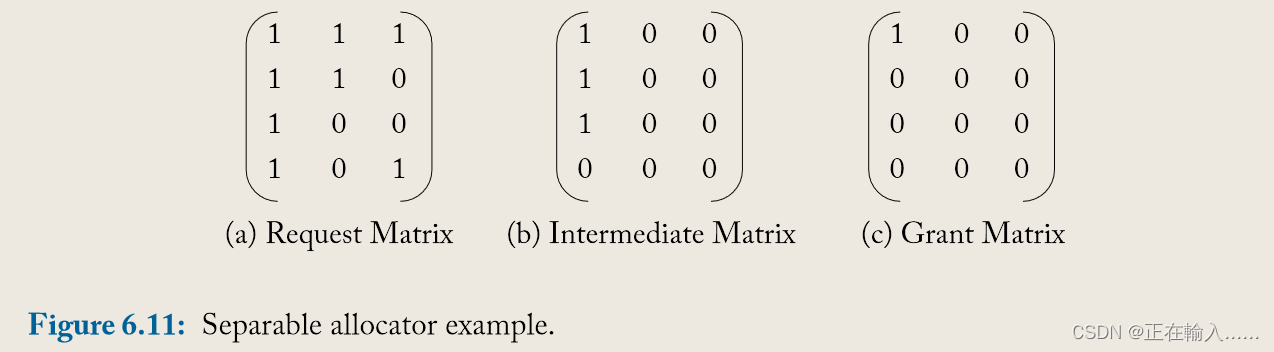

图 6.11 显示了可分离分配器的一个仲裁结果。图 6.11a 显示了请求矩阵。每个 3:1 仲裁器对应矩阵中的一行;分配器的第一阶段结果显示在图 6.11b 的矩阵中。第二组 4:1 仲裁器将在中间矩阵中设置的请求之间进行仲裁。最终结果(图 6.11c)显示只有一个初始请求被批准。

6.4.4 波前分配器 WAVEFRONT ALLOCATOR

可分离分配器面临的挑战通常是将请求与资源匹配效率低下,因为第一阶段不知道第二阶段的结果,第一级获胜的请求在第二级仍存在仲裁竞争。因此可以合并两级仲裁为一级以提高匹配率。波前分配器将整个分配作为一步执行,并且效率更高,同时可以在硬件中实现。

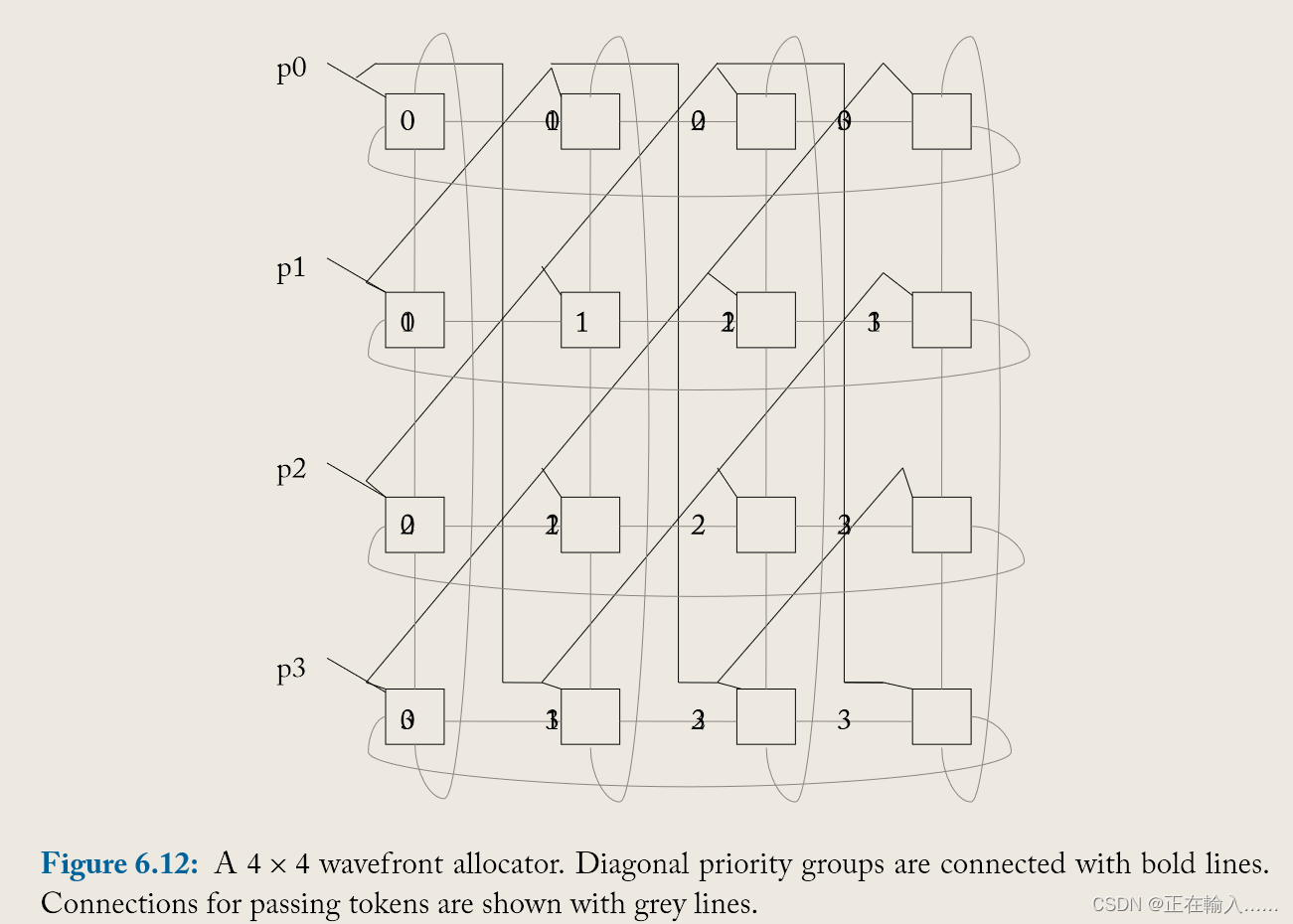

图 6.12 显示了 SGI SPI-DER 芯片 和 Intel SCC 中使用的 4x4 波前分配器。非方形分配器可以通过添加虚拟行或虚拟列来创建方形数组来实现。上面显示的具有可分离分配器的 3x4 分配示例需要 4x4 波前分配器。

波前分配器的执行从设置四个优先级线之一(p0:::p3)开始。这将行和列标记提供给连接到所选优先级线的对角单元格组。如果其中一个单元正在请求资源,它将消耗行和列令牌,并且其资源请求被授予。无法使用其令牌的单元格将行令牌向右传递,将列令牌向下传递。为了提高公平性,初始优先级组每个周期都会改变。

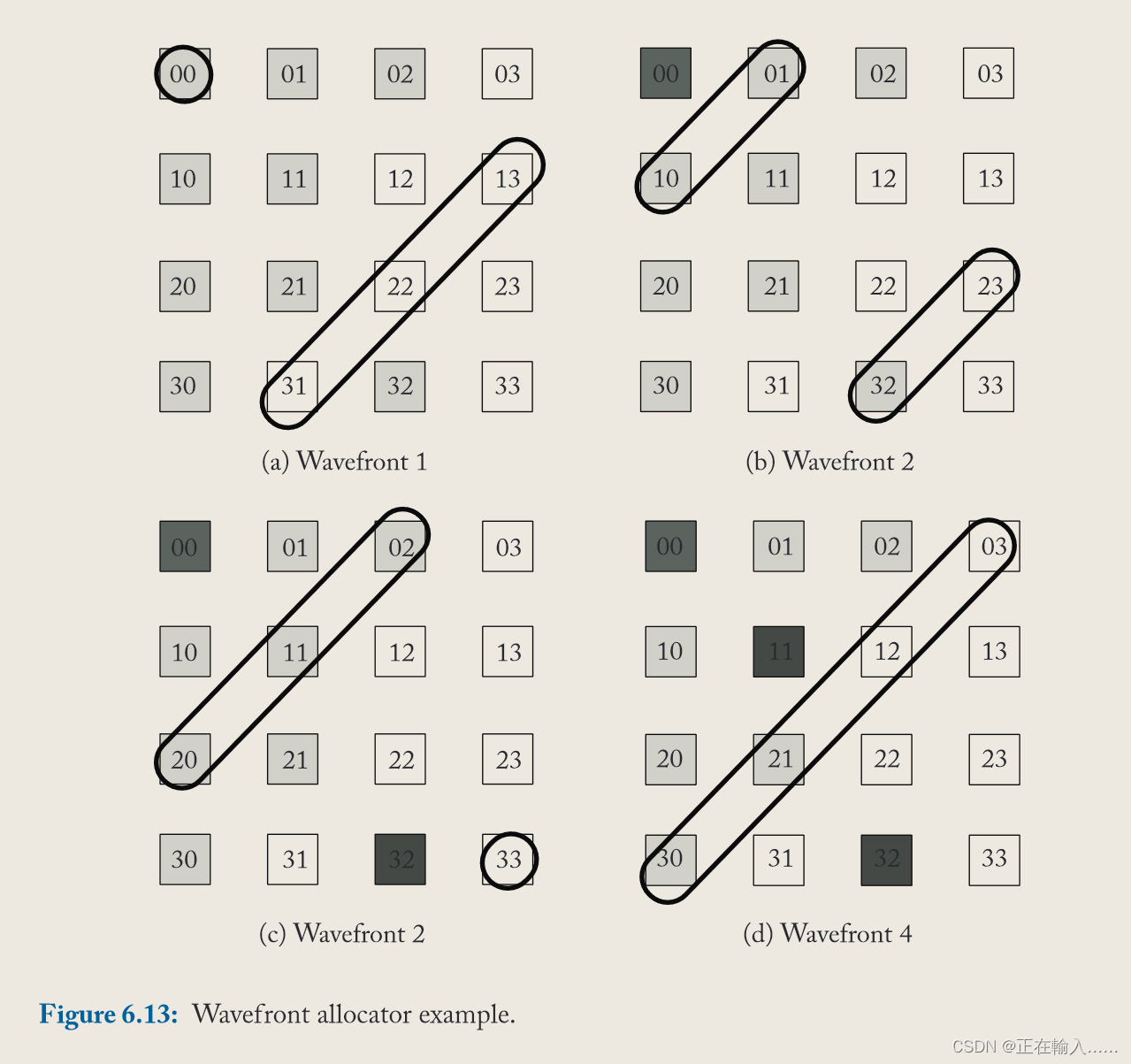

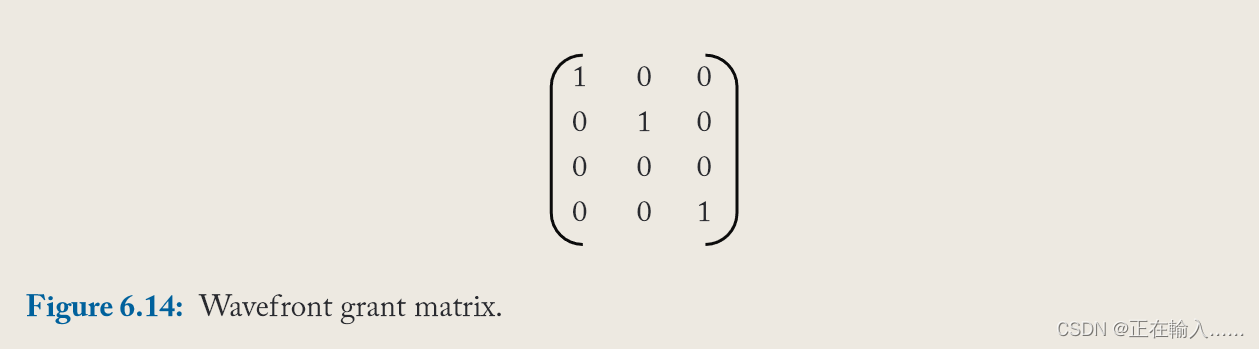

使用图 6.11a 中的相同请求矩阵,我们接下来说明波前分配器的功能。浅灰色阴影是请求矩阵中的请求。从 p0 开始的第一对角优先级波在图 6.13a 中圈出。条目 [0,0] 是第一个获得资助的条目(以深灰色突出显示)。接下来,波向下并向右传播(如图 6.13b 所示)。条目[0,0]在收到授权时在第一阶段消耗了一个令牌;因此,随着波的传播,[0,1] 和 [1,0] 在第二波中不会收到令牌,因为它已经被消耗了。条目 [3,2] 从 [3,1] 和 [2,2] 接收令牌,这导致其请求被授予(图 6.13c)。图6.13c显示了第3优先波;剩余未使用的令牌再次向下并向右传递。请求[1,1]在此波中收到有效令牌并收到授权。波前完全传播后,生成的授权矩阵如图 6.14 所示。波前分配器能够授予三个请求(与此示例中使用可分离分配器的单个请求不同,大大提高了输入虚拟通道和输出端口的匹配率)。

6.4.5 分配器的组织方式

自适应路由可能会使交换机的 flits 分配变得复杂。对于确定性路由算法,有一个所需的输出端口;开关分配器的功能只是选择单个输出端口。通过返回多个候选输出端口的自适应路由功能,交换机分配器可以对所有输出端口进行仲裁。授予的输出端口必须与虚拟通道分配器授予的虚拟通道匹配。或者,如果flit未能获得输出虚拟通道,则路由功能可以返回单个候选输出端口,然后重试路由(对于不同的输出端口)。

虚拟通道分配器的设计可以取决于路由功能的实现。可以实现路由功能以返回单个虚拟通道。这将导致虚拟通道分配器只需要在争用相同输出虚拟通道的输入虚拟通道之间进行仲裁。如果路由实现更通用,并且为同一物理通道返回多个候选虚拟通道,则分配器需要首先在 v 个可能的第一阶段请求中进行仲裁,然后再将获胜请求转发到第二阶段(可以使用上面描述的可分离分配器来完成)。返回所有候选物理通道的所有候选虚拟通道的路由函数是最通用的,并且需要虚拟通道分配器提供更多功能。

对于推测性虚拟通道路由器,非推测性交换机请求必须具有比推测性请求更高的优先级。实现此目的的一种方法是使用两个并行的开关分配器。一个分配器处理非推测性请求,而第二个分配器处理推测性请求。通过两个分配器的输出,可以选择成功的非推测请求而不是推测请求。然而,如果路由器中没有非推测性请求,则推测性交换机请求将成功分配所需的输出端口。 flit 有可能在推测交换机分配中成功,但在并行虚拟通道分配中失败。在这种情况下,推测是不正确的并且由交换机分配器保留的交叉开关通道被浪费。执行 VC 分配只需要head flit传输。因此,后续的主体和尾部 flits 被标记为非推测性(对于它们的开关分配),因为它们继承了分配给 head flit 的 VC。

路由器微架构流水线部分单独总结。

630

630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?