Verilog PID调节器基于fpga的Verilog PID调节器源码

ID:2220597454912833

灰太狼-xyz

在现代工程领域中,PID(Proportional-Integral-Derivative)控制器被广泛应用于自动控制系统中,其稳定性和鲁棒性使之成为许多实时控制系统的核心组件。随着技术的不断进步,FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,为PID控制器的实现提供了更加灵活和高效的方法。本文将基于FPGA实现一个Verilog PID调节器,为工程师提供一个参考和实践的方向。

首先,让我们来了解一下PID控制器的基本原理。PID控制器的核心思想是根据当前系统的误差和误差的变化率来调整输出信号,以使系统的行为与期望值尽可能接近。PID控制器由三个部分组成:比例控制器、积分控制器和微分控制器。比例控制器根据误差的大小与输出信号成比例地调整输出;积分控制器根据误差的累积量进行调整,以消除系统的静差;微分控制器根据误差的变化率调整输出,以提高系统的动态响应。

在FPGA中实现PID控制器需要使用Verilog语言描述其硬件逻辑。Verilog是一种硬件描述语言(HDL),能够对数字逻辑电路进行建模和仿真。通过使用Verilog编写的源码,我们可以描述PID控制器的逻辑结构和功能,并将其综合到FPGA上实现。

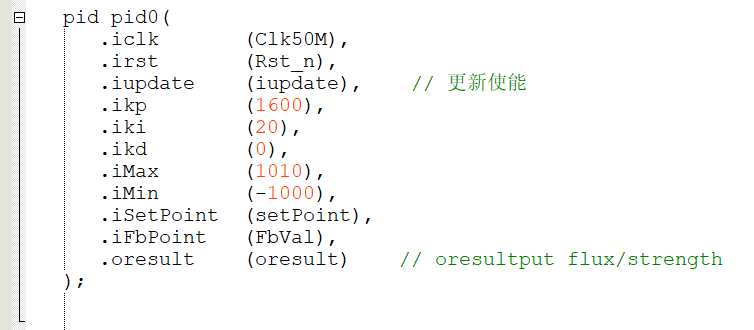

对于Verilog PID调节器的设计,我们需要考虑以下几个关键点。首先是输入和输出接口的定义。PID控制器的输入通常包括期望值(Setpoint)和反馈值(Feedback),输出为控制信号(Control Signal)。我们需要定义合适的输入输出接口,以便与外部系统进行数据交互。

其次是比例、积分和微分控制器的实现。在Verilog源码中,我们需要为每个控制器设计合适的逻辑电路和运算单元。比例控制器可以简单地通过乘法运算实现,积分控制器需要累加器来计算误差的累积量,微分控制器可以通过差分运算来计算误差的变化率。

此外,我们还需要考虑PID控制器的参数调节和反馈机制。PID控制器的性能取决于其参数的选择和调整。在Verilog源码中,我们可以为参数提供可调节的接口,使得工程师能够根据具体应用进行调试和优化。同时,我们还可以添加反馈机制,以实时监测系统的性能并对控制器进行自适应调整。

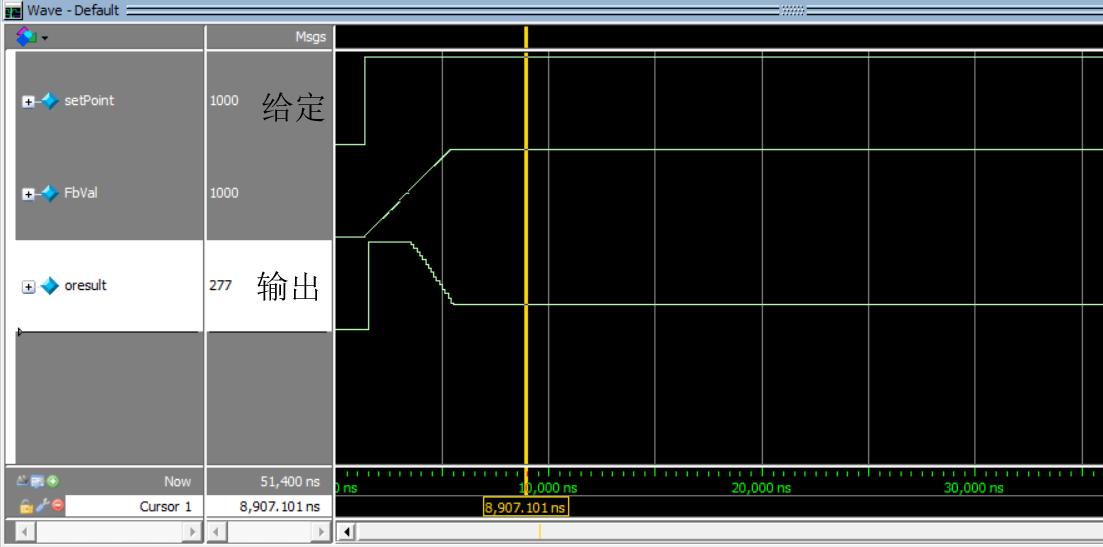

最后,我们需要对Verilog PID调节器进行仿真和验证。通过使用Verilog仿真工具,我们可以对源码进行仿真测试,以验证控制器的功能和性能。在测试过程中,我们可以模拟不同的输入和参数组合,以检验控制器在不同工况下的稳定性和鲁棒性。

综上所述,本文围绕Verilog PID调节器基于FPGA的实现展开了论述。PID控制器作为现代工程领域中重要的自动控制组件,其使用Verilog语言在FPGA上实现具有许多优势。通过对比例、积分和微分控制器的实现、参数调节和仿真验证等关键点的介绍,本文为工程师提供了一个参考和实践的方向。通过不断的研究和优化,Verilog PID调节器将在实际应用中展现出更加卓越的性能和效果。

相关的代码,程序地址如下:http://imgcs.cn/597454912833.html

3384

3384

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?