6.2 Clocks

最大系统时钟频率

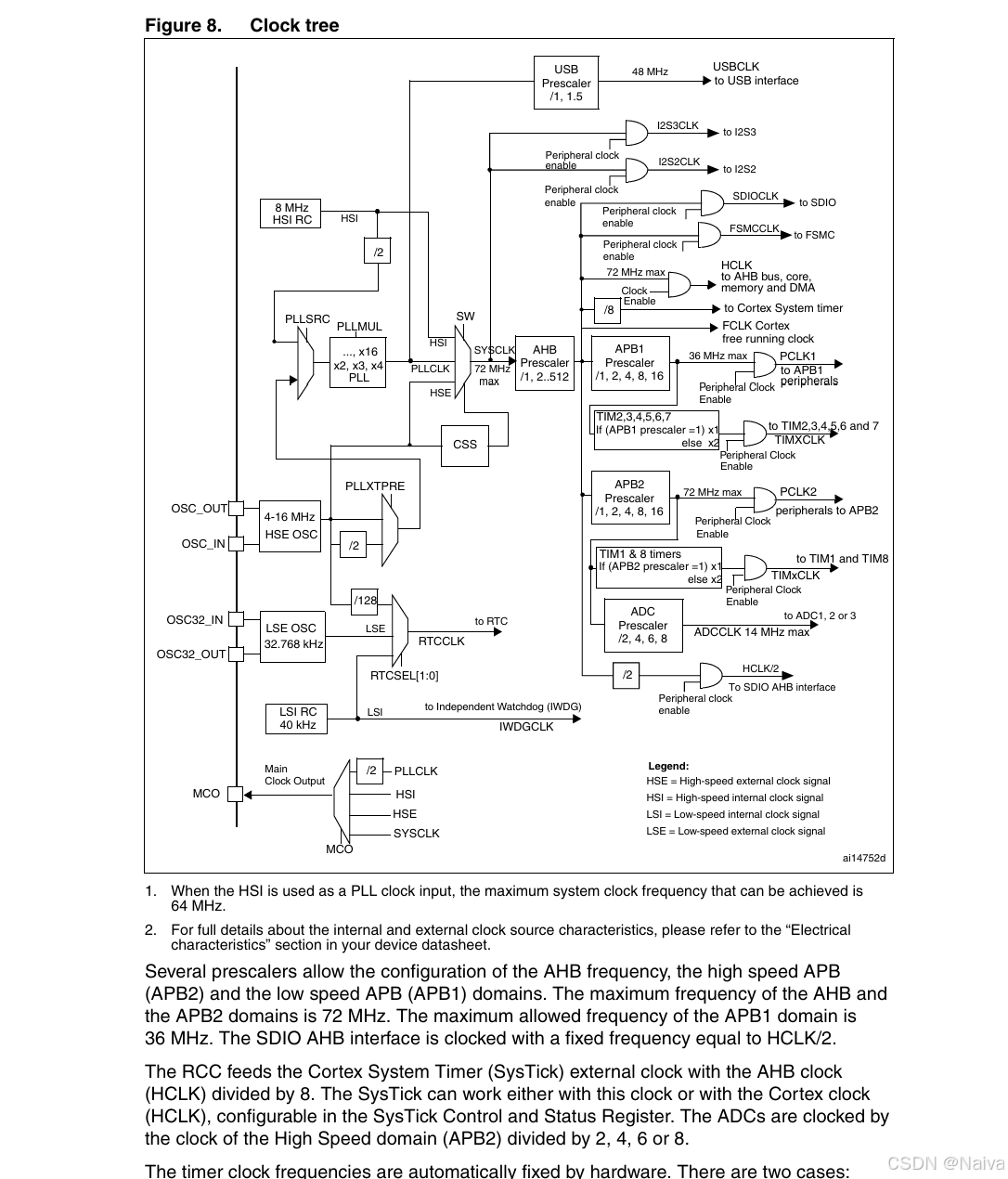

当 STM32F103 系列仅使用内部高速振荡器(HSI,8 MHz)作为时钟源,并通过 PLL 放大时,最大可达 64 MHz。([forum.mikroe.com][1], [keil.com][2])

- HSI 被内部除以 2(即 4 MHz)后输入 PLL,PLL 最多可设置到 ×16,因此最大输出时钟为 4 MHz × 16 = 64 MHz。([forum.mikroe.com][1])

- 如果不使用 PLL,直接用 HSI 作为系统时钟,则只能运行在 8 MHz。([Medium][3])

修改步骤概览

要在 system_stm32f10x.c 中去掉外部 8 MHz 晶振(HSE),并改用 HSI/2 → PLL → 64 MHz,需要:

-

在预编译宏中定义新的选择:

#define SYSCLK_USE_HSI_PLL -

在

SystemCoreClock的初始值分支里添加对应项:#ifdef SYSCLK_USE_HSI_PLL uint32_t SystemCoreClock = 64000000; // 64 MHz #elif defined SYSCLK_FREQ_72MHz … #endif -

在

SetSysClock()的分支调度中增加 HSI_PLL 路径:static void SetSysClock(void) { … #elif defined SYSCLK_USE_HSI_PLL SetSysClockToHSI_PLL(); #endif } -

新增并实现

SetSysClockToHSI_PLL()函数,用来配置 PLL 源为 HSI/2,倍乘因子为 16:static void SetSysClockToHSI_PLL(void) { // 1. 确保 HSI 已开启并稳定 RCC->CR |= RCC_CR_HSION; while (!(RCC->CR & RCC_CR_HSIRDY)) {} // 2. 配置 PLL 源:HSI/2, 倍频 ×16 RCC->CFGR &= ~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL); RCC->CFGR |= RCC_CFGR_PLLSRC_HSI_Div2 // PLL 时钟源 = HSI/2 | RCC_CFGR_PLLMULL16; // PLL 倍频因子 = 16 // 3. 启动 PLL 并等待就绪 RCC->CR |= RCC_CR_PLLON; while (!(RCC->CR & RCC_CR_PLLRDY)) {} // 4. 选择 PLL 作为系统时钟源 RCC->CFGR &= ~RCC_CFGR_SW; RCC->CFGR |= RCC_CFGR_SW_PLL; while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL) {} // 5. 设置总线预分频:AHB = /1, APB1 = /2, APB2 = /1 RCC->CFGR &= ~(RCC_CFGR_HPRE | RCC_CFGR_PPRE1 | RCC_CFGR_PPRE2); RCC->CFGR |= RCC_CFGR_PPRE1_DIV2; // APB1 ≤36MHz // 6. 配置 Flash 延时为 2 WS (64MHz 下至少需 2 WS) FLASH->ACR &= ~FLASH_ACR_LATENCY; FLASH->ACR |= FLASH_ACR_LATENCY_2; }- 以上配置最终使得:

SYSCLK = PLLCLK = 64 MHz,HCLK = 64 MHz,PCLK2 = 64 MHz,PCLK1 = 32 MHz(符合 APB1 ≤ 36 MHz 要求)。([keil.com][2])

- 以上配置最终使得:

关键寄存器说明

-

RCC->CR

HSION(bit0):开启内部振荡器。HSIRDY(bit1):HSI 就绪标志。PLLON(bit24):开启 PLL。PLLRDY(bit25):PLL 就绪标志。

-

RCC->CFGR

SW(bits1:0):系统时钟切换;00=HSI,10=PLL。SWS(bits3:2):时钟源就绪标志。PLLSRC(bit16):PLL 源选择;0=HSI/2,1=HSE。PLLMULL(bits21:18):PLL 倍频因子;1110对应 ×16。HPRE、PPRE1、PPRE2:AHB/APB 预分频。

-

FLASH->ACR

LATENCY(bits2:0):Flash 访问延时周期;在 48–72 MHz 下至少要2 WS(值010)。

以上即为使用内部 8 MHz 时钟、最大可达 64 MHz 的配置方案,并附上关键代码修改示例。

1160

1160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?