基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:

- 输入路径(Input Path),使用输入约束

- 寄存器到寄存器路径(Register-to-Register Path),使用周期约束

- 输出路径(Output Path),使用输出约束

- 具体的异常路径(Path specific exceptions),使用虚假路径、多周期路径约束

一、 输入约束Input Constraint

OFFSET IN约束限定了输入数据和输入时钟边沿的关系。

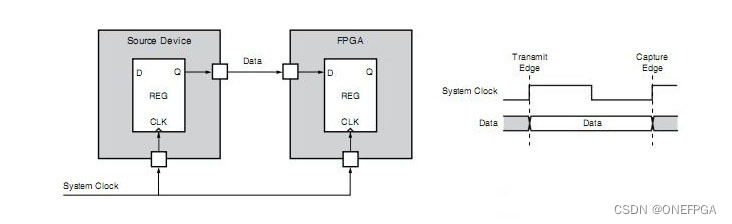

1.系统同步输入约束System Synchronous Input

在系统同步接口中,同一个系统时钟既传输数据也获取数据。考虑到板子路径延时和时钟抖动,接口的操作频率不能太高。

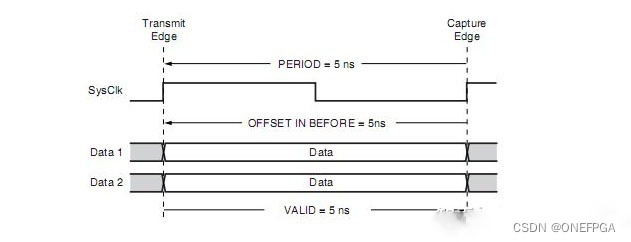

上述时序的约束可写为:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;</

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:输入路径(Input Path),使用输入约束寄存器到寄存器路径(Register-to-Register Path),使用周期约束输出路径(Output Path),使用输出约束具体的异常路径(Path specific exceptions),使用虚假路径、多周期路径约束一、 输入约束Input ConstraintOFFSET IN约束限定了输入数据和输入时钟边沿的关系。1.

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:输入路径(Input Path),使用输入约束寄存器到寄存器路径(Register-to-Register Path),使用周期约束输出路径(Output Path),使用输出约束具体的异常路径(Path specific exceptions),使用虚假路径、多周期路径约束一、 输入约束Input ConstraintOFFSET IN约束限定了输入数据和输入时钟边沿的关系。1.

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2638

2638

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?