使用BDM和JTAG调试MPC8xx

1.1 参考

用户应该熟悉“MPC860 PowerQUICC™系列用户手册”(MPC860UM/D)和“32位PowerPC™体系结构编程环境手册”(MPEFPC32B/AD)。

这些手册可以从MPC860网页上下载。

点击下面的连接可以转到飞思卡尔半导体产品区主页:

http://www.freescale.com

推荐阅读IEEE 1149.1 JTAG规范以熟悉JTAG。

1.2 BDM概貌

在BDM出现之前,可选的调试工具只有ROM监控器或者在线仿真器(ICE)。前者需要编写一定的调试代码下载到RAM中,如果需要固化到ROM中则需要一定的存储空间。为了与外部调试器通信,ROM监控器可能在设备内部需要一个接口,从而降低设备的性能;或者需要一个外部接口,从而增大目标板的尺寸。另外一个选择——ICE在对处理器的控制上提供了更大的灵活性,包括实时跟踪、编程模式访问和硬件断点,不需要使用处理器资源。然而,由于ICE需要接入外部信号,以及专用的电缆和外部存储器,因此ICE被认为是开发中一笔昂贵的花费。

MPC8xx上实现了BDM,以克服ROM监控器的限制,并且不需要ICE的昂贵开销。这是通过发展硬件本身的某些功能来实现的,本文接下来将详细介绍。一个全双工的串行接口允许在开发端口支持逻辑和开发工具之间进行通信。通过内部的观察点和断点,能够跟踪程序流程。更重要的是,单步调试允许在任何一个点上查询内存和寄存器。

1.3 BDM的运行

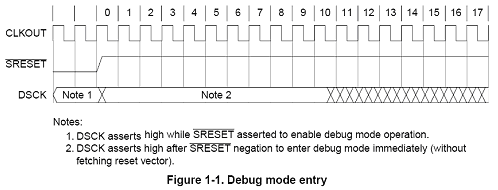

开发端口能够工作在两种模式:自陷使能模式和调试模式。在自陷使能模式下,开发端口从开发工具接收一个10bit的信号,这些信号用于控制片上断点功能和调试端口命令。在调试模式下,所有从开发端口取得的指令(32bit)全部送到处理器去执行,这样加载/存储内存的操作在真实的系统内存中进行。调试模式是在复位的情况下,SRESET信号拉低之前至少3个时钟周期情况下,通过拉高DSCK信号使能的,如图1-1所示。如果DSCK信号是在SRESET信号保持低电平的情况下拉高的,则处理器产生一个断点异常直接进入调试模式,而不是取得复位向量号。这使得用户可以调试一个缺乏ROM的系统。如果在复位之后不需要进入调试模式,则DSCK信号必须在SRESET信号保持低电平的之后的7个时钟周期内进入低电平。

调试使能寄存器(DER)允许用户选择性的使能导致处理器进入调试模式的事件。中断事件通过中断导致寄存器(ICR)报告的。这导致只有DER中相应的位被设置,并且调试模式被使能的情况下才能进入调试模式。进入调试模式之后,程序将从进入调试模式的位置继续执行。退出调试模式使用rfi指令,处理器将恢复到正常操作,并且FRZ/FLS引脚被拉低。

1.4 系统接口

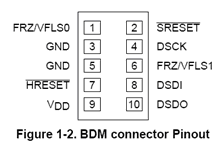

BDM信号通过开发端口接口与开发工具进行通信。接口是一个由10针组成的位于用户开发板上的接头,如图1-2所示。

开发串行时钟(DSCK)用于在复位的时候使能调试模式。在复位之后可以立刻进入调试模式,也可以通过ICR中一个事件报告的发生来进入调试模式。对于开发端口来说,DSCK是一个输入信号,并且在任何时候必须保持高电平或者低电平,DSCK信号不能悬浮。因此建议将该引脚连接到一个下拉寄存器,以避免意外进入调试模式。DSCK也用于异步时钟模式下,为数据进出开发端口的移位寄存器提供时钟,因为DSCK信号与CLKOUT是异步的。另一个可用的时钟模式叫做异步自时钟,不需要输入时钟。因此端口是通过系统时钟驱动的。这两种时钟模式的选择发生在复位的时候。DSDI输入信号是在SRESET信号拉低8个时钟周期之后被锁定的。如果输入是低,则使能异步时钟模式,否则异步自时钟模式被使能。

开发串行时钟(DSCK)用于在复位的时候使能调试模式。在复位之后可以立刻进入调试模式,也可以通过ICR中一个事件报告的发生来进入调试模式。对于开发端口来说,DSCK是一个输入信号,并且在任何时候必须保持高电平或者低电平,DSCK信号不能悬浮。因此建议将该引脚连接到一个下拉寄存器,以避免意外进入调试模式。DSCK也用于异步时钟模式下,为数据进出开发端口的移位寄存器提供时钟,因为DSCK信号与CLKOUT是异步的。另一个可用的时钟模式叫做异步自时钟,不需要输入时钟。因此端口是通过系统时钟驱动的。这两种时钟模式的选择发生在复位的时候。DSDI输入信号是在SRESET信号拉低8个时钟周期之后被锁定的。如果输入是低,则使能异步时钟模式,否则异步自时钟模式被使能。

开发串行数据输入(DSDI)引脚从开发工具接收数据,数据是以移位的方式串行进入开发端口的移位寄存器。

开发串行数据输出(DSDO)引脚从开发端口的移位寄存器传送数据到开发工具。

冻结(FRZ)引脚指示处理器在调试模式下,用于停止任何片外设备,并且允许开发端口和工具之间的一个握手。当FRZ信号拉高,软件看门狗的时钟、PIT、实时时钟、时间计数器以及递减器可以被禁止。这是通过每个定时器的控制寄存器中相关的位来控制的。如果被编程为FRZ信号拉高就停止计数,则计数器将保持已有的值不变,直到FRZ信号拉低。然而总线监控器将被使能,与该信号的状态无关。

为了允许开发工具复位处理器,BDM接头必须包含HRESET和SRESET信号。VDD信号用于向开发工具提示目标板上电。

1.6 JTAG概貌

通常用于测试印刷电路板(PCB)的方法包括“边界连接测试”和“钉床”测试。然而随着多引脚设备和多层PCB的出现,这些方法不再合适,二十世纪八十年代,节点测试行动小组(JTAG)成立(成员来自200多个公司)来解决这一问题。他们随后开发了一个集成硬件到标准设备中的标准,通过软件可以控制该硬件。被称作边界扫描测试(BST)。后来IEEE采纳了这个标准,并定义了IEEE1149.1标准测试访问端口和边界扫描结构。MPC8XX系列提供了一个兼容这个标准的测试访问端口(TAP)。

1.7 TAP接口

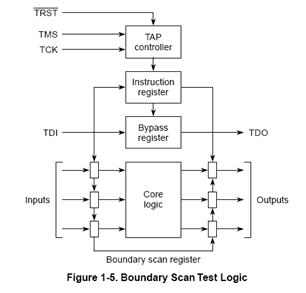

测试逻辑由一个4位的指令寄存器和两个数据寄存器(一个1位的旁通寄存器和一个475位的边界扫描寄存器)组成。这些寄存器的操作是通过TAP控制状态机来控制的,TAP状态机的序列是通过测试模式选择(TMS)输入来控制的。寄存器是被通过串行测试数据输入引脚(TDI)输入的数据修改的。而输出结果则从串行测试数据输出引脚(TDO)输出的。当数据没有输出设备的时候TDO引脚是三态的,。一个活动的低的异步复位(通过一个内部的上拉电阻)用来初始化TAP控制器。边界扫描寄存器是一个475位的串行移位寄存器,容纳了除XTAL、EXTAL和XFC(这些是模拟信号)之外的所有信号,当设备正常工作时,边界扫描电路处于非激活状态。然而,当进入测试模式之后,位于每一个引脚上的边界扫描单元被连接成一个位于TDI和TDO之间的扫描链,如图1-5所示。通过这种方法可以进行设备的电气测试,例如连接性测试:确保目标板上没有断路和短路。

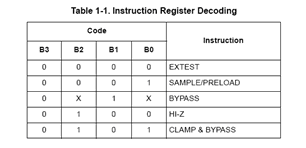

TAP实现了一个指令寄存器,这是IEEE1149.1标准所必须的,它是一个4位宽度,没有校验的寄存器。通过这四个指令位选择三种必须的和两种可选的指令。如表1-1所示。

在“测试-逻辑-复位”状态下,指令寄存器缺省选择BYPASS指令。外部测试(EXTEST)指令使处理器进入外部边界测试模式,并且在TDI和TDO之间连接475位的边界扫描寄存器。EXTEST也产生一个内部的软复位,使得MPC8xx的系统逻辑在执行外部边界扫描操作的时候,强制进入到一个已知的起始内部状态。

BYPASS指令通过在TDI和TDO之间放置一个1位的旁通寄存器,允许数据在正常工作过程中经过处理器。数据不会进入边界扫描链,从而当MPC8xx之外的其他处理器被测试的时候提高测试效率。

SAMPLE/PRELOAD指令在TDI和TDO之间连接边界扫描寄存器,但是仍然允许处理器按照正常模式工作。这使得边界扫描寄存器能够对处理器的输入输出数据进行采样。

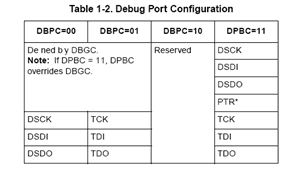

TCK,TDI和TDO引脚和开发端口引脚是复用的。这是在“硬件复位配置字”的DBPC位配置的。该字是在HRESET和RSTCONF信号拉高的时候从数据总线加载的。如果这时RSTCONG没有拉高,就会选择0作为缺省值。为了确保TAP接口功能正常,必须如表1-2所示那样配置DBPC位[D11/D12]。

如果BDM和TAP端口都需要,则DPBC必须被设置成0x11,如表1-2的最后一列所示。

TAP控制器在上电之后位于“测试-逻辑-复位”状态,并且被禁用,以允许处理器正常工作。要进入JTAG模式时设置TMS=0。进入JTAG模式后,缺省进入一个等价于BYPASS的模式,在这种模式下,TDI和TDO之间通过旁通寄存器实现了一个1位的移位寄存器路径。一个测试MPC8xx进入JTAG模式的的简单方法就是,进入缺省的BYPASS模式后,驱动一个位流进入TDI,并且监控TDO在一个周期之后的输出是否一致。FRZ信号的拉高表明处理器位于调试模式,因此JTAG的入口条件尚未被满足。

1.8 TAP配置

TAP信号按照如下的要求进行配置,复位扫描链逻辑:

l 如果从不使用TAP和低功耗模式,则将TRST连接到地。

l 如果需要使用TAP或者低功耗模式,则将TRST连接到PORESET。

l 如果需要使用掉电模式(最低的功耗模式,VDDH被关闭),则通过一个二极管连接TRST到PORESET(阳极连接到TRST,阴极连接到PORESET)。

TMS、TDI和TRST信号包括片上的上拉电阻。然而,TCK没有片上的上拉或者下拉电阻;因此TCK必须通过一个10K的电阻下拉。TCK信号的频率应该不超过10MHz的最大允许频率。

1.9 边界扫描描述语言

边界扫描语言(BSDL)是VHDL的子集,在IEEE1149.1规范中,BSDL是一种描述边界扫描结构的标准化方法。设计者和测试软件开发者可以设计测试模式并在在线编程中操作。MPC860的BSDL文件能够在网上找到(参见1.1, “References”)。

1.10 结束语

通过集成BDM和JTAG支持功能到芯片中,以及提供简单的接口,克服了在MPC8xx的高密度电路板上调试和测试具有大量引脚的微处理器所遇到的巨大困难。实现这一特性,无需耗费宝贵的目标板空间,提高了用户的系统开发效率,同时降低了开发成本。

附录A

典型的初级问题和回答

下面的问题在开始阶段经常被问起。

l 当8xx在BDM下,cache被使能,cache是否会响应对外部内存的访问?也就是说在BDM下从核心读写内存时,cache会干预或者响应么?

当你在BDM下的时候,cashe被冻结。你可以读写cache的寄存器,从而查看其内部,但是cache将不会按照正常的模式工作。不论在进入BDM之前cache处于任何模式,都是如此。

l 在MPC8xx BDM接口上,FRZ信号引脚能够代替VFLS(0:1)而不影响调试模式的功能么?

如果你不打算使用trace功能,那就不需要VFLS引脚。FRZ不能代替VFLS,他们的功能(用户手册的开发支持部分有相关的介绍)完全不同。

l 在BDM下,当访问内存的时候,处理器是否停止工作?

在BDM下,MPC8xx核心处于冻结状态,只接收来自BDM端口的指令。如果没有可以执行的指令,则核心处于冻结状态,也就是说在下一条指令出现在BDM端口上之前都停止工作。MPC8xx在访存的中间不应该中断,如果写内存的周期已经完成,并且没有其他指令可以执行,则处理器将停止。

l 来自开发端口的指令使用物理地址,而不是逻辑地址?用户手册表明来自开发端口的指令访问的是真实的系统内存,这意味者是物理内存?

在体系结构的规格说明书中,物理编址的内存通过真实的地址访问。

l 软复位(SRESET)之后将发生什么?

软复位之后,MPC8xx将根据用户的设置重新配置开发端口。用户应该确保没有对SIUMCR的假写,这将导致损坏调试端口的配置。

l TAP应该被如何配置才能避免意外的进入到JTAG?

为了确保正常的运行过程中扫描链测试逻辑对于系统逻辑是透明的,应该通过保持TRST或者TMS信号持续保持高电平来强制TAP进入“测试逻辑复位控制器”状态。

l 如果MPC8xx在上电后开始从FLASH执行程序然后进入JTAG模式,MPC8xx将继续执行位于FLASH上的代码么?

这取决于复位之后JTAG端口被配置成何种状态。当BYPASS模式被选择,所有的测试寄存器将执行正常的功能。

l 在JTAG模式下,MPC8xx的核心将会做什么?

进入JTAG模式后,核心将缺省进入一个等价于BYPASS的模式,在这个模式下,一个宽度为1位的移位寄存器被连接在TDI和TDO之间。一个测试MPC8xx进入JTAG模式的的简单方法就是,进入缺省的BYPASS模式后,驱动一个位流进入TDI,并且监控TDO在一个周期之后的输出是否一致。

l JTAG模式下FTZ将位于高电平?

FRZ信号表明内核位于调试模式,因此JTAG的入口条件尚未满足。

l 如果SIUMCR[DBGC和DBPC]在PORESET的时候被锁存,那么之后能够通过软件来修改他们么?

只要SIUMCR[DLK]没有被拉高,用户能够在任何时间修改这些域。

l 至少在JTAG建立的初始阶段,TRST必须保持高电平。如果TRST仍然保持低电平,通过将TMS拉到0并且锁住TCK,JTAG能够仍然被使用么?

TRST不能仍然位于低电平,但在初始阶段必须保持低电平。

l 如果处理器的输入时钟处于非活动状态,则JTAG将会工作么?PLL永远都不会锁么?

当输入时钟处于非活动状态时,边界扫描测试将仍然工作。然而任何非扫描测试,例如检查寄存器,将需要时钟功能。如果PLL丢失一个时钟将会导致一个内部硬件复位的发生。如果用户尝试从非活动状态启动处理器时钟,PLL将不会正常工作。PLL的工作需要稳定的时钟输入。

l 软件看门狗在BDM和JTAG下被禁用了么?

当JTAG被使能的时候,软件看门狗配置将和系统保护控制寄存器SYPCR[SWE]的设置一摸一样。进入JTAG之后,用户需要考虑MPC8xx的任何复位。看门狗定时器应该被手动禁用。BDM的情况是一样的。

4875

4875

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?