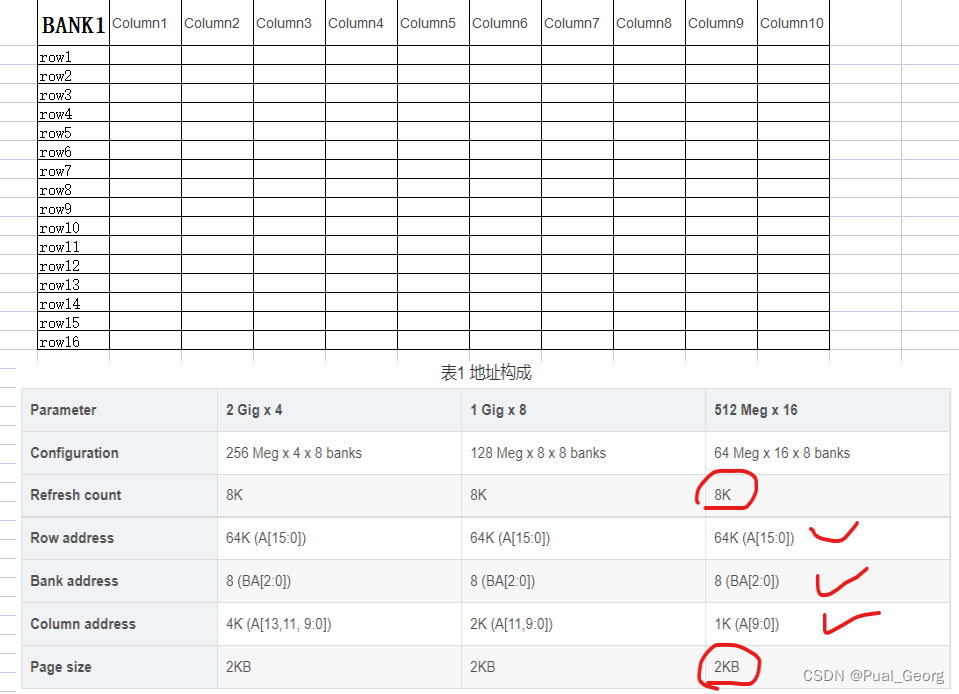

1.结构(16bit位宽,一共有8个BANK)

容量计算=2^16*2^3*2^10*16bit=8Gb=1GB

无论是KB转换MB还是Kbit转换Mbit都是2的10次方为单位(涉及内存容量都是1024其他都是1000的转换关系,涉及码率一般默认bit,涉及总线带宽默认B,网速转换是1000)。与频率,周期转换不一样。

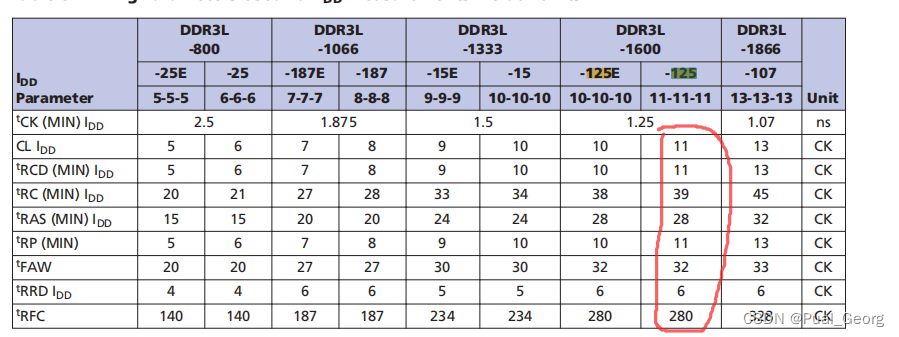

2.-125为速度频率

3.MIG

不仅包括RTL,还包括XDC约束文件。

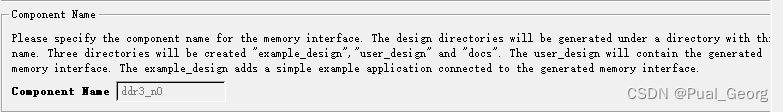

IP核的名字

IP核的名字

——一个控制器

AXI4 interface ——一般不勾选

clock period——DDR3和FPGA相连的差分时钟的频率(接口频率),一般根据FPGA性能而定。

k7_325T的一般也可以达到800M.(k7系列的FPGA所支持的DDR3传输速率高达1866MT/s,这里需要跟硬件工程师具体了解了解,实际使用最高还是1600MT/s,对应频率= 1600M/2= 800Mhz;)——对应到ip核是差分的ddr3_ck_p/n

4:1——换算到用户逻辑时钟200M.对应到ip核的信号输入是

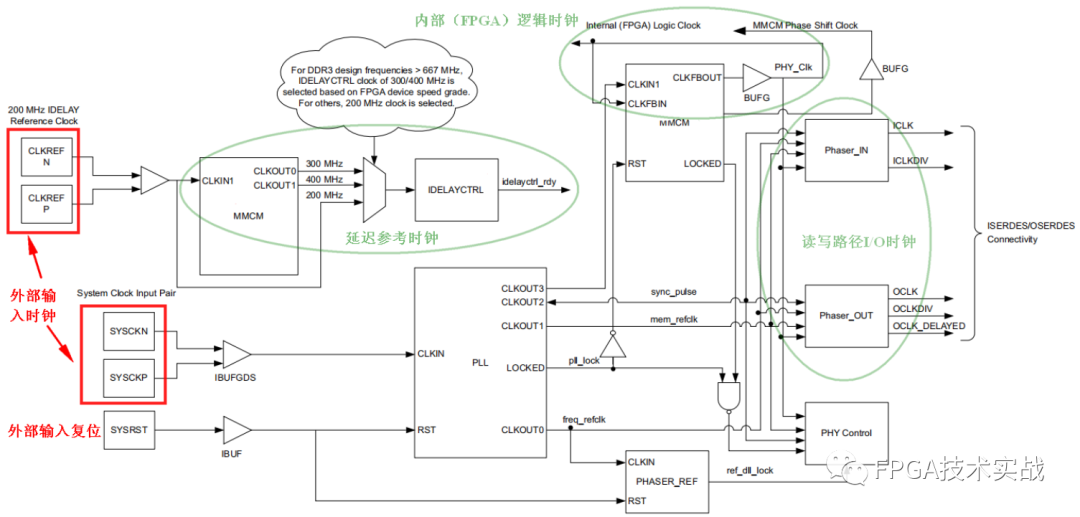

我们锁相环生成的200M时钟信号是给两个时钟(sys_clk_i/clk_ref_i)使用他是供ddr IP核内部使用,他会倍频到800M和分频到200M用户时钟(ui—clk)给我们读写测试模块使用

memory type——(components(颗粒)就是黑色的一小块DDR3 。CHIP,其他选项就是绿色的卡的那种样子的类型)

memory part——自定义的参数

——

——

——这里特别提醒一下:

——这里特别提醒一下:

物理Bank(Rank) 是多个芯片组成的内存条上出现的概念,由于处理器的数据位宽一般是32/64bits,而单个芯片的位宽等于其内部单个存储阵列的位宽4/8/16,所以需要多个芯片组合起来才能提供CPU需要的数据。

板卡上如果有只有一片DDR3,这里就设置16bit就行,如果4片DDR3那么位宽就是16bitX4=64bit。

ECC: ECC 校验使能,数据位宽为 72 位的时候才能使用。

Data Mask: 数据屏蔽管脚使能。勾选它才会产生屏蔽信号。

Number of Bank Machines: Bank Machine 的数量是用来对具体的每个或某几个来单独控制的,选择多了控制效率就会高,相应的占用的资源也多。若DDR3 芯片是八个 bank,这里选择 4 个,则平均一个 Bank Machine 控制两个BANK。

ORDERING: 该信号用来决定 MIG 控制器是否可以对它收到的指令进行重新排序,选择 Normal 则允许,Strict 则禁止。本实验选择 Normal,从而获得更高效率。

该时钟为上图中DDR3 IP核SYSCLKP/SYSCLKN时钟, 这是输入给MIG 核的时钟,IP核内部会自己调用pll和MMCM 来产生自己的工作时钟。

他的时钟类型由于是内部自己生成的,所以不选择单端或者差分时钟。

本实验选择200MHz,选择这个时钟频率的好处是Reference clock(上图时钟树直接硬性规定200M)可以直接选择使用system clock,也可以

Reference Clock: MIG IP 核参考时钟。同样选择1.“No Buffer”,将由时钟模块生成,(上图时钟树直接硬性规定200M)可以直接选择使用2.system clock,也可以

Read Burst Type and Length: 突发类型选择,突发类型有顺序突发和交叉突发两种,本次选择顺序突发(Sequential),其突发长度固定为 8。

8..从原理图导出来的信号名由于硬件命名不标准会导致MIG识别不成功的情况(一定以MIG的信号名为标准)

9.MIG识别原理eg:ddr3_dq[0]对应ddr3_dq<0>,才能识别成功。电平标准是默认生成的,实际不用绑定。(此处注意原理图到出来要切换到小写字母、数字外需要<>符号,)

10.DDR3既可和HP相连,又可和HR相连。推荐一般和HP相连。(注意A7只有HR——bank)

DDR4好像只能和HP相连。

11.如果配置 MIG ip核里面使能 XADC 的话,device tempe信号在veo里面是找不到的,位置在veo同名的.V文件里面

12.DDR3供电为1.5V、DDR3L为1.35V。

13.通过ddr3型号-125可以推断出ddr3接口速度1/125=800m

14.怎么选择系统时钟的3种类型:no buffer代表外部时钟非200m给到fpga,而内部逻辑进过pll,自带buffer到200给mig,其他两个事差分和单端是直接给到fpga

15:数据位宽等于关系:800*2*16=200*X(逻辑位宽)—x=128bit

16.选择ddr3型号是与原理图型号一样,位宽是ddr3和fpga的总位宽(eg:16bit*4)

937

937

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?