1.我们说的所有时序分析都是建立在同步电路的基础上的,异步电路不能做时序分析(或者说只能做伪路径约束(在设伪路径之前单bit就打拍,多bit就异步fifo拉到目的时钟域来))。——FPGA 设计中寄存器全部使用一个时钟的设计是同步设计电路,FPGA 设计寄存器使用多个时钟的设计是异步设计电路。

异步电路由于使用的时钟不同,导致上游寄存器的输出数据进入下游寄存器的时间是任意的,这非常可能导致不满足下游寄存器的建立时间要求和保持时间要求,从而导致亚稳态。同样的原因,由于两者时钟不同,所以也不法建立对应的模型来分析异步电路是否能满足时序要求

2.时序分析和时序约束的关系:

先有时序约束(告诉EDA工具你的时钟频率要求等),后有时序分析(1.静态2.动态)。

3.时序收敛:

时序收敛就是你改作业的过程,把不及格的作业通过改、抄等手段给改到合格的过程就是时序收敛。

4.

组合逻辑:组合逻辑电路的毛刺现象几乎是不可避免的

时序逻辑:时序逻辑电路解决了组合逻辑电路无法解决的毛刺问题,将电路的行动全部置于统一的行动之下----时钟。

5.

高级的FPGA芯片其建立时间和保持时间会比低级的FPGA芯片较小,这也是其能运行频率更高的原因。——如果建立时间或者保持时间的要求无法被满足,那么就会发生亚稳态现象。此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为决断时间Tmet(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关

6.

四种基本的时序路径的第四种——FPGA管脚到管脚:通常是纯组合逻辑电路类似于直通处理

7.源寄存器与目的寄存器之间其采样时间相差一个时钟周期。

- 发射沿(Launch Edge) :是源寄存器采样的时间点,也是时序分析路径的起点

- 锁存沿(Latch Edge):是目的寄存器采样的时间点,也是时序分析路径的终点

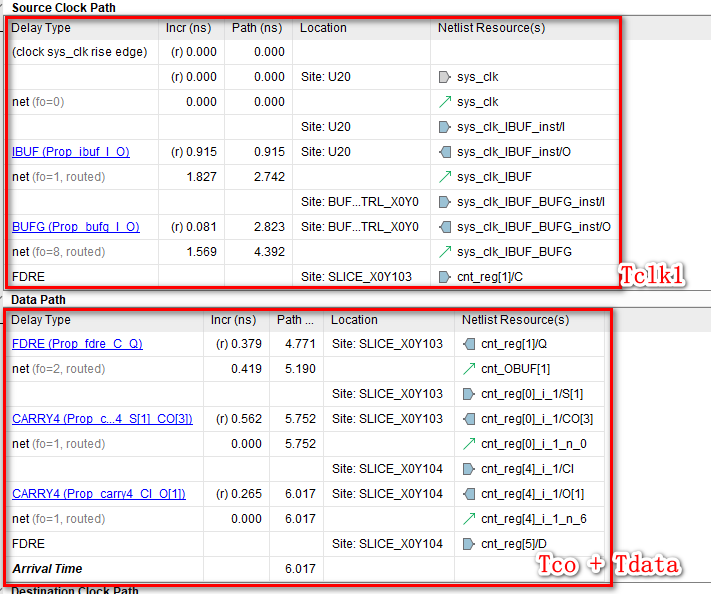

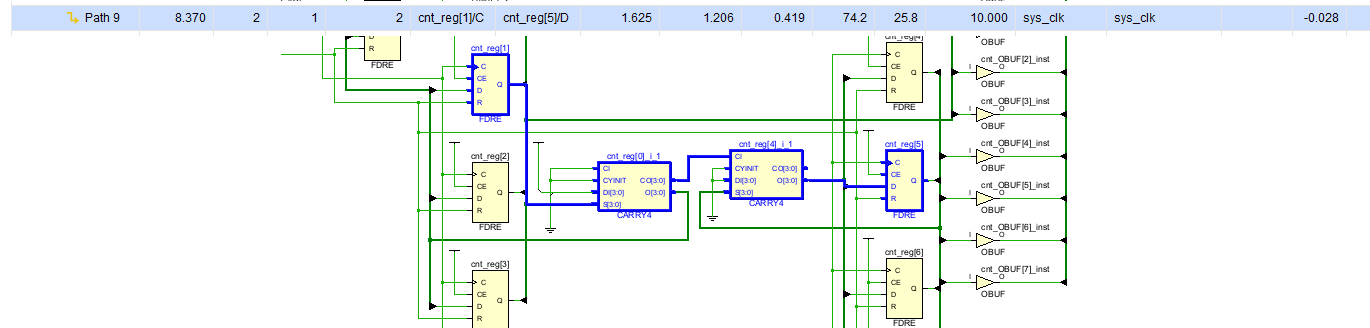

8.Data Arrival Time(数据到达时间)Data Arrival Time = launch edge(一般是0时刻点) + Tclk1(FPGA的时钟管脚--布线--IBUF(这个是缓冲的,每个管脚都会自动添加,增加驱动能力)--布线--BUFG(全局时钟网络,可以减少时钟到不同寄存器之间的Skew,一般时钟管脚都会添加)--布线--源端寄存器时钟端口。从上图可以看到,把每一条细小的路径叠加后,时钟从IO口到源端寄存器的时间是 4.392ns。) + Tco +Tdata【数据路径则是数据从源端寄存器的D端到目的寄存器的D端的路径,也就是Tco + Tdata。Tco等于0.379ns,接下来的所有net+2个CARRY4则是组合逻辑的延迟即Tdata,计算得到Tco + Tdata = 1.625ns。】——Tclk1+Tco+Tdata=6.017ns

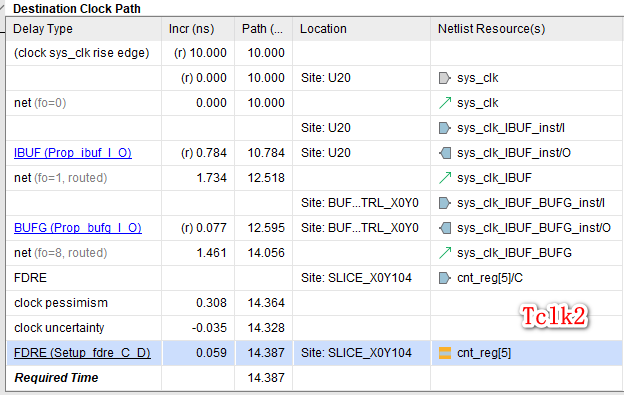

9.数据需求到达的时间:Data Required Time = latch edge + Tclk2(如下图) - Tsu

10.数据需求时间--保持时间:Data Required Time = latch edge + Tclk2 + Th

11.Setup Slack=Data Required Time-Data Arrival Time 则说明数据在规定的时间内达到了目的寄存器;反之,则认为数据并没有在规定的时间达到目标,此时REG2锁存的数据很有可能是亚稳态状态。(平时我们大多都是通过减少Tdata来使得时间裕量为正,以此实现设计的时序收敛。)

12.Hold Slack = Data Arrival Time - Data Required Time 如果Hold Slack为正,则认为数据在被锁存的时候有足够多的稳定时间,是有效的;反之则认为数据可能是亚稳态状态。

13.主时钟(Primary Clock)——约束如果记不住语句可以通过GUI界面来产生约束文件

主时钟通常有两个来源:(1)板级时钟(主要是晶振)通过输入端口进入FPGA;(2)FPGA的GT收发器的输出管脚(如恢复时钟)。

14.

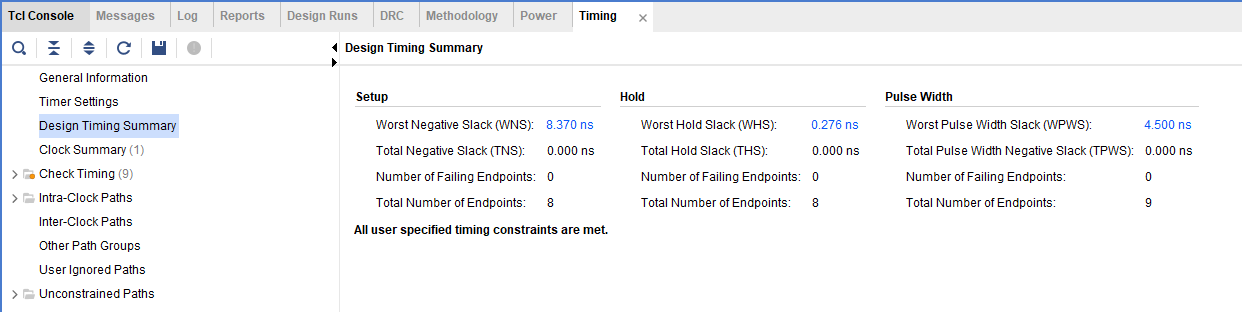

- WNS:最差负时序裕量 (Worst Negative Slack)

- TNS :总的负时序裕量 (Total Negative Slack),也就是负时序裕量路径之和

- WHS :最差保持时序裕量 (Worst Hold Slack)

- THS :总的保持时序裕量 (Total Hold Slack),也就是负保持时序裕量路径之和

15.

- 可以看到WNS为8.370ns,这表示这个工程中最差的那条时序路径的建立时间裕量是8.370ns,所以该设计是时序收敛的。如果时序不收敛,那么肯定是有WNS为负。

- 而TNS为0代表不存在建立时间裕量为负的时序路径,这也表示设计是收敛的。如果设计不收敛,那么必然存在1条或多条建立时间裕量为负的时序路径,作为路径之和的TNS也就一定是一个负数。

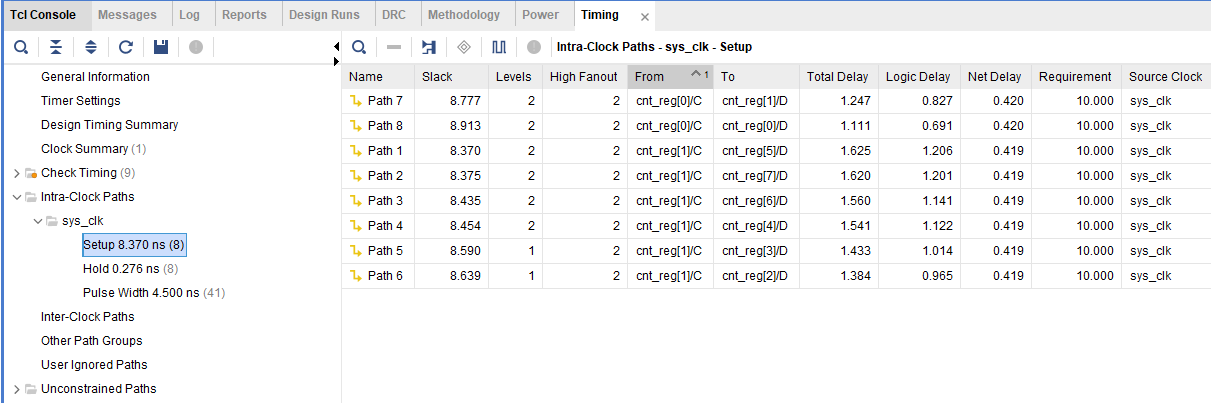

16.我们最需要关注的是intra-clock paths下sys_clk的setup和hold,这把具体的时序路径都穷举出来了:

- slack:建立时间裕量

- level:逻辑级数,这里1就表示在两个寄存器之间仅存在1个组合逻辑器件

- fanout:表示从这一点连接到了几个目的端点,fanout = 1就表示连接了1个目的端点

- from to:表示是哪两者之间的时序

点击schematic(两个寄存器之间的东西就表示level数,如图为2level)

17.

slack:裕量,具体到这条路径就是建立时间裕量,裕量为8.370ns,表示这条路径是满足时序要求的

source:源端寄存器,即时序分析的起点,发射沿(Launch Edge)

destination:目的端寄存器,即时序分析的终点,锁存沿(Latch Edge)

path group:时序分析的时钟来源

path type:路径类型,此路径为建立时间的分析

requirement:时序要求,设定为100MHz,所以就是10ns

data path delay:组合路径的数据延时,包括组合逻辑器件的延时(logic)和布线延时(route)

logic levels:逻辑级数,即两个寄存器之间存在多少级组合逻辑

clock path skew:时钟到达目的寄存器和源寄存器之间的时间差值

clock uncertainty :时钟的不确定度,包括skew和jitter

文章探讨了FPGA设计中同步和异步电路的区别,强调了时序分析在确保电路正确性中的重要性。同步电路基于单一时钟,而异步电路的时钟差异可能导致亚稳态问题。时序约束先于时序分析设定,用于指定时钟频率要求。时序收敛是优化设计以满足时序要求的过程。文章还详细解释了建立时间、保持时间、时序路径、时序裕量等概念,并提供了WNS、TNS等关键指标用于评估设计的时序收敛状态。

文章探讨了FPGA设计中同步和异步电路的区别,强调了时序分析在确保电路正确性中的重要性。同步电路基于单一时钟,而异步电路的时钟差异可能导致亚稳态问题。时序约束先于时序分析设定,用于指定时钟频率要求。时序收敛是优化设计以满足时序要求的过程。文章还详细解释了建立时间、保持时间、时序路径、时序裕量等概念,并提供了WNS、TNS等关键指标用于评估设计的时序收敛状态。

3912

3912

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?