锁相环电路,有教程

输出频率800MHz或者1GHz,

采用Ring_VCO的结构,输入参考频率20MHz,分频器是40-50分频,电荷泵电流20uA,工艺是smic55nm

每个模块都有单独的testbench

可送一些仿真,设计参考资料

还有matlab,verilog-a建模推导。

呈现最完整的project

前仿真,无版图

ID:21159747278137869

IC软硬件学习资料营

锁相环电路是一种常见的频率合成电路,在各种通信系统和数字电路设计中都得到广泛应用。本文将围绕锁相环电路的设计和实现展开讨论,具体参数如下:输出频率为800MHz或者1GHz,采用Ring_VCO的结构,输入参考频率为20MHz,分频器采用40-50分频,电荷泵电流为20uA,工艺为smic55nm。

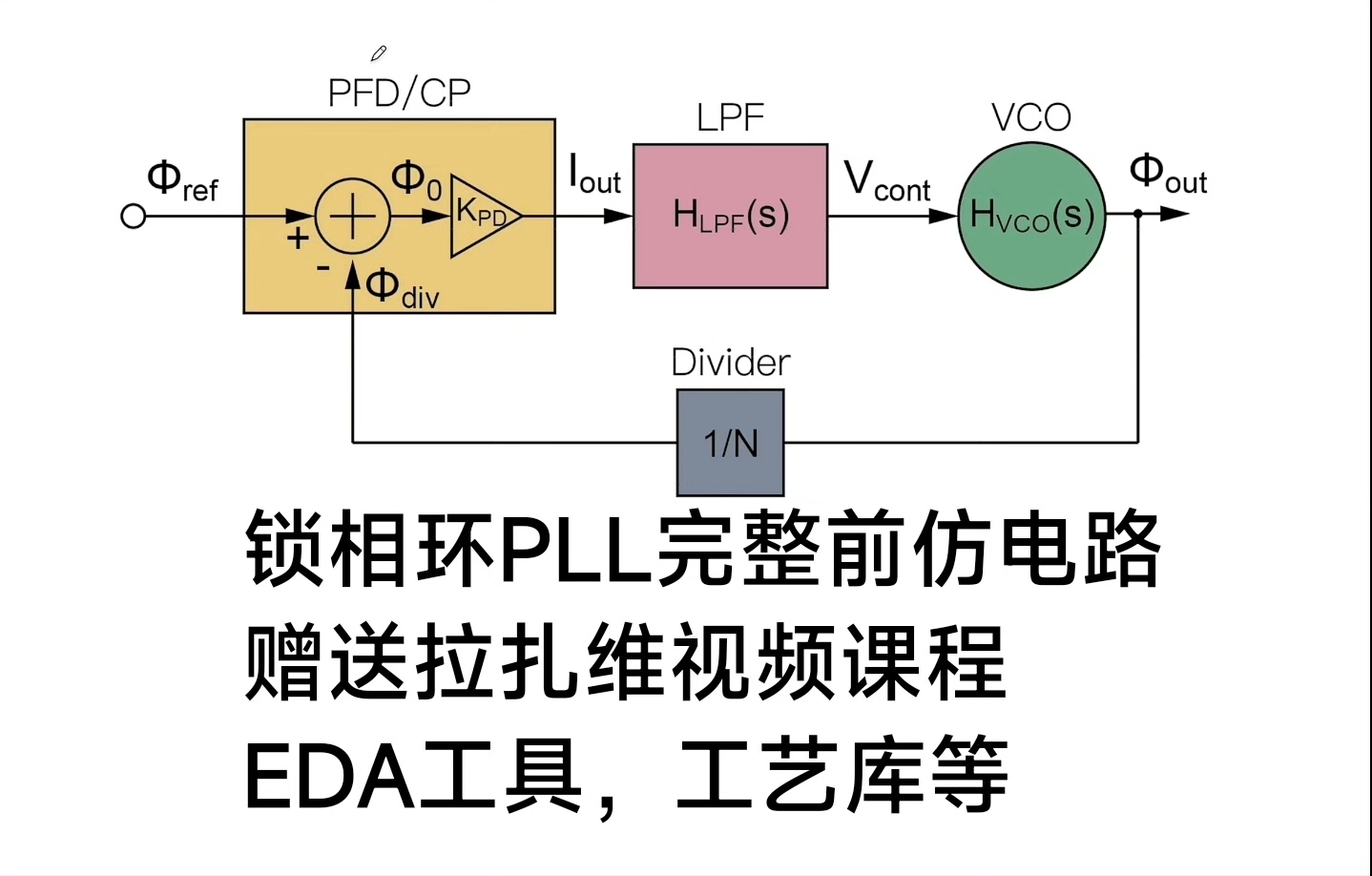

在设计一个完整的锁相环电路之前,我们首先需要了解锁相环的原理和各个模块的功能。锁相环主要由相位比较器、环路滤波器、电压控制振荡器和分频器组成。相位比较器用来比较输入参考信号和反馈信号的相位差,环路滤波器则根据相位比较器的输出来调整电压控制振荡器的频率,使其与输入参考频率保持同步。分频器则用来将振荡器的输出频率分频,得到所需的输出频率。

在设计中,每个模块都需要经过详细的测试和验证,以确保其功能正常。对于相位比较器、环路滤波器和电压控制振荡器,我们可以分别编写相应的testbench进行单独测试,并根据测试结果进行调整和优化。此外,为了保证整个锁相环电路的正确性和稳定性,我们还可以进行一些仿真实验,比如通过电路仿真软件进行时域和频域仿真,以验证电路的性能和稳定性。

在设计过程中,我们可以参考一些相关的设计资料和教程,以便更好地理解锁相环电路的原理和设计方法。另外,对于一些特殊的情况和需求,我们还可以使用一些辅助工具,比如MATLAB和Verilog-A建模推导,以进行更深入的分析和设计。

最后,在整个设计流程完成之后,我们可以进行前仿真来验证设计的正确性。通过前仿真,我们可以预先检测到可能存在的问题,并及时进行调整和修改,以确保最终的设计是可靠和稳定的。虽然在本文中没有提到版图设计,但在实际工程中,锁相环电路的版图设计也是非常关键的一步,通过合理的版图布局和布线,可以提高电路的性能和可靠性。

综上所述,本文围绕锁相环电路的设计和实现展开了讨论,对于每个模块都进行了详细的介绍和测试,并提到了一些辅助工具和仿真实验的使用。通过本文的内容,读者可以了解到锁相环电路的基本原理和设计流程,并在实际工程中应用。希望本文对于锁相环电路的设计和研究有所帮助,对读者能够在相关领域取得更好的研究和应用成果。

以上相关代码,程序地址:http://wekup.cn/747278137869.html

本文详细介绍了锁相环电路的设计,包括Ring_VCO结构、参数选择(如800MHz/1GHz输出、20MHz输入、40-50分频等)、以及使用MATLAB和Verilog-A进行模型建立。着重于测试、仿真和设计流程,旨在帮助读者理解和实践锁相环电路的构建。

本文详细介绍了锁相环电路的设计,包括Ring_VCO结构、参数选择(如800MHz/1GHz输出、20MHz输入、40-50分频等)、以及使用MATLAB和Verilog-A进行模型建立。着重于测试、仿真和设计流程,旨在帮助读者理解和实践锁相环电路的构建。

1129

1129

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?