FPGA采集CameraLink相机Full模式

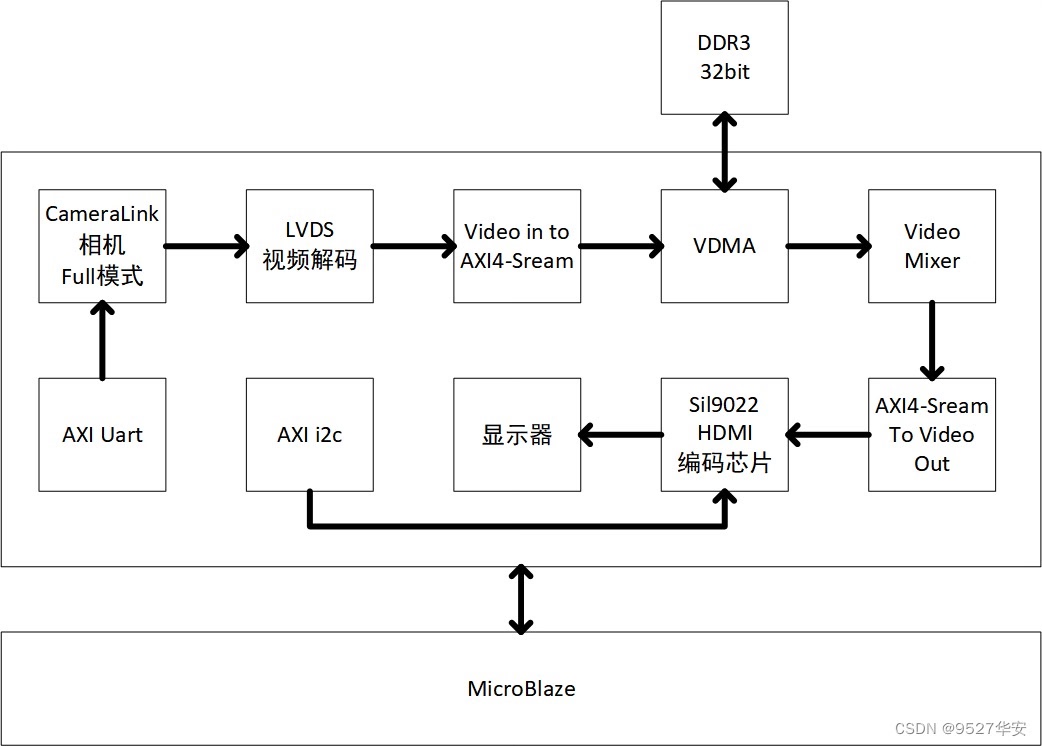

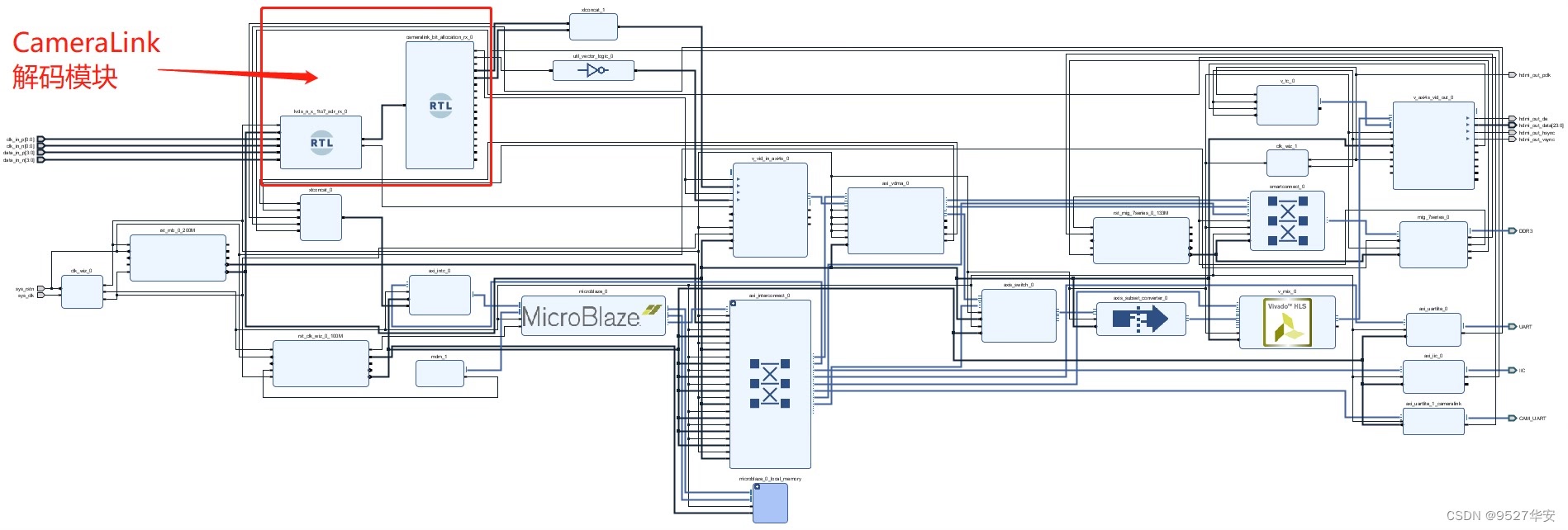

本文详细描述了FPGA采集CameraLink相机Full模式解码输出的实现设计方案,思路是这样的,CameraLink相机输入到FPGA板子,FPGA使用内部逻辑资源实现LVDS视频解码,解析出像素时钟、行同步信号、场同步信号、数据有效信号、以及像素数据,然后将视频转为Xilinx的AXI4-Sream的视频流,经VDMA送入DDR3缓存,然后读取出视频再经过AXI4-Sream to Video Out通过HDMI接口输出视频,这是Xilinx图像处理常用的套路,可谓相当精巧的方案

ID:65360721343787341

FPGA小白

FPGA采集CameraLink相机Full模式

在如今科技日新月异的时代,图像处理技术的发展越来越迅猛。而FPGA作为一种硬件加速的解决方案,其强大的计算能力被广泛应用于图像处理领域。本文将详细描述FPGA如何实现CameraLink相机Full模式解码输出的设计方案。

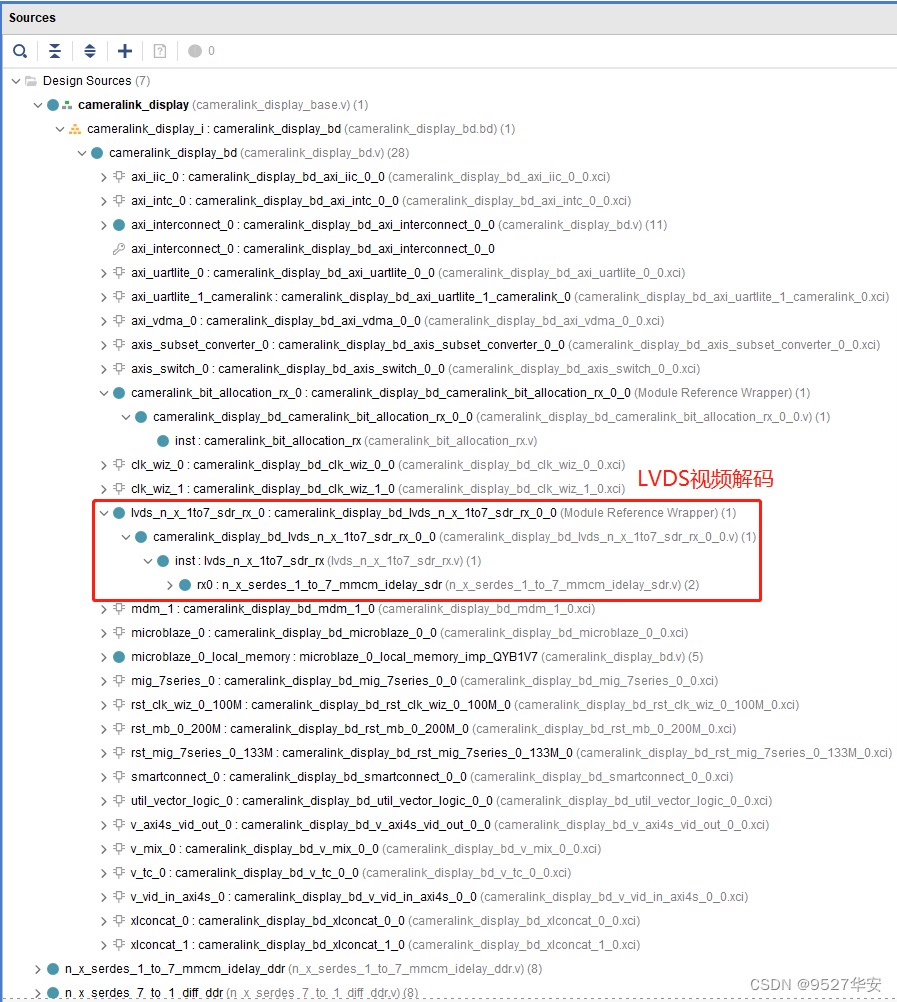

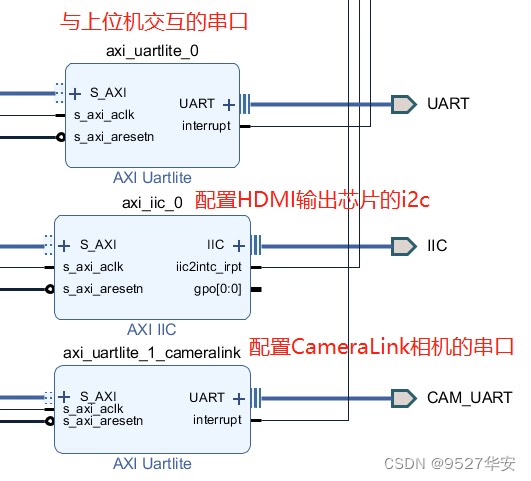

首先,我们先来看一下整体的思路。CameraLink相机的输入通过FPGA开发板连接,并利用FPGA内部的逻辑资源实现LVDS视频解码。解码的过程中,可以得到像素时钟、行同步信号、场同步信号、数据有效信号以及像素数据。

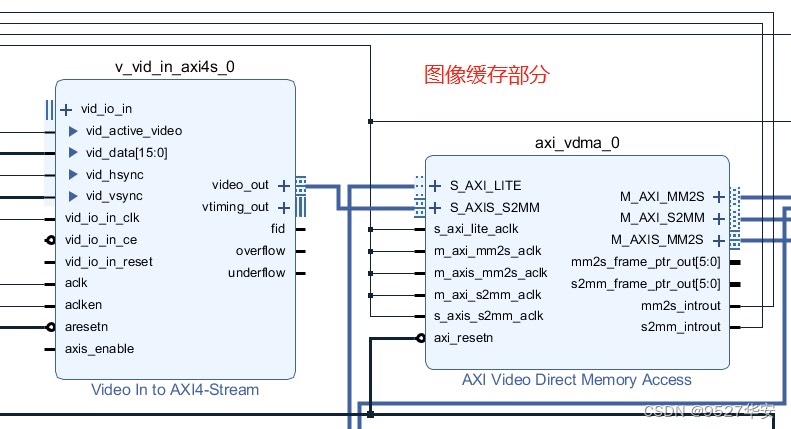

接下来的一步非常关键,我们需要将解码后的视频转换为Xilinx的AXI4-Stream形式的视频流数据。这里我们使用VDMA(Video DMA)模块,将视频数据存储到DDR3缓存中。VDMA模块提供了高带宽的数据传输通道,可以有效地实现视频数据的存取。

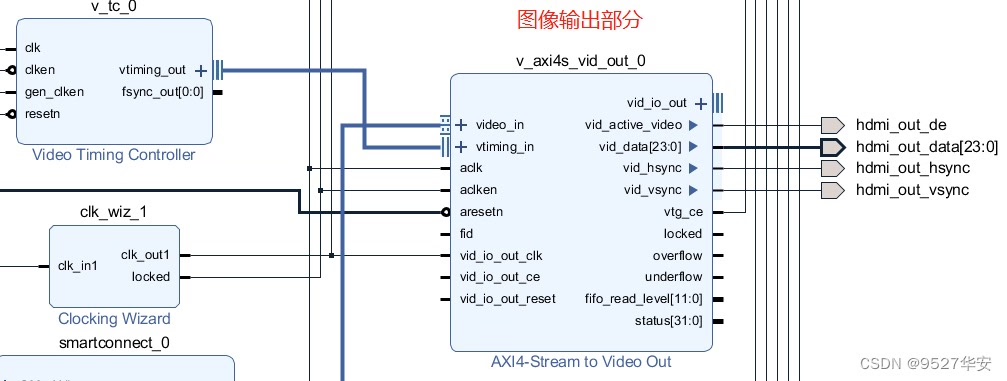

经过以上步骤,我们已经成功地将CameraLink相机的视频数据存储到DDR3缓存中。接下来的任务是将视频数据读取出来,并通过AXI4-Stream to Video Out模块通过HDMI接口输出视频。这个过程是Xilinx图像处理常用的套路,也是一种相当精巧的方案。

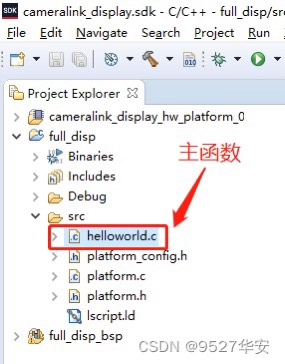

FPGA作为一种可编程逻辑器件,可以根据需求进行灵活的配置和设计。在本方案中,通过利用FPGA内部的逻辑资源和丰富的外设接口,我们成功地完成了CameraLink相机Full模式解码输出的实现。

此外,FPGA在图像处理领域还有许多其他应用。例如,可以利用FPGA实现图像滤波、图像增强、目标检测等功能。相较于传统的软件实现方式,FPGA在图像处理方面具有更高的性能和更低的延迟。

总结而言,本文详细描述了使用FPGA采集CameraLink相机Full模式解码输出的实现设计方案。通过利用FPGA内部的逻辑资源和外设接口,我们成功地实现了LVDS视频解码、AXI4-Stream视频流转换、以及HDMI视频输出等功能。这一方案不仅在技术层面上非常精巧,同时也为图像处理领域的发展带来了新的可能性。相信在未来的科技发展中,FPGA将继续发挥重要的作用,并为我们带来更多创新的解决方案。

【相关代码,程序地址】:http://fansik.cn/721343787341.html

2265

2265

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?