基于fpga的tcp乱序重排算法实现,通过verilog实现适用于fpga的tcp乱序重排算法,并通过实际数据测试验证。

代码里包含注释,可以明白每个模块的含义。

采用自创的乱序重排算法,易于在硬件中实现。

该算法和工程可用于实际应用、算法设计、研究学习。

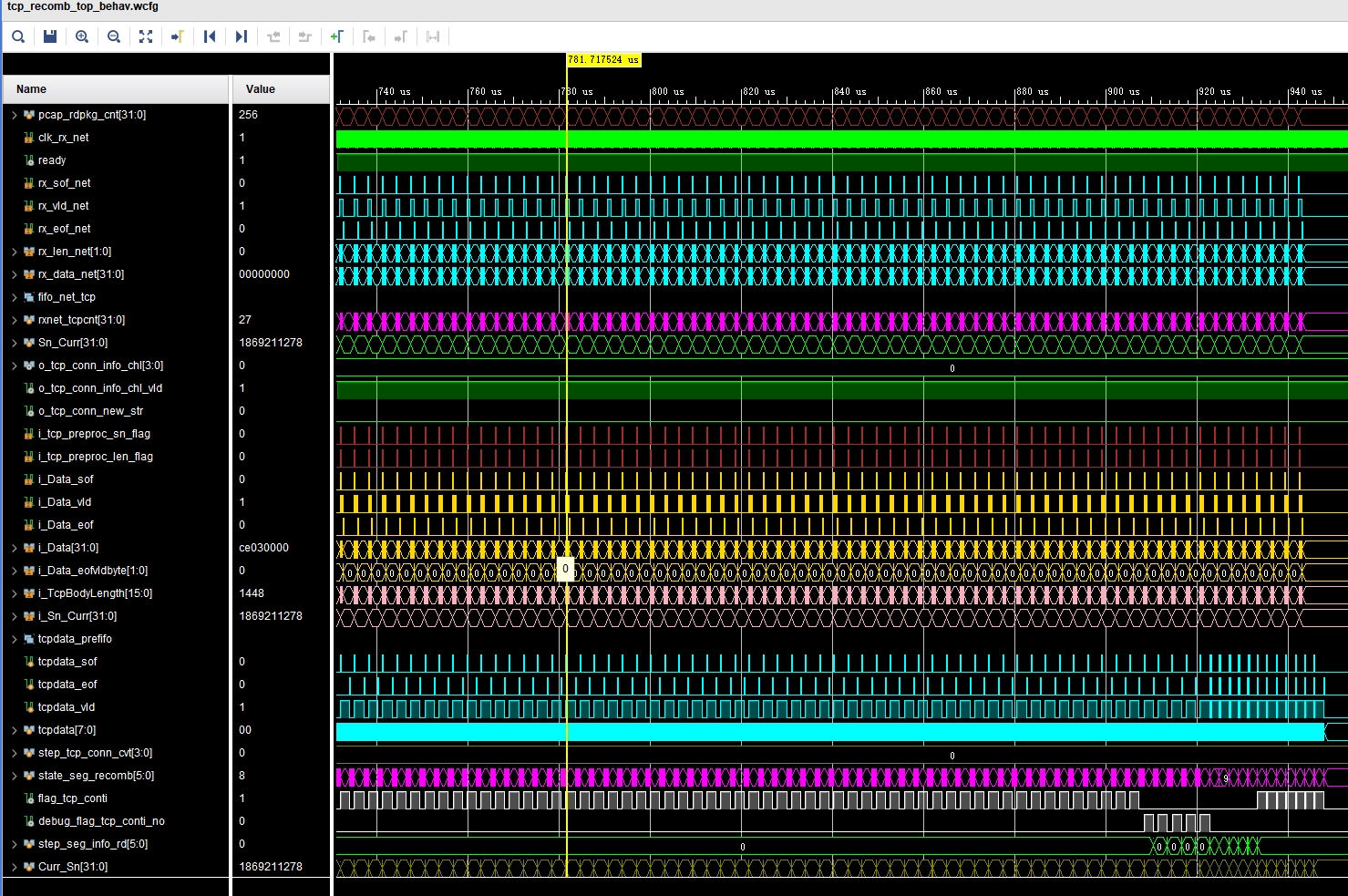

提供测试用的抓包文件,仿真结果。

解决棘手的fpga处理tcp乱序问题。

此工程在实际场景中多次测试,结果正确,性能良好。

可实现tcp的快速重排与恢复。

具有很强的实际意义和算法意义。

YID:87900679350854662

平芜尽处是春山

FPGA上的TCP乱序重排算法:从理论到实践

在数字化通信的世界里,TCP协议以其可靠的传输机制被广泛使用。然而,当数据在传输过程中出现乱序时,传统的TCP协议可能无法正常工作。针对这一棘手问题,本文将详细介绍一种基于FPGA的TCP乱序重排算法实现。

一、引言

在网络通信日益频繁的今天,数据的传输效率与可靠性变得尤为重要。当网络中存在延迟、丢包等情况时,TCP协议的数据包可能会出现乱序现象。这给接收端带来了不小的挑战,尤其是当数据量巨大时,传统的TCP协议可能无法有效处理这种情况。因此,我们设计了一种自创的乱序重排算法,并成功在FPGA上实现了该算法。

二、算法设计

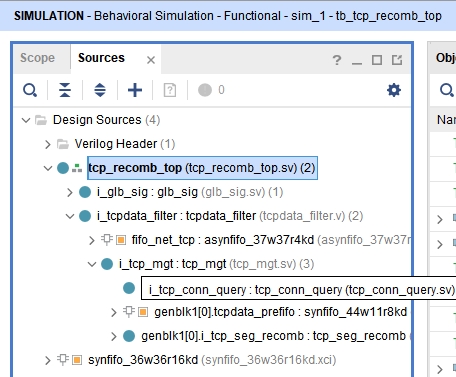

我们的算法采用了高效且易于硬件实现的策略。在Verilog编程语言中,我们设计了一个模块化的,包括数据接收、乱序检测、缓存管理以及重排输出等模块。每个模块都承担了特定的功能,并且都配备了详细的注释,以便于理解每个模块的作用。

三、硬件实现

FPGA的并行处理能力使得我们的算法得以高效实现。通过优化Verilog代码,我们成功地将算法转化为可在FPGA上运行的硬件逻辑。这不仅能快速处理大量的数据包,还能保证低延迟和高可靠性。

四、测试与验证

我们提供了实际的抓包文件以及仿真结果作为验证的依据。在实际场景中,我们的工程经过了多次测试,结果证明其能够正确且高效地处理TCP乱序问题。此外,我们还对算法的性能进行了评估,结果显示其具有很好的性能表现。

五、结果与讨论

我们的算法不仅解决了FPGA处理TCP乱序的问题,还实现了tcp的快速重排与恢复。该算法具有很强的实际意义和算法意义,为网络通信领域带来了新的解决方案。同时,该算法的设计与实现也为研究学习和工程应用提供了宝贵的参考。

六、代码与资源

以下是部分Verilog代码示例,包含了必要的注释以解释每个模块的功能:

// 数据接收模块

module DataReceiver (

// 输入输出端口定义 ...

);

// 模块内部逻辑 ...

endmodule

// 乱序检测模块示例

module ReorderDetection (

// 依赖DataReceiver的输出以及自身所需的输入端口 ...

);

// 乱序检测逻辑 ...

endmodule

此外,我们还提供了测试用的抓包文件以及仿真结果文件,以便读者能够更好地理解和应用我们的算法。所有这些资源都可在我们的官方网站或GitHub仓库中获取。

七、结语

通过本文的介绍,我们展示了一种基于FPGA的TCP乱序重排算法的实现方法。该算法不仅解决了FPGA处理TCP乱序的问题,还具有很强的实际意义和算法意义。我们相信,这一解决方案将为网络通信领域带来新的可能性,并为研究学习和工程应用提供有益的参考。

独家揭秘,点即得: https://pan.baidu.com/s/16VvteuL28lAosGzdPJEtpg?pwd=msh9

317

317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?