本编文章在ADI官方HDMI例程的基础上进行修改,实现视频通路,为使用ZYNQ视频处理做好必要准备。

在 【ZYNQ-7000开发之九】使用VDMA在PL和PS之间传输视频流数据 这篇文章中,介绍了如何使用VDMA传输stream类型的视频流数据,本次实验将结合【ZYNQ-7000开发之三】ZYNQ平台的HDMI驱动测试这篇文章,本次实验默认大家已经完成了【ZYNQ-7000开发之三】和【ZYNQ-7000开发之九,至少要完成【ZYNQ-7000开发之三】,本次实验将在【ZYNQ-7000开发之三】的基础上直接修改。

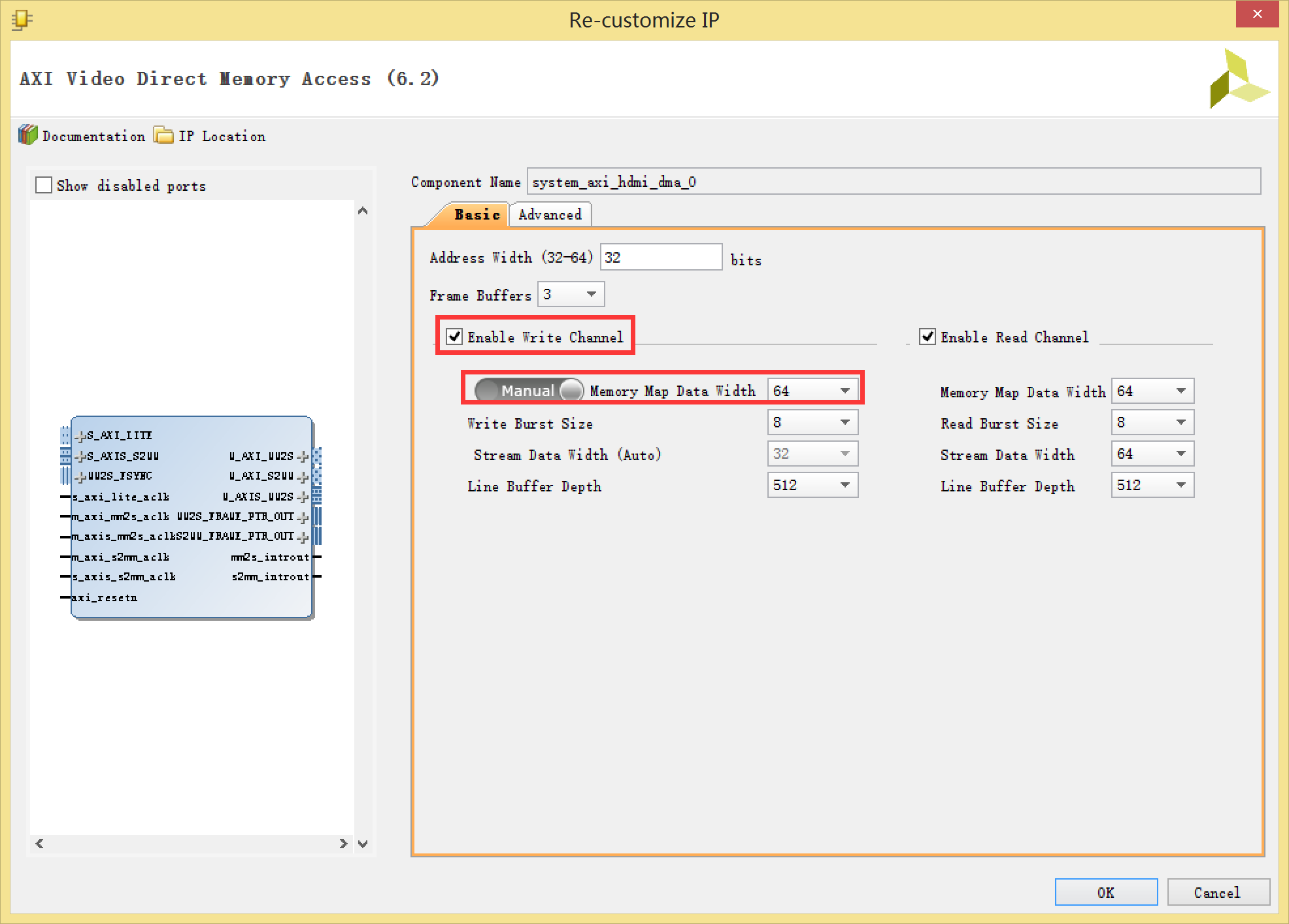

本篇文章的思想是使用TPG产生stream类型的数据,然后用VDMA转换成Memory Map类型的数据写入到DDR3缓存,最后再用VDMA 从DDR3读出来转换成stream类型,发送给HDMI控制器,进而显示在HDMI显示器上。

TGP VDMA等的规范说明可以到官网下载最新版本

本文所使用的开发板是Miz702(兼容zedboard)

PC 开发环境版本:Vivado 2015.2 Xilinx SDK 2015.2

其它:HDMI显示器,串口线

本文介绍如何在ZYNQ-7000平台上利用TPG生成视频流,通过VDMA转换数据类型并存储至DDR3,再由VDMA读取并经HDMI显示。详细步骤包括修改硬件系统工程,如配置VDMA和TPG IP,以及连接信号;接着修改软件工程,调整InitHdmiVideoPcore函数,最终在640*480分辨率下成功显示视频。读者可尝试不同分辨率及TPG输出类型。

本文介绍如何在ZYNQ-7000平台上利用TPG生成视频流,通过VDMA转换数据类型并存储至DDR3,再由VDMA读取并经HDMI显示。详细步骤包括修改硬件系统工程,如配置VDMA和TPG IP,以及连接信号;接着修改软件工程,调整InitHdmiVideoPcore函数,最终在640*480分辨率下成功显示视频。读者可尝试不同分辨率及TPG输出类型。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1622

1622

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?