先给出UG953对BUGHCE的介绍:

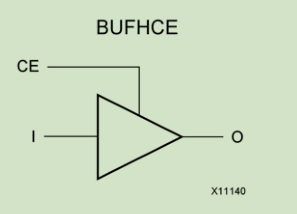

BUFHCE

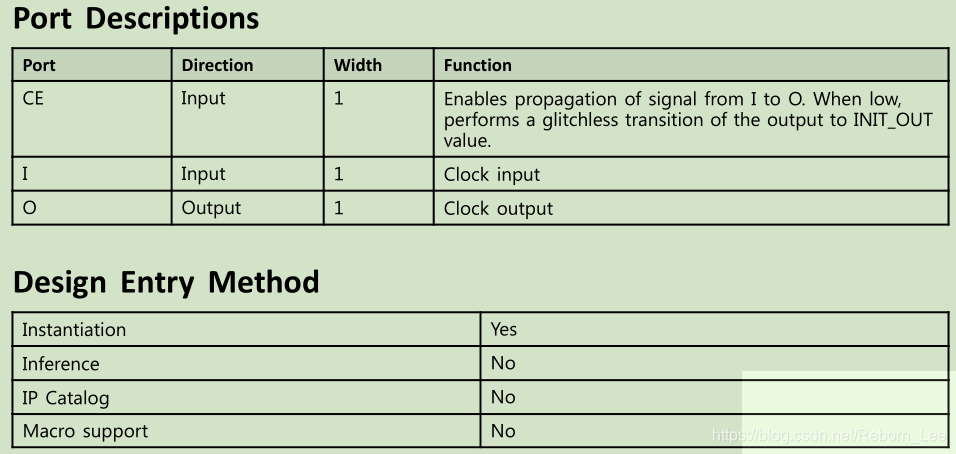

Primitive: HROW Clock Buffer for a Single Clocking Region with Clock Enable

BUFHCE原语允许直接访问全局缓冲区(BUFG)资源的时钟区域入口点。 这允许访问全局时钟网络的未使用部分以用作高速,低偏斜本地(单时钟区域)布线资源。 此外,时钟使能输入(CE)允许对时钟使能或门控进行更细粒度的控制,以允许电路或部分设计的功率降低,而不是经常使用。

Refer to the 7 series FPGA Clocking Resources User Guide for details about using this component.

CE: 允许信号从I传播到O.当为低电平时,执行输出到INIT_OUT值的无干扰转换。

Verilog Instantiation Template

// BUFHCE: HROW Clock Buffer for a Single Clocking Region with C

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?