一、实验目的

1. 学习掌握可综合 Verilog 语言进行 时序逻辑设计 的使用;

2. 学习测试模块的编写、综合和不同层次的仿真。

二、实验过程

一)时钟上升沿触发的D寄存器

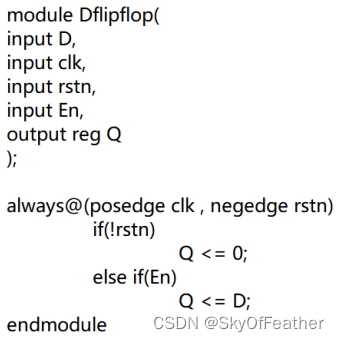

1) 源码

1. Dflipflop

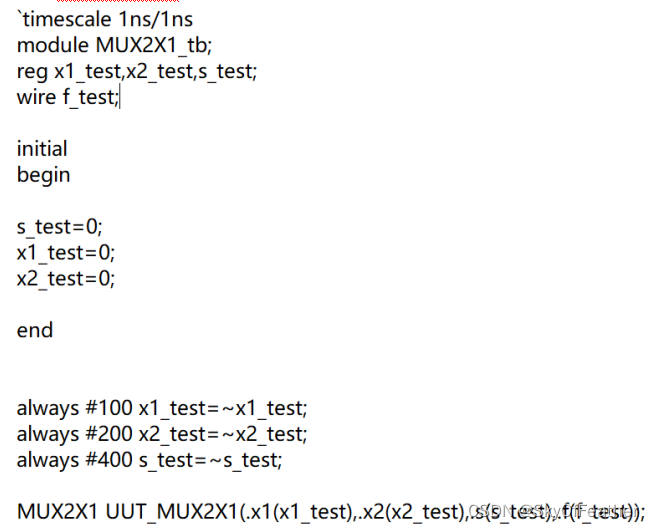

- Dflipflop_tb

- 生成波形与RTL图形

略

- 分析

D触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。在两个有效的脉冲边沿之间,D的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入端D必须有足够的建立时间,保证信号稳定。

一个时钟信号的上升沿来临时,将此时的输入D传输给输出Q;在时钟信号的其他阶段内,输出均保持不变。

根据波形分析可知,满足此要求。

- 4bBit具有并行加载功能的移位寄存器

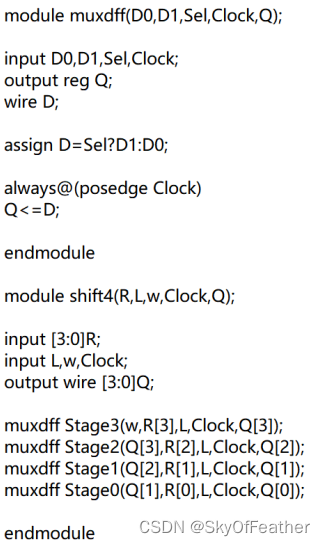

- 源码

- shift4

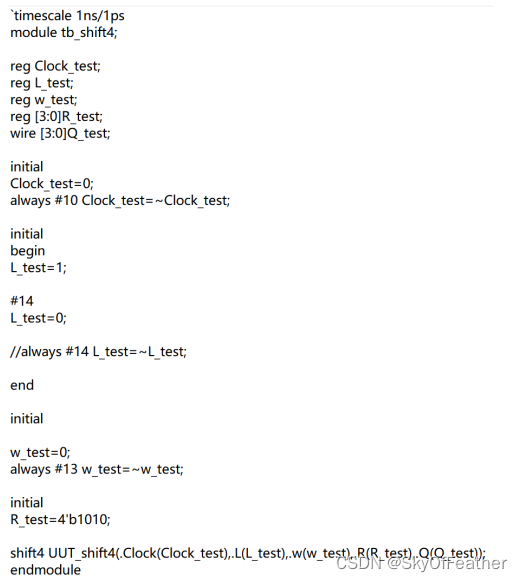

- shift4_tb

- 生成波形与RTL图形

略

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2369

2369

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?