随着制程推进至3纳米,单一芯片晶体管的密度已经逼近极限,因此半导体业除了持续向先进制程推进外,同时也寻找其他既能使芯片维持小体积,又能保有高效的方式,异质整合的概念因而萌芽。

异质整合广义来说,就是将两种不同的芯片透过封装、3D堆迭技术整合在一起,如逻辑芯片+记忆体、光电+电子元件等。

所以说将2种不同制程、不同性质的芯片整合在一起,皆可以称为异质整合,基于这个想法,衍生出2.5D、3D、Chiplets等封装技术。

CoWoS简介

CoWoS(Chip-on-Wafer-on-Substrate)是一种2.5D、3D的封装技术,可以拆成“CoW”、“WoS”两个面向。

CoW(Chip-on-Wafer)意思是指将芯片堆迭,而WoS(Wafer-on-Substrate)则是把芯片堆迭在基板上。

因此,CoWoS的意思就是把芯片堆迭起来,并封装在基板上,并根据排列的形式,分为2.5D与3D两种,此封装技术的好处是能够减少芯片的空间,同时还能减少功耗与成本。

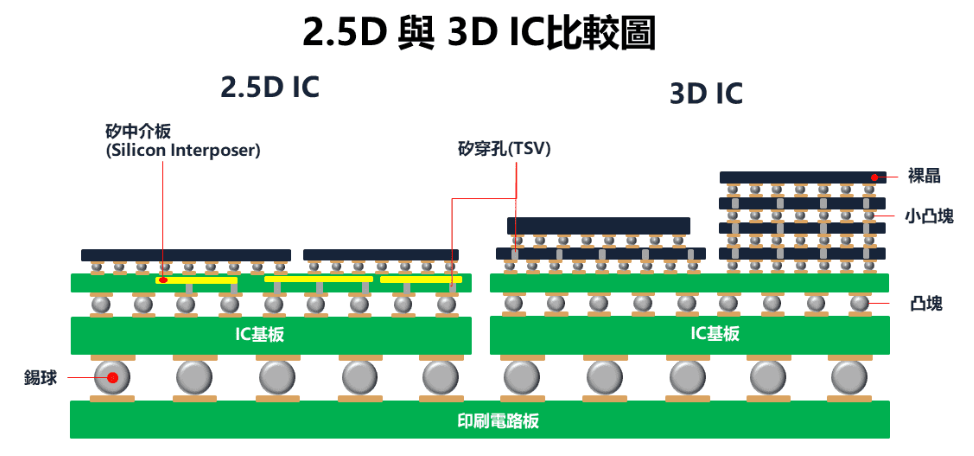

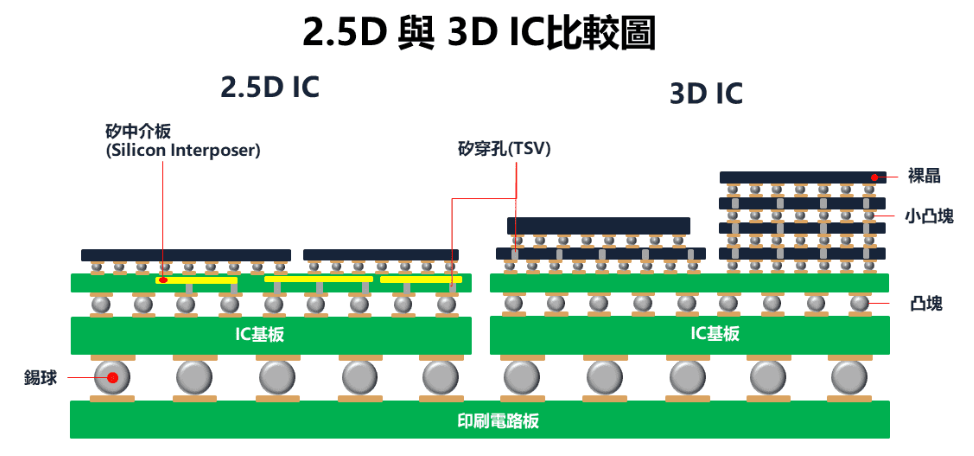

2.5D与3D封装示意图

其中,2.5D与3D的封装技术主要差在堆迭的方式。

2.5D封装最为人所知的就是台积电的CoWoS,其技术概念就是以水平堆迭的方式,将半导体芯片放在中介层之上或透过硅桥连接芯片,最后再透过封装制程连接到底层的基板上,让多颗芯片可以封装一起,达到封装体积小、功耗低、引脚少的效果,本质上仍然是水平封装,只是让芯片间的距离更加靠近。

AI浪潮进一步推升先进封装需求

由于CoWoS封装可以将各种芯片 封装并整合至基板上,这可以让芯片间的线路缩短,达到提高效能的效果,同时也能够节省功耗,故主要应用于消费性电子端,其中在高速运算的领域成长最快,而CoWoS主要有前段晶圆级制程与后段载板级制程,晶圆级制程主要会在晶圆厂完成,故传统封测厂难以切入。

这也是为什么当AI服务器需求攀高后,台积电产能会供不应求的原因所在。

在这个背景下,台积电就会因市场需求扩充CoWoS的产能,因此半导体设备的供应链就被市场认为是主要的受惠者之一。

- END -

2184

2184

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?