🎓 微机原理考点专栏(通篇免费)

欢迎来到我的微机原理专栏!我将帮助你在最短时间内掌握微机原理的核心内容,为你的考研或期末考试保驾护航。

为什么选择我的视频?

- 全程考点讲解:每一节视频都紧扣考试要点,拒绝冗余,专注于最关键的知识点。

- 系统且高效:我已经为你精心准备了系统的学习资料,让你不再迷茫。

🔗 点击这里观看我的视频讲解 🔗

我需要你的支持

我为这套视频投入了大量精力,希望它能对你的学习有所帮助。如果你觉得内容有用,请给我的视频点个赞、评论、并关注我,这将是我继续创作的最大动力!

🙏 感谢你的支持!祝你学有所成! 🙏

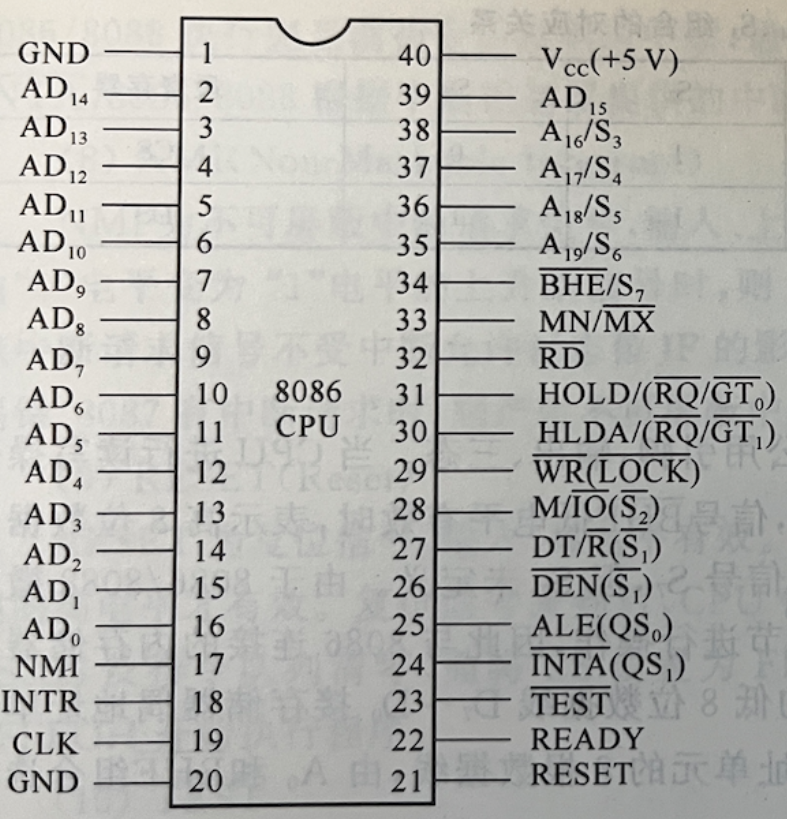

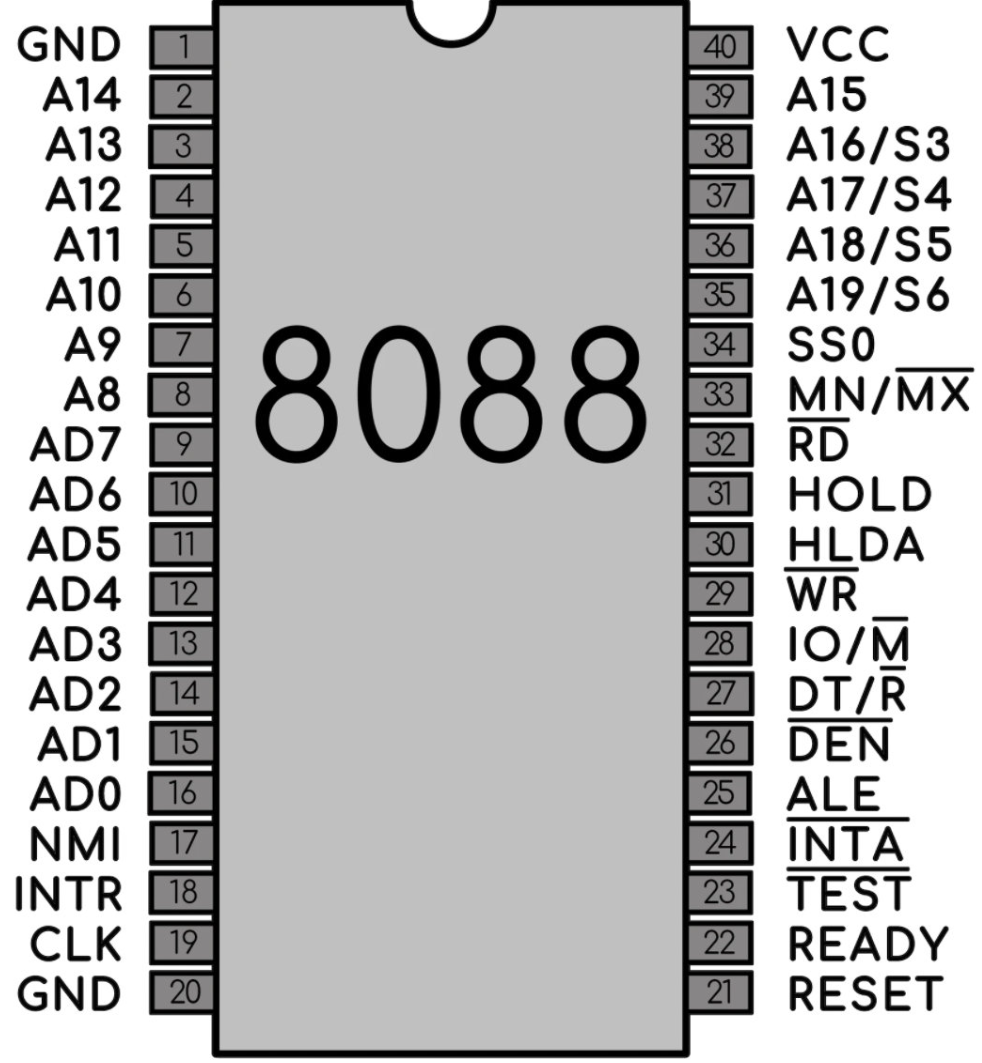

2.5 8086-8088CPU引脚

8086 微处理器信号描述

-

MN / MX ‾ \texttt{MN}/\overline{\texttt{MX}} MN/MX:最小模式和最大模式控制输入端。

- MN / MX ‾ = 1 \texttt{MN}/\overline{\texttt{MX}}=1 MN/MX=1时:工作方式设置为最小模式,在此方式下,系统全部控制信号由8086本身提供。

- MN / MX ‾ = 0 \texttt{MN}/\overline{\texttt{MX}}=0 MN/MX=0时:工作方式设置为最大模式,会外接其他CPU或扩展设备。

-

ALE:地址锁存允许信号

- 这是一个输出信号,表示当前总线上输出的是地址信息,需要进行地址锁存。该信号为正脉冲,在总线周期的 T1 状态时有效。

-

RESET:复位信号

- 这是一个输入信号,高电平有效。它用于复位微处理器,使其重新启动程序执行。

-

RD ‾ \overline{\texttt{RD}} RD:读信号; WR ‾ \overline{\texttt{WR}} WR:写信号

-

BHE ‾ / S 7 \overline{\texttt{BHE}}/\texttt{S}_7 BHE/S7:高8位数据总线允许/状态复用引脚

- 该引脚在 T1 状态时输出。如果信号为 0,表示高8位数据线(D15~D8)上的数据有效。

-

DEN ‾ \overline{\texttt{DEN}} DEN:数据允许信号

- 这是一个输出信号,低电平有效,提供给数据总线收发器(如 8286),表示 CPU 准备发送或接收数据。

-

M / IO ‾ \texttt{M}/\overline{\texttt{IO}} M/IO:存储器/外设控制信号

- 这是一个输出信号,用于区分存储器访问和 I/O 设备访问。信号为 1 表示访问存储器,为 0 表示访问 I/O 设备。

-

DT / R ‾ \texttt{DT}/\overline{\texttt{R}} DT/R:数据收发控制信号

- 这是一个三态输出信号,用于控制数据传输方向。信号为 1 时表示发送数据,为 0 时表示接收数据。

-

AD15~AD0:地址/数据复用引脚

- 在总线周期的 T1 状态用来输出要访问的存储器或 I/O 端口地址,在 T2~T4 状态,作为数据传输线。

-

A19/S6~A16/S3:地址/状态复用引脚

- 在 T1 状态:输出高 4 位地址,在 T2~T4 状态:输出状态信息。

- 访问存储器时:A19~A16 与 AD15~AD0 组成 20 位地址。

- 访问 I/O 端口时:不使用这 4 条引线。

-

READY:“准备好”信号

- 由所寻址的存储器或 I/O 端口发来的响应信号,表明存储器或 I/O 端口的状态。CPU 在 T3 采样 READY,如果 READY=0,则在 T3 后插入一个或多个 TW,直至 READY=1,进入 T4,完成数据传送,从而结束当前总线周期。

-

HOLD:总线保持请求信号

- 这是一个输入信号,高电平有效,用于请求 CPU 释放总线。

-

HLDA:总线保持响应信号

- 这是一个输出信号,高电平有效,表示 CPU 已同意 HOLD 信号并释放总线。

奇区和偶区

8086 的 1MB 存储空间实际上分为两个 512KB 的存储体,分别叫奇存储体(奇区)和偶存储体(偶区)。

- 偶存储体与数据总线 D7~D0 相连,该存储体中每个地址均为偶数地址。

- 奇存储体与数据总线 D15~D8 相连,该存储体中每个地址均为奇数地址。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?