目的

基础时钟木块提供MSP430Fx1xx的各个外设或者CPU的时钟,这里我们对这个模块进行配置,通过IO口进行时钟的输出用以验证配置的正确性。(DCOCLK有点复杂,这里只测试源时钟是XT1和XT2的ACLK、SMCLK、MCLK的输出)

组成

基础时钟模块由以下三个时钟模块组成:

ACLK(Auxiliary clock,辅助时钟) ACLK由XT1晶振通过分频得到,XT1晶振可以选择32.768KHz的低速晶振,也可以选择450KHz-8MHz的高速晶振,但是需要在寄存器中进行相关配置。

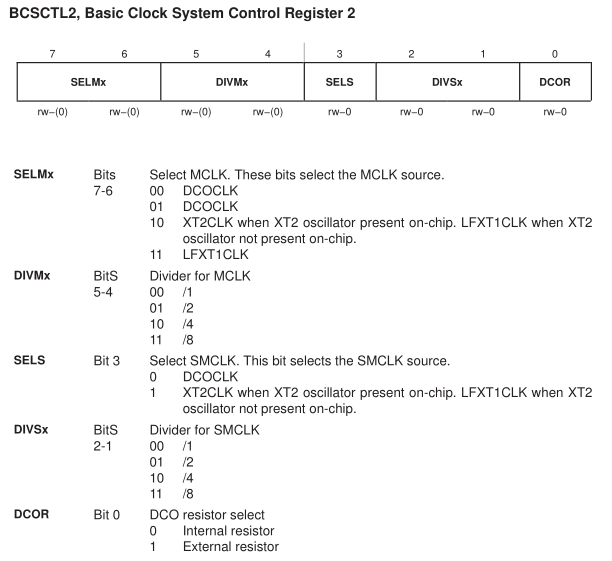

MCLK(Masterclock,主时钟) MCLK是CPU运行时的时钟,其源时钟可以从XT1晶振、XT2晶振和内部DCO时钟进行选择,然后通过分频可以得到。

SMCLK(Sub-mainclock, 从主时钟) SMCLK是内部设备时钟,其源时钟可以从内部DCO或者XT2晶振时钟进行选择(如果没有焊上XT2晶振,也可以用XT1),然后通过分频得到。

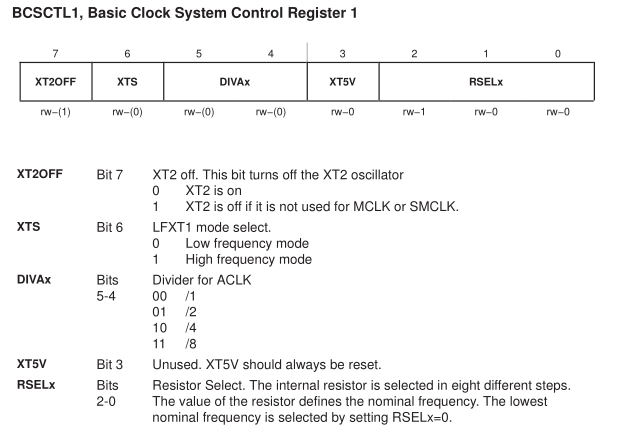

涉及寄存器

XT2OFF位初始化后为1,即关闭XT2晶振,我们可以将其置0开启XT2。

XTS位是XT1的晶振选择。若XT1选择32.768kHz的低速晶振,该位必须置0;若XT1选择450KHz~8MHz的高速晶振,该位必须置1。

DIVAx是寄存器的第5、4位,通过配置这两位对XT1晶振时钟进行分频,具体分频如上图所示。当这两位为全1时,ACLK是XT1晶振时钟的8分频。

RSELx 这是与DCO相关的,先不讲。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6225

6225

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?