异步电路学习笔记

文章目录

基本概念

异步电路概述

同步电路和异步电路的特点

当前,大部分的数字电路都是同步的。同步数字系统中,所有状态的翻转发生在同步时钟的跳变沿,系统的状态保存在寄存器中。组合逻辑根据系统的当前状态和输入信号产生系统的新状态和输出信号,新状态在时钟跳变沿被锁存到寄存器中。因此,同步电路的设计者必须控制组合逻辑延时,使其在最坏条件下满足寄存器的建立时间和保持时间。同步电路作为主导设计方法,其成熟的EDA工具几乎覆盖整个大规模数字电路设计流程,从高层次语言描述到一个完整的芯片版图只需要极少的人工干预。

然而,随着芯片特征尺寸的缩小、面积的增大以及时钟工作频率的提高,特别是片上系统(System on a chip,SoC)的出现,全局同步时钟的实现已越来越困难,同时全局同步时钟导致的功耗问题令设计者束手无策。基于以上原因,异步电路重新引起学术界和工业界的关注。

异步电路没有全局时钟,系统各模块之间的数据交换通过相互之间的握手过程完成。在这种情况下,一步集成电路的低功耗、潜在的高性能和便于模块化设计的优点逐渐显现出来。

同步电路的问题

同步电路占据数字大规模集成电路的主导地位,其电路系统要求系统各部分的时钟是同步的或者是几乎同步的,然而时钟信号是电信号,其传输过程和其他普通信号一样存在延时,如果时钟信号的延时占据时钟周期的很大部分,则各部分电路会出现同步失效的问题。同步电路的问题主要体现在以下几个方面:

- 时钟偏移:由于时钟信号传输延时客观存在,时钟信号到达芯片各处电路的时间存在差异,这一差异称为时钟偏移。同步电路的时钟周期如下式所示:

T c l k = T l o g i c + T s + T c q + T c l k _ s k e w T_{clk}=T_{logic}+T_s+T_{cq}+T_{clk\_skew} Tclk=Tlogic+Ts+Tcq+Tclk_skew

其中, T l o g i c T_{logic} Tlogic为组合逻辑延时; T s T_s Ts和 T c q T_{cq} Tcq分别为寄存器的建立时间和寄存器的锁存延时; T c l k _ s k e w T_{clk\_skew} Tclk_skew为时钟偏移时间。

- 功耗问题:CMOS工艺是一种很好的低功耗工艺,只有当逻辑门发生翻转时才产生功耗。在数字系统中,通常某一时刻只有一部分的逻辑门在工作,另一部分逻辑门是不需要发生翻转的。但是在同步电路中,很大一部分的逻辑门直接连接在时钟信号上,而且时钟驱动器通常是电路中最大的逻辑门,因为停止或者启动一个高速时钟不是一件容易的事情,所以这些逻辑门通常无时无刻不在发生翻转,即使此时只有很小的一部分电路在工作也是如此。在现代高速微处理器设计中,近一半的功耗消耗在了时钟电路中。

- 多时钟域集成问题:随着芯片集成规模的增大,特别在SoC设计中,通常存在多个不同源时钟的模块。在每一个时钟域内部,可以采用同步电路来实现,而时钟域之间的接口同步电路就很难胜任。全局异步局部同步(GALS)是目前解决这一问题的主要办法。

异步电路的优势与问题

与同步电路不同,异步电路通过使用大量本地握手信号来完成整个电路的时序控制工作,每个电路模块在握手信号的有效跳变沿后开始工作,在工作完成后产生相应的完成信号。此特点使得异步电路具有以下几个优势。

- 功耗低

同步电路中,时钟工作频率必须满足最大负荷的要求,导致电路功耗高,而门控时钟技术只能有限地改善功耗浪费的现象。异步电 路仅在需要处理数据时才消耗能量,而且异步电路由于细粒门控时钟门和零待机功耗小 ,可以在零功耗无数据状态与最大吞吐状态 之间迅速切换,不需要任何辅助电路。

- 运行速度快

同步电路工作时需要考虑电路的最坏情况延迟,而异步电路的性能则由电路的平均延迟决定,因此理论上可以比同步电路达到更高 的速度小。在小线宽集成电路工艺中,由于工艺误差,电路延迟分布较大,异步电路有可能达到比同步电路更好的性能。

- 电磁兼容性好

CMOS 电路仅在开关时产生电流,而同步电路的时钟使电路同时开关,造成很大的瞬时电流,这样就产生了很强的电磁干扰;而 且,时钟的固定周期使这些能量集中在时钟基波及其谐波附近的很窄的频谱范围内。异步电路的局部工作时间倾向于随机分布,每 个单元在收到其他部分的输入信号后才开始工作。这样,电路中没有类似同步电路在特定时刻上的大电流瞬时值,仅产生一些在时 间上分布的小电流峰值,辐射功率也小;而且,电路的工作没有锁定在一个固有的频率上,使辐射功率不会集中在特定的窄带频谱 中,而是在大范围上均匀分布。

- 工艺可以移植性和环境自适应性好,可靠性高

异步电路对信号的延迟不敏感,对小线宽集成电路工艺的适应性较强。当集成电路线宽达到深亚微米时,由 连线寄生参数引起的信 号延迟会超过由电路单元引起的延迟,在这种情况下,在完成电路的物理设计之前无法得到较准确的电路延迟信息。另外,如果改变 集成电路制造工艺,那就需要重新设计电路逻辑甚至电路结构以满足时序要求。异步电路使用握手信号进行通信,电路的延迟只会 影响工作速度而不会影响电路行为,因此电路的物理设计比较简单,并且对集成电路制造工艺的偏差不敏感。

- 模块化易于集成

异步电路的接口信号显式包含了模块的时间特性,因而易于模块间的互连。同步电路中,模块接口信号的时间特性是相对于该模块 的内部时钟的,这样不同时钟域模块之间的互连问题就很难解决,模块之间的时序验证也很难使用工具自动完成。而异步电路简单 的握手接口特性很好地解决了模块互连和时序验证问题。模块之间信号只需满足相应的异步通讯协议,而无需满足信号相对模块内 部时钟的严格时序要求。

-

可避免时钟偏移问题

随着单芯片系统的增大和互连线延迟在整个电路延迟中所占的比例增大,同步电路的时钟偏移越来越难控制,设计难度越来越大。异步电路用大量本地时序控制信号取代整体时钟,避免了时钟设计问题。

虽然,异步电路在以上几个方面优于同步电路,但异步电路的问题也同样明显。

- 相对于同步电路,异步电路中信号的每一次翻转都代表一次操作。任何不需要的信号翻转,例如噪声,都可能会引起电路功能失效,因而异步电路设计需要花费大量力气来消除电路输出的竞争冒险和毛刺;

- 为了获得高鲁棒性的电路,异步电路需要额外的门单元。任意异步模块之间的数据交换,都需要额外的控制电路来完成异步握手协议;

- 对于一个复杂数字系统设计,完全靠手工完成几乎是不可能的事情,然而现阶段异步电路设计缺少成熟的EDA设计工具,对同步电路设计广泛适用的EDA工具,例如自动布局、自动布线、逻辑综合都不适用于异步电路设计;

- 异步电路由于其数据驱动的特点,使其性能分析与优化异常困难。同步电路关键路径(两个寄存器之间的最大延时的组合逻辑路径)延时决定电路性能的评估方法同样不适用于异步电路。

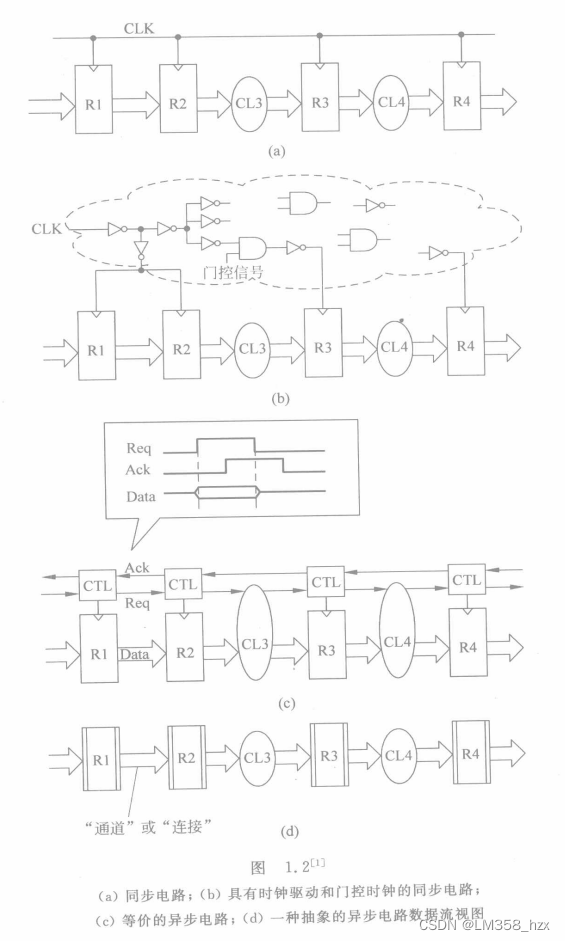

时钟和握手

在异步电路当中,相邻寄存器之间的握手信号代替了时钟信号,例如基于握手协议的请求-应答信号,如图 1.2©所示。在后面的章节中将看到握手协议和数据编码,在此,先做一些说明,如图 1.2(d)所示。

- 将连接一个寄存器和下一个寄存器的数据和握手信号称为“数据通道”或“连接”,如图 1.2©所示。

- 将存储在寄存器中的数据称为打上数据值的令牌(那些数据在令牌通过组合电路的过程中可能会改变)。

- 组合电路对寄存器间的握手是透明的;组合电路在它的每一个输入吸收一个令牌,执行计算,而后再将令牌释放到它的每一个输出连接(类似在 Petri net 中的一个转换)。

这样看来,异步电路仅仅是一个静态的数据流结构。要保证正确的操作,要求数据令牌在电路中“流动”的过程当中不会消失,一个令牌不会覆盖另一个,新的令牌不会消失。这需要遵循一个简单的规则:如果一个寄存器后面的寄存器输入并存储了这个寄存器先前存储的数据令牌,那么该寄存器将会从它前面的寄存器输入并存储一个新的数据令牌(前面和后面寄存器的状态是由各自到来的请求和应答信号来表示的)。

按昭这个规则,数据从一个寄存器复制到沿着电路路径的下一个寄存器。在这个过程当中,下一级寄存器将经常持有复制的相同数据,但是旧的复制数据将随后被一个新值有序地覆盖掉,一个连一个的握手周期将总是精确地传输完一个数据令牌。理解这种所谓的“令牌流游戏”对于有效的电路设计非常关键。

“握手通道和数据令牌”非常有用,它等价于同步电路中寄存器传输级的抽象概念。我们称为数据流抽象概念,它将电路结构和功能与电路的具体实现区别开来。另一个重要的信息是:寄存器之间的握手控制令牌的流动,组合电路模块对握手必须是充分透明的。组合电路确保这个透明并不容易,它比传统的组合电路更复杂,采用术语“功能模块(function block)”来表示输入和输出端口是握手通道或连接的组合电路。

图 1.2(b)中的同步电路由一个和周期时钟信号同相位的时钟脉冲控制,然而图 1.2©中的异步电路是由一个可以在任何时间产生的局部时钟脉冲控制。这个局部的握手确保了时钟脉冲只在需要的时间和地方产生。这样,时钟脉冲具有随机性,从而可以产生较少的电磁辐射和更平滑的供电电流,不会出现同步电路中的大的峰值电流。

异步电路分类和C单元

异步电路大致可以从握手协议、数据编码方式和延时模型三个方面加以分类,这样能组合出很多种异步电路的工作模式。本节详细描述异步电路的分类及其基本单元:C 单元。

握手协议

握手协议是保证异步电路各个组件之间数据流动并且不发生冲突的一种机制。握手协议可以分为四相位握手协议和两相位握手协议。

四相位握手协议

四相位握手协议也被称为归零(return-to-zero,RTZ)握手协议,归零信号也被称为“电平信号”,如图 2.1(a)所示。这里的“四相位”(4-phase)是指通信动作的次数:①发送端准备好数据后会将请求信号置高;②接收端接收数据后将应答信号置高;③发送端将请求信号置低作为响应(此时数据可以不再保持有效);④接收端通过将应答信号置低来做出应答。此时,发送端就可开始下一个通信周期。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BH2B5Bcs-1666168433722)(异步电路学习笔记20221017.assets/image-20221017205338527.png)]](https://img-blog.csdnimg.cn/60e7a8cf2792427a82c1e8e03b2e9030.png)

两相位握手协议

上述四相位握手协议的缺点是多余的归零翻转造成了不必要的时间和能量的损耗,图2.1(b)所示的两相位协议就可避免这一缺点。在两相位握手协议中,请求和应答信号都使用信号线上的电平翻转沿来进行编码。在这种编码中的0→1和1→0翻转是没有区别的,它们都代表一次“信号事件”(signal event)。理想情况下,两相位握手协议应该比四相位握手协议在电路实现上有着更快的执行速度,不过由于不同问题所对应的电路实现往往复杂多变,因此不能简单地说哪种协议是最好的。

数据编码方式

数据编码方式是指数据信息在异步逻辑中以何种方式来表达,异步电路设计中采用的编码方式主要包括单轨编码和双轨编码,此外我们还将介绍一种1/4编码方式。

单轨编码

单轨编码(single-rail encoding)方式中,一根数据线表示一比特信息,发送方和接收方之间的时序同步通过额外的“请求”和“应答”信号来完成。单轨编码也被称为捆绑数据(bundled-data)编码,也就是说,在数据信号采用普通布尔电平进行编码的同时,还包含单独的请求和应答信号(与数据信号“捆绑”在一起),如图2.1(a)所示。单轨编码方式主要基于假设异步电路的“请求”信号线的延时不小于相应的数据通道延时。由于单轨编码可以得到和同步电路相当的电路面积,所以在异步电路设计中被普遍采用;而且,数据通道可以用传统的同步电路设计工具得到。

双轨编码

双轨编码(dual-rail encoding)也称为延时不敏感编码(delay-insensitive,DI encoding),如果接收方能够从传送的数据中检测出完成编码标记,该编码方式就称为不敏感编码。延时不敏感编码的异步电路使用带冗余的逻辑表达式,其中一些输出值表示输出是有效的,另外一些输出值则表示输出是无效的。所以,延时不敏感编码电路不需要“请求”信号,但是接收方需要额外的硬件产生完成信号。

双轨编码中一比特信息由两根线表示,也就是将待传输的每一位信息的请求信号和数据信号编码在一起,用两根线来传输一个数据位。具体来说,双轨编码中每个数据信息d都采用两个请求线表示:一个请求线d.t用来表示逻辑1(真),另一个请求线d.f用来表示逻辑0(假)。其中(0,0)表示空闲状态,(0,1)和(1,0)代表逻辑“0”和逻辑“1",(1,1)是非法的。与单轨电路相比,双轨编码会导致过大的面积代价和更高的功耗。

一个更加抽象的四相位握手的示意图,如图2.2所示:①发送端产生一个有效码字;②接收端接收这个码字并置应答信号为高;③发送端通过产生一个空码字作为响应;④接收端通过置应答信号为低来做出响应,这时候发送端就可开始下一个通信周期。更抽象一些,在通道上观察到的就是被空码字隔开的有效码字数据流。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-hKctUsmo-1666168433723)(异步电路学习笔记20221017.assets/image-20221017210809425.png)]](https://img-blog.csdnimg.cn/60f8391d6b844cd4818ef12730663a65.png)

现在我们将这种方法扩展到多个并行位的(bit-parallel)通道。一个N位数据通道可以简单地通过并接N个线对来实现,每个线对都采用上面的编码方式进行编码。接收端总能检测到所有位都为有效的情况(以将应答信号置高作为响应)和所有位都为空的情况(以将应答信号置低作为响应)。这个过程从直觉上看虽然不难理解,但是也需要有一些数学推导做基础实际上,双轨编码是延迟不敏感编码码组家庭的一个很简单的成员门口,它有一些很好的特性:

(1) 任何双轨码字的并接又是一个双轨码字。

(2) 对于一个给定的N(通信中的数据位宽),所有可能的码字集合可以划分为三个集合:

-

N个线对都是{0,0}的空码字。

-

中间过渡码字,这时一部分线对处于空值,而另外的线对都是有效数据。

-

2 N 2^N 2N个不同的有效码字。

图2.3是一个N位通道的握手示意图:接收端首先看到空码字,然后是一列中间过渡码字(越来越多的位/线对变为有效),最终变为有效码字。接收到这个有效码字并进行应答后,接收端将看到一组中间过渡码字(越来越多的位/线对变为空),最终变为空码字,接收端通过将应答信号置低作为响应。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Mad1VqoT-1666168433723)(异步电路学习笔记20221017.assets/image-20221017211133412.png)]](https://img-blog.csdnimg.cn/a2085c8a00584994926f8c4dfe02bae4.png)

1/4编码

1/4编码是指4根线被用来并行传递2比特信息,其中(0,0,0,0)代表空的编码,(0,0,0,1)、(0,0,1,0)、(0,1,0,0)和(1,0,0,0)分别代表数据0、1、2和3。1/4编码可以降低DI系统的开关动作:并行传输2比特信息,1/4编码和双轨编码电路的面积代价是相同的(2个双轨通道),但是前者的信号跳变要少50%。双轨编码和1/4编码(one-of-four encoding)是两种常用的DI编码。

延迟模型

在逻辑门级,按照异步电路采用的延时模型,异步电路被分为有限延时和无限延时。有限延时模型认定所有的逻辑门单元和连线的延时信息是已知,或至少是有限的。基于有限延时模型的异步电路和同步电路的设计方法是一样的,这种方法在早期的异步电路设计中被采用。由于有限延时模型可以得到更小的电路实现,所以还会被用于异步电路的数据通道的设计。

目前,异步电路一般都采用无限延时模型来设计。也就是说,逻辑门和连线延时是未知的,电路设计不用考虑延时分布,而利用控制电路或状态机。下面简单介绍几种特殊的无限延时模型:速度无关电路、延迟不敏感电路和准延迟不敏感电路。

速度无关电路

下面以图2.4为例来说明异步电路类型的划分。这个图表示了三个逻辑门:A、B和C,门A的输出信号连接到门B和C的输入。逻辑门A、B和C的延迟分别为 d A d_A dA、 d B d_B dB和 d C d_C dC,连线延迟如图所示分别为 d 1 d_1 d1、 d 2 d_2 d2和 d 3 d_3 d3。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-AoLyXEpK-1666168433723)(异步电路学习笔记20221017.assets/image-20221017212156611.png)]](https://img-blog.csdnimg.cn/eb1a3b24b5ef4c02a6264b441dd8f79f.png)

速度无关电路(speed-independent,SI)中假定所有的逻辑门都是有上界的正延时(但数值可能不确定),所有的连接线都是理想的零延时。以图2.4为例,速度独立电路的条件就是逻辑门延时 d A d_A dA、 d B d_B dB和 d C d_C dC为正值,且 d 1 d_1 d1= d 2 d_2 d2= d 3 d_3 d3=0。但是在现在的半导体工艺条件下,连线延时为零是不符合实际情况的。不过通过假定 d 1 d_1 d1和 d 2 d_2 d2的取值并要求 d 2 d_2 d2= d 3 d_3 d3,连线延时就可以与门延时组合在一起,从理论上这种电路仍然是速度独立电路。

延迟不敏感电路

延迟不敏感电路(delay-insensitive,DI)模型中假定所有的逻辑门和连线都是有正上界的正延时(但数值可能不确定)。以图2.4为例来说明,延迟不敏感电路也就是说d d A d_A dA、 d B d_B dB、 d C d_C dC、 d 1 d_1 d1、 d 2 d_2 d2和 d 3 d_3 d3值任意,不影响电路正常工作,这类电路具有很好的鲁棒性。还有一种延迟不敏感的电路形式是Muller模型,这里连线部分(在分叉之后)被建模为缓冲器部件,如果这个等价的电路模型是速度独立的,那么原电路就是延迟不敏感的。

准延迟不敏感电路

一般把那些在连线分叉(fork)处的线段延时相同即

d

2

d_2

d2=

d

3

d_3

d3,而其余部分都是延迟不敏感的电路称为准延迟不敏感电路(quasi-delay insensitive,QDI)。通过认真的电路设计确保信号在这些连线分叉的所有终点都同时发生变化,即所有分支具有相等延时的分叉,又称为等时叉(isochronic fork)。典型的等时叉在门级电路中用来控制连线延时。

延迟不敏感电路是很少的,在文献中涉及的延迟不敏感电路一般是指准延迟不敏感电路。那些需要精细的延迟时间假设才能正常工作的电路则称为自定时电路。

从上面的叙述中可以很清楚地看到速度无关电路和延迟不敏感电路的区别在于分叉线到所有终点的延时是否相等。如果延时相等,则该分叉线是等时的。我们考虑图2.4中门A输出发生改变的情况:这个变化最终会反映到门B和C的输人,再经过一定的时间后门B和C根据新的输入产生新的输出。如果仅仅是门B对新的输入做了响应,不能确定门C的输人是否有改变。在这种情况下,假设 d 2 d_2 d2= d 3 d_3 d3(即等时叉)是必要的,这样就可以推测出:因为门B的输出改变,所以门C也看到了这个改变。

在两相位和四相位捆绑数据方法中,控制电路一般是速度无关电路(某些情况下是延迟不敏感的),而具有匹配延迟的数据通路是自定时的。根据四相位双轨编码方法设计的电路一般是准延迟不敏感的,在图2.12和图2.14中的连接到几个C单元输人端的分叉必须是等时的,而连接到几个或门输人端的分叉是延迟不敏感的。

C单元

同步电路定义了信号稳定和有效的时间点;在两次时钟事件(clock-tick)之间,信号可能会有冒险(hazard),也可能会有多次的跳变转换沿。而在异步电路中,信号跳变被当作“事件”(event),在任何时间点被并行触发。在状态发生改变或产生一系列新的输出前,系统都会等待一个特定的信号变化或信号变换序列的发生,也就是说时钟的缺失意味着信号的每一次转变都是有意义的。因此,必须避免竞争(race)和冒险(hazard)的存在,以免“毛刺”被系统认定为有效的“事件”引起误操作;同时,系统本身也要确保输出信号的跳变都是有意义的。

在异步电路的设计中,为避免“冒险”,每个信号跳变要能被其他信号跳变推断出来。例如,如果二输入“或”门的输出出现“1-0”的跳变,可以推断“或”门的两个输入都是“0”;但是,对于输出出现“0-1”的跳变,就不能推断“或”门的输人状态,这时“或”门的输入可能为(0,1)、(1,0)或(1,1)。所以,“或”门只能指示输入全“0”的状态;同理,“与”门只能指示输入全“1”的状态。

C单元是异步电路中很好地解决了冒险问题的电路,而且是异步电路设计中普遍应用的特殊单元,C单元是一个状态保持单元,就像异步置位-复位锁存器,通过C单元输出状态的变化,可以确认输人端的状态改变。当两个输入都是。时,输出被置为0;当两个输入都是1时,输出被置为1;其他输入情况下,输出不发生改变。这样,当观察者看到输出发生从。到1的改变时,就可以得出结论,两个输入都为1;类似地,如果看到输出发生从1到0的改变时,就可以判定,两个输入都是0。尽管,C单元的接口和普通的逻辑门类似,但是C单元不完全是组合逻辑,它包含一个类似寄存器功能的存储结点。

图2.5(a)所示为对称C单元的符号和真值表,从真值表中可见,对称C单元在相同的输入值时输出才发生变化,从输出端出现的“0→1“或“1→0”跳变,就能确定输入是全“1”或全“0”。

由于握手行为比较频繁,在异步电路中将反复出现0和1之间的转换,C单元显然是异步电路设计中经常使用的基本部件。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-siKgwgCm-1666168433724)(异步电路学习笔记20221017.assets/image-20221017213901511.png)]](https://img-blog.csdnimg.cn/bd6245ce448d4ac0bdcd56a7e56074d4.png)

Muller流水线

图2.6是用C单元和反相器建立起来的一个电路,这个电路的名字是Muller流水线(pipeline)或分配器(distributor),这个电路的变换和扩充可构成几乎所有异步电路的控制单元。如果剥去一些杂乱的细节,就会发现Muller流水线往往就是电路的关键所在。这个电路具有很好的对称性,一旦理解了它的特点,对大部分异步电路设计的理解就有了很好的基础。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Pq4aXShc-1666168433724)(异步电路学习笔记20221017.assets/image-20221017214113363.png)]](https://img-blog.csdnimg.cn/d67a1c7dc7c245aabe4d6d016961f478.png)

在图2.6中Muller流水线的机制实际上是传递握手,在所有的C单元被初始化为0之后,左边环境的部分就开始发起握手行为。我们首先考虑第i级C单元(记为C[i]),当且仅当后边的C[i+1]为0时,它才会从前面的C[i-1]传播进来(如输入或存储)一个1;同理,在它后面的C单元为1时,它将从前面的C单元传播(如输入或存储)一个0。如图2.6所示,如果把异步电路中的信号传播看作一系列的波形序列那么,在流水线中的c单元级就是用来保持波形序列的波峰和波谷在传播中的完整性。

观察者可以在C单元流水线级间的任何接口中看到正确的握手,但是其时序可能与左边环境的握手时序不同。一旦把一个波形输入到Muller流水线,这个波形将会以一定的速度传播,传播速度由电路的实际延时所决定。

最终,第一个从左边环境输人的握手请求信号将到达右边环境,如果右边环境不对这个握手做出响应,流水线将最终填满,这样的话,流水线将停止与左边环境的握手Muller流水线表现为一个FIFO行波。

除了上述的优点,Muller流水线还具有很多非常优美的对称性。首先,不管实际将采用两相位的握手还是四相位的握手,它们的电路都是相同的,不同点在于如何理解信号并应用电路。其次,电路从右到左操作时也是一样的。你可以颠倒信号的极性定义,颠倒请求和应答信号的角色,并从右至左地操作电路。这一点有些类似在半导体当中的电子和空穴,当电流向一个方向流动时,可以解释为电子向一个方向运动或空穴向相反的方向运动。

这个电路具有一个很有趣的特性是可以不考虑逻辑门和连线的延时也能正确运行,即Muller流水线是延迟不敏感的。

电路实现风格

上面介绍的协议都假设数据发送端会主动发起数据传输,称为推通道(pushchannel)。相反,如果是数据接收端主动要求通道上的数据传输,就称之为拉通道(pullchannel):在这种情况下,请求和应答信号方向转换为相反方向,并且由应答信号(从发送端到接收端)来表示数据信号的有效性。在简略表示连接(link)/通道(channel)的电路符号中,常用一个圆点表示通道中的主动方,如图2.7所示的捆绑数据通道。为了使通道概念更完整,我们还要考虑几个变形:①一个没有数据的通道可以用来进行握手(同步);②一个需要双向传递数据的通道可以分别用Req和Ack指示正向和反向数据的有效性。后者可实现为只读存储器的接口:地址信号可以与Req捆绑在一起,数据可以与Ack捆绑在一起。接下来的章节里,除非特殊说明,我们将主要讨论推通道的情况。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-7KcVxcfB-1666168433724)(异步电路学习笔记20221017.assets/image-20221017214932819.png)]](https://img-blog.csdnimg.cn/d788c0e23c914b9c92d6998ea07e47b7.png)

前面介绍了异步电路的分类,这些分类方法可以组合成多种可能的协议。异步电路设计根据需要采用不同的协议,从而具有不同的电路风格。

在双轨编码协议中表示每一位数据的两根线可以看做是相应数据的独热(one-hot)编码,这还可以扩展为n选l(1-of-n)编码和高基数(higher-radix)编码;如果着眼点在于通信而不是计算,n选m(m-of-n)编码也是可以的。异步电路可能存在的协议能够通过握手协议、数据编码方式和通道类型各种可能的选择进行笛卡尔积得到,即

{两相位,四相位} × {捆绑数据,双轨, n 选 1 , … } × {推,拉} {两相位,四相位}\times{捆绑数据,双轨,n选1,…}\times{推,拉} {两相位,四相位}×{捆绑数据,双轨,n选1,…}×{推,拉}

协议的选择将影响电路实现的特性,如面积、速度、功耗和鲁棒性等。

异步控制器电路

异步设计方法的核心是异步控制器电路,目前主流的异步控制器单元具有三类,即CElement、GASP和Click。CElement实现了基于“数据捆绑”的握手协议,而GASP和Click电路采用“约束捆绑数据”的握手协议,将通讯和数据管理分离为不同事件,这种事件分离的机制从原理上保证了电路的时序,可以显著简化异步设计方法。

CElement异步方法(即C单元)

众所周知,异步电路与同步电路主要区别在于是否存在时钟信号,但是在很多情况下要求信号是有效的,因此信号的每一次跳变都会对整个电路的功能产生影响,因此冒险和竞争会造成的严重问题。根据竞争冒险理论,主要是因为电路的信号变化没有传递到另一个信号上,或者说一个信号的变化被另外一个信号给屏蔽了,本章所介绍的CElement可以很好的解决这个问题。CElement由Muller于1955年提出(也称为Muller C),是目前应用最广的异步控制单元,实现了基于“数据捆绑”的握手协议,这种电路在握手通讯过程中,由于没有对数据进行任何约束,后期需要大量的时序验证工作才能保证电路的正确性。

CElement中的状态保持单元,类似于异步电路复位置位的锁存器,主要原理是通过事件“与”操作来实现,也被称为事件的逻辑。CElement的实现方式有很多,而在图1中所示为CElement逻辑实现为最直观的方式,其主要由4个与非门组合而成。从图中可知,CElement包含两个输入端(a和b)以及一个输出端(c),因此可以得到如下逻辑表达式:

C = ( a & b ) ∣ ( b & c ) ∣ ( a & c ) C=(a\&b)|(b\&c)|(a\&c) C=(a&b)∣(b&c)∣(a&c)

从逻辑表达式中可以看出,输出c为组合回路,即输出c即为输出端,又作为整个逻辑单元的输入端。对于这种情况出现时,将会在设计电路的编译过程中编译工具产生一些警告语句,对于设计中的警告语句也应该给予足够的重视,以免对整个电路设计造成不良的影响。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-8ZBWlJTX-1666168433724)(异步电路学习笔记20221017.assets/image-20221017215824134.png)]](https://img-blog.csdnimg.cn/633750f0a7bc45c48db65e2585435875.png)

通过图1的CElement模块和逻辑表达式(1)可以得到表1中真值表,仅当输入端A和B两者均为0时,其输出端C将变化为0;而当二者的值均为1时,输出端才为1;此外的情况下,其输出值将一直保持不变。

与同步电路不同,异步CElement控制没有一个统一的离散时间信号,电路模块之间的通信或者流水操作都是通过一系列的握手信号完成的。在图2为Muller流水电路的结构,其包括控制电路和功能电路模块,在控制电路中包含两路控制:请求信号Req和应答信号Ack,前者主要是启动一个操作,而后者表示操作的完成。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-MroiUa84-1666168433725)(异步电路学习笔记20221017.assets/image-20221017215917159.png)]](https://img-blog.csdnimg.cn/94a5e0fb4b614f8985fc44d920fb94ae.png)

从上图中可以看出,当第一个CElement接收到请求信号(Req),将产生一个输出信号,并触发存储器(Latch)工作,继而将数据(Data)往下一级传递。同时产生的信号还作为下级CElement的请求信号(Req),由此数据也将按照流水的方式进行逐步的传递。Muller C作为一种非常经典的异步控制器结构,在各种异步电路中广泛采用,在此基础上扩展和改进已成为异步电路的基石,本文采用的Click异步控制器其实现方式也与其类似。

GASP异步方法

GASP异步控制器通过单轨线和单轨数据编码实现握手通讯,这种结果使N+1条线来通信N个数据位。GASP电路在相同技术条件下的速度是全局时钟电路的两倍速度,具备良好的异步设计速度、低功耗和低面积方面的灵活性和弹性,并且还拥有良好的片上通信电路,这也是采用GASP作为网络通信的原因。

如图3为GASP电路的实现原理,其局部激活信号fire将控制数据进行传递,而GASP电路总共存在顺时针和逆时针两个运行方向。除了数据线方面,GASP电路的很大的特点是用单根先实现双流向的通信,即与上下两级的GASP模块完成控制信号的传递。一个单轨线存在两个驱动,分别在线的两端,一个用于请求,另一个用于应答,其中高电平代表一个请求信号(request),而低电平代表应答信号(acknowledge),这就很自然的导致两相的归零制(Return-to-Zero)握手。在图中的

S

i

n

S_{in}

Sin和

S

o

u

t

S_{out}

Sout这两根单轨线将分别请求和应答两级GASP模块,每一次工作都将产生相应的激励信号fire,由此进一步完成对功能模块的事务处理。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-ar6ZLWG3-1666168433725)(异步电路学习笔记20221017.assets/image-20221017220043264.png)]](https://img-blog.csdnimg.cn/5beb5c3b6af946ec909e39600e554694.png)

Click异步方法

Click异步控制器采用“约束捆绑数据”的握手协议,将控制通讯通路和事务处理分成不同的事件,这种机制在一定程度上保证了异步电路实现上的时序,具有非常好的层次化结构,为设计者提供良好的设计思路。Click异步控制器最早是由Peeters和Willem在2010年提出,是三种主流异步控制器中较新颖的异步设计方法,多个控制器之间通过Req(请求)和Ack(应答)进行握手通讯,并且用fire(激发)信号现实功能模块间的数据传输。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-1iGp4IAI-1666168433725)(异步电路学习笔记20221017.assets/image-20221017220206403.png)]](https://img-blog.csdnimg.cn/85c1d370b07840509868f590764adb99.png)

Click异步控制器的实现原理如图4中所示,其模块包含两对输入/输出端,其目的是配合上下两级的异步控制单元,其中左边的输入(in_R)和输出(in_A)用于和上级的Click模块进行通讯,右边的输入(out_A)和输出(out_R)连接与下级Click模块。当上级请求信号in_R升高之后,信号通过异或门之后将变高,此时右边的同或门的输出默认值为高电平,二者共同通过中间的与门,因此其结果输出高电平。与门的输出一方面将作为电路的局部触发信号fire,另一方面将激活D触发器工作,其输出值分别作用于应答上级的控制器(in_A)、下级控制器的请求信号(out_R)以及右侧同或门的输入端。完成上述工作机制之后,上下两级的Click模块将会重置此模块的in_A和out_R两个信号,并同时取消局部激活信号fire。在局部信号fire的激活和取消的时间区间内,功能模块将进行事务的处理。其中,在图5中所示的为Click控制器的握手协议原理图,其中很清晰的展示局部激活信号fire的产生条件。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-K6rWVOmh-1666168433725)(异步电路学习笔记20221017.assets/image-20221017220234646.png)]](https://img-blog.csdnimg.cn/a43e4d38521a47c785e7c2fcc4eb8d1b.png)

Click异步控制器是本论文主要采用的异步电路控制方式,其结构简单、模块间的通讯机制清晰以及具有良好的稳定性等优点。在实现多种乘法器的设计结构中,其中将采用多个Click的微流水线控制单元,以此来保证电路处理结果的正确性。

ac8051项目分析

项目整体介绍

ac8051为兰州大学何安平团队开源的一个全异步8051MCU软核,它是基于Synopsys公司开发的同步DW8051——一个由状态机堆叠机制实现的两级流水线MCU,在不改变它的MCU核内电路逻辑结构的基础上转化而来,其架构图如下图所示

项目内各个文件夹内容情况说明:

fpga------FPGA版本的异步MCU。

|---bitstream:可以直接使用的比特流文件,用Vivado直接加载即可。

|---coe:MCU的执行程序,将该文件加载在Icache对应的bram IP内即可直接使用.

|---doc:模块说明和一些注意事项。

|---rtl:MCU的电路代码。

|---xdc:MCU的约束文件。

keil5-----生成coe所用的keil工程

tb--------MCU仿真用的测试文件

在README文件中,还通过视频及配图教程手把手演示工程运行的全过程。教程中还展示了在Vivado中对工程进行功耗分析的过程。

模块详细情况介绍

自复位电路

click异步控制器在fpga版本里没有复位键(rst_n),但click需要有复位功能。因此在设计异步电路时,click需要有一个不被全局复位信号影响的自复位电路模块。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-T4IkmZsq-1666168433726)(异步电路学习笔记20221017.assets/image-20221018111619695.png)]](https://img-blog.csdnimg.cn/7035287091114d1789ac66c4125b3e55.png)

在全局系统复位后,计数到第40个时钟周期时使in_R由高到低,产生复位效果。这个in_R不仅可以作为click链的复位信号,还可以作为click链的启动信号。在click_control.v中,将它取反即可启动整个click链。

约束方式

步骤

- 在所有例化的电路模块前加(keep_hierarchy=“yes”),保证电路在综合和布局布线时所有的模块信号名称保持不变

- 对除了always语句中posedge和negedge引用的信号如fire、rst_n等以外的所有信号加上(dont_touch=“true”),保证电路在综合和布局布线时所有的模块信号不会被优化掉

- 可适当删除部分不会被布局布线阶段优化掉的信号约束,以降低电路总功耗

加约束的目的

现如今的EDA设计工具都是针对同步电路设计的,它难以理解异步电路到底在做什么样的事情。所以说如果不加约束的话,在布局布线的时候click链很多信号会被莫名其妙的优化掉,甚至根本找不到它对应的名称,若电路出现了问题,难以排查。

复位滤波模块

目的

异步电路设计中一直存在一个问题,就是相位匹配问题。如图(b),若click单元没收到第三次应答(3rd ack),则即使第四次请求到来(4th req)也不会产生fire信号。

在本次设计的MCU中,启动in_R(click_control中的process_req_out信号)会受全局复位影响。若在复位时它是高电平,且它前面的请求和应答工作均完成,则它在复位后从高点平变为低电平会导致产生一次fire。在这一次fire后,in_A,out_R,out_A会陆续变为0,完成复位。但是若全局复位信号在额外的fire还没使out_R、in_A和out_A完成复位就结束了,那么这一次的相位状态会保存在click链中,导致下次启动错误。为了解决这个问题,就必须要进行复位滤波。

复位滤波的目的:

(1)滤除复位按键产生的毛刺信号,使只有一个稳定的复位信号进入MCU

(2)使复位信号保持一定的时间,不能短于click链自复位的时间。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-RnDDj8kH-1666168433726)(异步电路学习笔记20221017.assets/image-20221018112610869.png)]](https://img-blog.csdnimg.cn/3bcd5048005b47059b62a6e4d936a4f8.png)

设计方法

- 在rst_n从低电平变为稳定的高电平后开始计数一段时间,等计数结束后产生第一级复位信号rst_n1

- 在rst_n1从低电平变为稳定的高电平后开始计数一段时间,等计数结束后产生第二级复位信号rst_n2

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Am9RF43M-1666168433726)(异步电路学习笔记20221017.assets/image-20221018113121289.png)]](https://img-blog.csdnimg.cn/db48b15935594401bf7fd88f880711c4.png)

异步驱动逻辑部分

异步驱动逻辑(Asynchronous Driving Logic, ADL)包含两部分,一部分是取指和译码异步驱动逻辑(IF&ID ADL),一部分是执行异步驱动逻辑(EX ADL)。

IF&ID ADL

一般流水线的第一级的异步驱动逻辑设计都分为三部分:启动部分(Event Start Part),执行部分(Event Driving Part)和结束部分(Event End Part)。

-

启动部分(Event Start Part):主要负责三个功能:

(1)处理MCU启动请求

(2)处理MCU运行请求

(3)处理外设响应请求 MCU启动请求对应的是它复位后由计数器产生的第一个请求,该请求到来后MCU开始工作。它对应的是图中的Start_req信号(click_control.v中的fire_start信号),它只会产生一次,因为后续该驱动逻辑工作接受的请求必须是EXADL返回的请求信号,不可能用无限复位的方式驱动MCU保持工作。也就是说,in_R第一次翻转是由Start_req决定的,之后所有翻转都是由EX_ack(click_control.v中的process_req_end信号)决定的,这也是它处理MCU运行请求的过程。

外设响应请求对应的信号为I/O_ack1(click_control.v中的fire_rx_end信号)和Icache_ack(click_control.v中的out_R_icache信号),这两个请求保证了MCU和外设正确的跨时钟域交互。在MCU启动后,当I/O_ack1未到来时,MCU会停在fire_c2对应的阶段,直到它到来后才使MCU继续工作;Icache_ack未到来时,MCU会停在fire_c3对应的阶段,直到它到来后才使MCU进入到fire_c4阶段。由于MCU在外设工作时会绝对静止(没有fire信号驱动内部电路模块),直到外设结束工作后MCU才收到请求信号继续工作,因此我们的方法在解决跨时钟域问题时不需要异步FIFO的机制。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-x9rfwRco-1666168433727)(异步电路学习笔记20221017.assets/image-20221018144304191.png)]](https://img-blog.csdnimg.cn/4743a010987248eb8528574f983eebc3.png)

-

执行部分(Event Driving Part):主要负责产生fire信号来驱动MCU工作,由于DW8051是一个四阶段状态机MCU,因此需要四个fire信号来驱动BIU和它对应的状态机计数器工作。

-

结束部分(Event End Part):主要负责向下一级和Dcache发送启动请求

EX ADL

一般流水线的第二级及往后的异步驱动逻辑设计都分为两部分:执行部分(Event Driving Part)和结束部分(Event End Part)。

- 执行部分(Event Driving Part):主要负责产生fire信号来驱动MCU工作,由于DW8051是一个四阶段状态机MCU,因此需要四个fire信号来驱动Control等第二级流水电路模块和第二级流水状态计数器工作。

- 结束部分(Event End Part):主要负责向IF&ID ADL发送继续工作请求。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-cOayi6Md-1666168433728)(异步电路学习笔记20221017.assets/image-20221018145012482.png)]](https://img-blog.csdnimg.cn/308eff3ee75d4ee79bdf9c322a0744f1.png)

异步存储器设计

图(a)为异步Icache的结构图,图(b)为异步Dcache的结构图。由DW8051的工作原理可知,Icache仅工作在MCU的第三个状态机,Dcache工作在MCU的第1、2、4个状态机。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-PByf4fks-1666168433728)(异步电路学习笔记20221017.assets/image-20221018145118209.png)]](https://img-blog.csdnimg.cn/ce4cfcfc8eb64772b14e26a183b5964b.png)

异步外设设计

下图为异步UART的结构图,(a)为RX模块的结构图,(b)为TX模块的结构图。设计思路也非常简单,当RX和TX模块接收到MCU发送的查询请求I/O_req1(uart_unit.v中的fire_rx信号)和I/O_req2(uart_unit.v中的fire_uart信号)时,若它们此时不需要工作,直接向MCU返回应答信号I/O_ack1(uart_unit.v中的fire_rx_end信号)和I/O_ack2(uart_unit.v中的fire_tx_end信号);若它们此时需要工作,则等到Receive Part和Transmit Part工作结束后再发送应答信号I/O_ack1和I/O_ack2。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-br3ObTYp-1666168433728)(异步电路学习笔记20221017.assets/image-20221018145231865.png)]](https://img-blog.csdnimg.cn/1c018bbaf48741eb8e7352194d601b97.png)

7156

7156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?