同步电路在一个理想的电路时钟的控制下,只要电路的各个功能环节都市现了时序收敛,整个电路就可以可靠工作。

但在一个功能复杂的SoC系统中,难免会有异步信号与同步信号交互的问题。

因此。在多核SoC系统中,通常采用 全局异步局部同步(GALS) 的设计。

同步电路设计

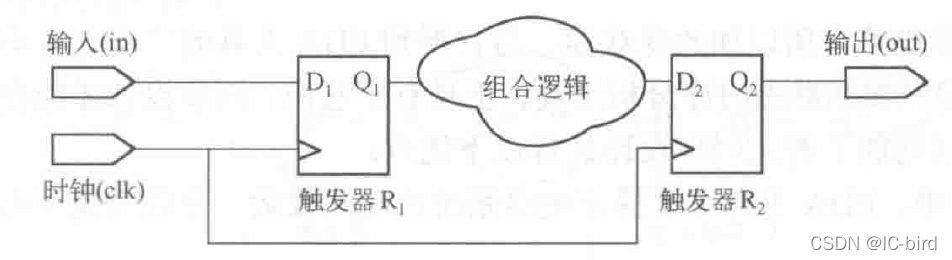

同步电路即 电路中所有受时钟控制的单元全部由一个统一的全局时钟进行控制。

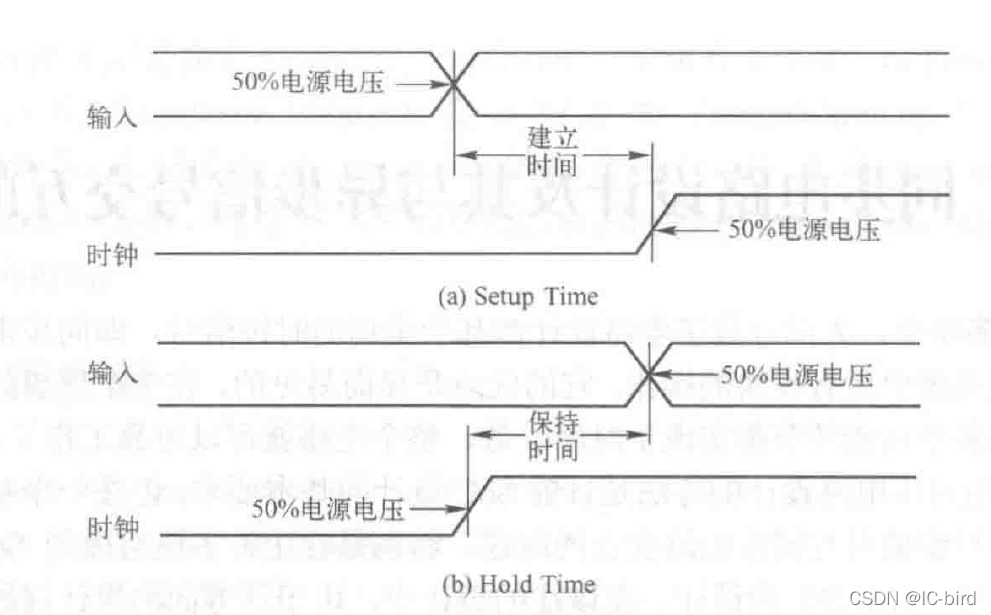

触发器的时期收敛保证了触发器输入端的数据在时钟信号有效沿来临之前就达到稳定状态,即满足了触发器的建立时间(Setup Time)

同时也保证了触发器输入端数据在时钟有效沿过后的一段时间内保持稳定,即满足了触发器的保持时间(Hold Time)

同步电路的最大工作速度由最常的组合逻辑路径延时决定。

优点:

EDA工具可以保证电路系统的时序收敛,有限避免了电路竞争冒险现象

触发器只在时钟边沿才改变取值,很大限度的减少了整个电路受毛刺和噪声影响的可能

缺陷

主要问题时时钟偏斜和功耗

时钟到达时间在空间上的差别成为时钟偏斜(Clock Skew),解决办法是采用EDA工具进行时钟树综合(根据最长时钟路径来平衡其他时钟路径,需要加入大量延迟单元,使得面积和功耗大大增加)

除了时钟偏斜(Skew),同步电路还受到时钟抖动(Jitter)的影响。时钟抖动是指,芯片某一给定点上时钟信号的间歇性变化,即时钟周期在不同时间段长度不一。

异步电路设计最大的不同是电路中的数据传输可以在任何时候发生,电路中没有一个全局的或者局部的控制时钟

无法避免竞争冒险现象、减少噪声影响

优点:

模块化特性突出:采用握手信号进行模块间通信,互联后不会受各个模块内部延时的影响

对信号延时不敏感:握手信号通信,电路的延时只会影响工作速度,不影响电路行为

没有时钟偏斜问题:取代整体时钟,避免时钟设计问题

潜在的高性能特性:不需要考虑最坏情况

好的电磁兼容性:不会在特定时刻瞬间大电流,电路工作没有锁定在一个固有频率上,大范围均匀分布

具有低功耗特性:数据驱动,尽在需要处理数据时才会消耗能量,具有低功耗潜力。

本文探讨了同步电路如何通过全局时钟实现时序收敛,以及其优点如稳定性、功耗控制。同时,对比异步电路的模块化、低功耗特性,并指出在SoC系统中采用GALS设计的原因。讨论了同步电路的缺陷,如时钟偏斜和抖动,以及异步电路的解决方案。

本文探讨了同步电路如何通过全局时钟实现时序收敛,以及其优点如稳定性、功耗控制。同时,对比异步电路的模块化、低功耗特性,并指出在SoC系统中采用GALS设计的原因。讨论了同步电路的缺陷,如时钟偏斜和抖动,以及异步电路的解决方案。

1694

1694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?