大家好大家好这里是X,来了来了更新了更新了

总线带宽概念💧

先走一波概念,总线带宽可理解成总线的数据传输速率,即单位时间内总线上传输数据的位数,通常用每秒传输信息的字节数来衡量,单位可用MBps(兆每字节)来表示

剖析计算需要的条件⚡

可以看到----需要时间----总线宽度

这个东西通过单位就可以剖析出来,这也是一种基本能力

总线的带宽指的是这条总线在单位时间内可以传输的数据总量,它等于总线位宽与工作频率的乘积。

总线带宽的两种计算方法

第一种:带宽 = 时钟频率 × 数据位数

第二种:带宽 = 数据位数 / 总线传输周期,总线传输周期 = n×时钟周期,时钟周期 = 1 / 时钟频率

其中n是题目中规定的总线传输周期对应的时钟周期的个数,这种方法也适用于计算数据传输率

对于64位、800MHz的前端总线,它的数据传输率就等于64bit×800MHz÷8(Byte)=6.4GB/s;32位、33MHz PCI总线的数据传输率就是32bit×33MHz÷8=132MB/s

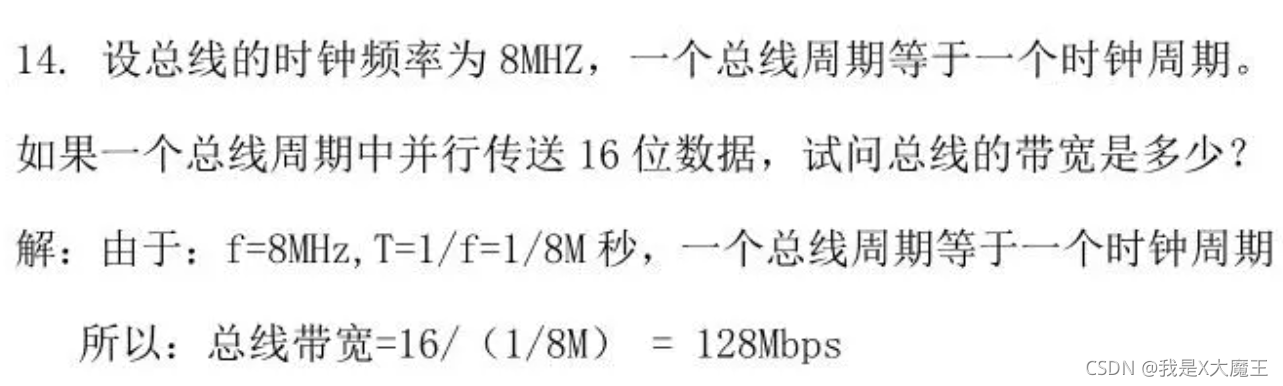

例题

一个字节Byet = 8bit,所以1Bps = 8bps,1MBps = 8Mbps

🧀以下的“/”代表➗

总线频率为33MHz,总线宽度为32位(4B),求总线带宽?

33 x (32/8) = 132MBps

在一个32位的总线系统中,总线的时钟频率为66MHZ,假设总线最短传输周期为4个时钟周期,试计算总线的最大数据传输率。若想提高数据传输率,可采取什么措施?

标准答案:

1)由总线传输周期 4/66 M秒,得总线的最大数据传输率为 32 / ( 4/66 )= 528 Mbps

2)若想提高数据传输率,可以提高总线时钟频率、增大总线的宽度或减少总线传输周期的时钟个数

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?