UART IP

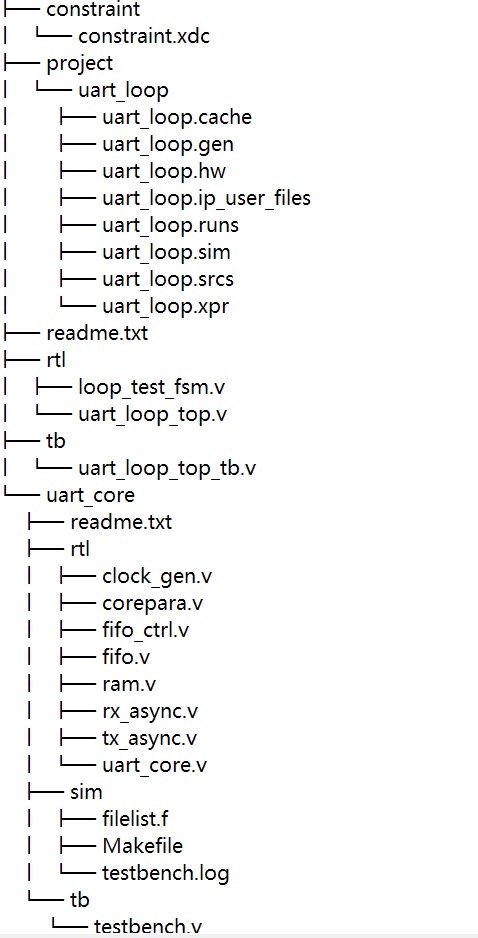

项目使用的代码;

使用verilog;

IP使用VCS进行仿真;

可移植到任何FPGA上使用;

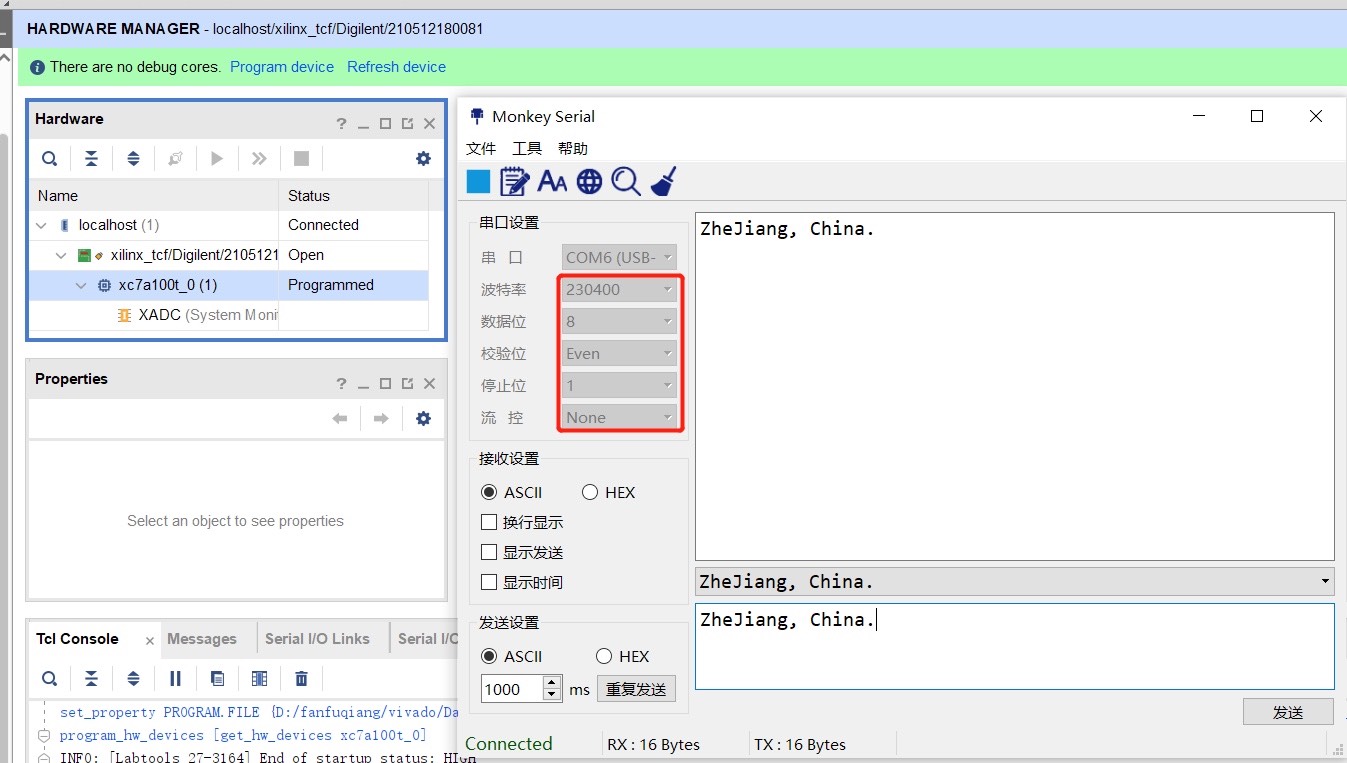

上板测试工程为回环测试,接收上位机发送数据再发回给上位机,也包含仿真文件,使用vivado

ID:64699688090032369

咸鱼_RTL猿

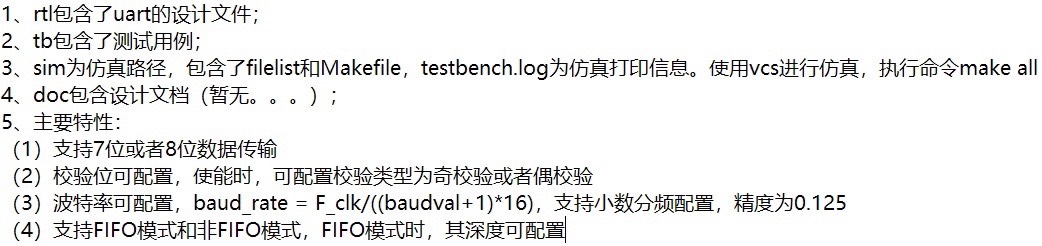

UART(通用异步接收传输)是一种广泛应用于串行通信领域的通信协议,它在现代计算机和嵌入式系统中占据重要地位。在本文中,我们将讨论关于UART IP的一些关键方面,包括使用Verilog编写的项目代码、使用VCS进行仿真以及如何将此IP移植到任何FPGA上使用。

首先,让我们从项目使用的代码开始。UART IP是使用Verilog语言编写的,这是一种硬件描述语言,广泛应用于数字电路设计。Verilog具有丰富的语法和语义,使得设计师可以方便地实现各种功能和逻辑。在编写UART IP代码时,设计师需要考虑时钟信号、数据传输格式、错误检测等因素,以实现可靠的数据通信。

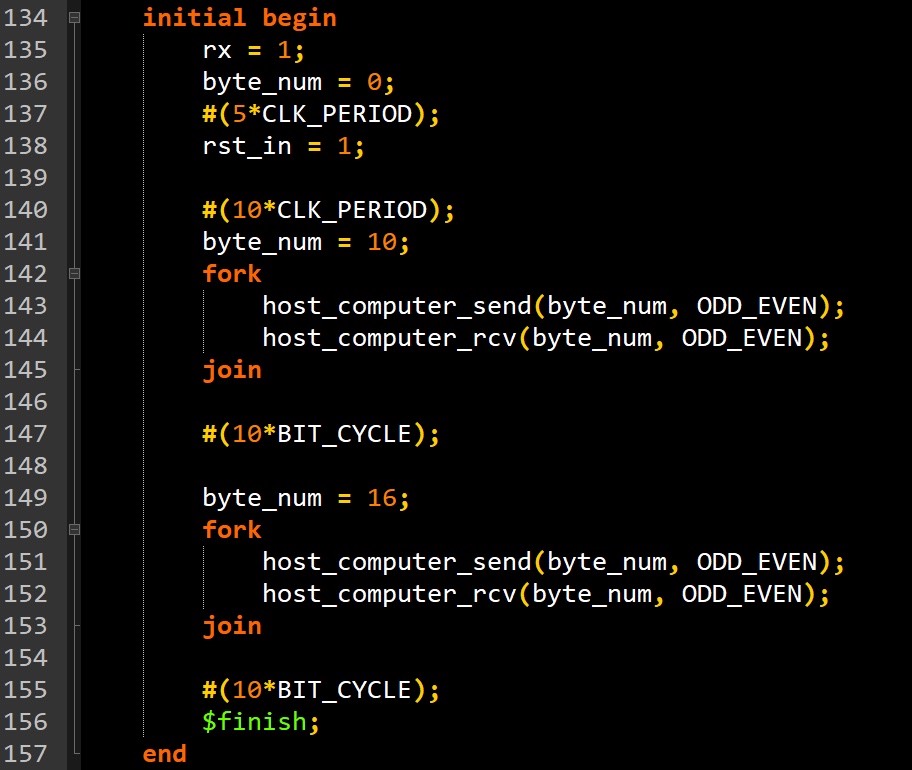

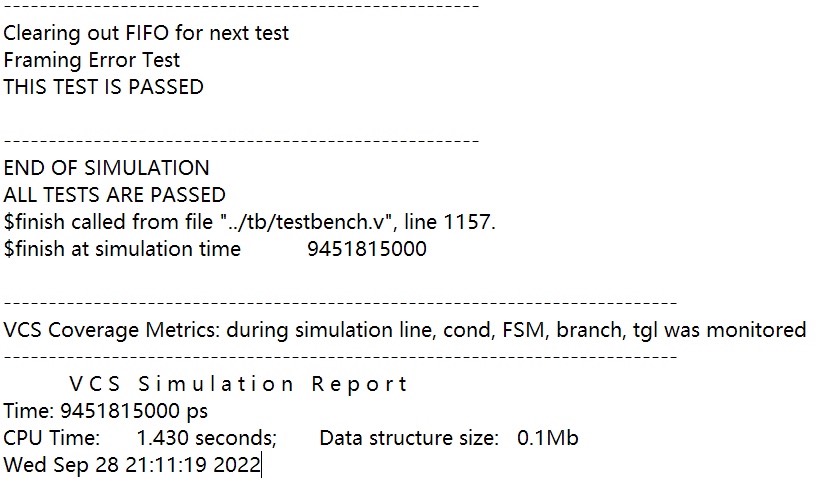

接下来,我们将讨论如何使用VCS进行仿真。VCS是一款流行的硬件验证工具,可以用于验证Verilog代码的正确性和性能。通过对UART IP进行仿真,我们可以模拟不同的数据传输场景,包括正常情况下的数据传输和异常情况下的错误处理。通过仿真,我们可以确保UART IP在各种情况下都能正常工作,并能够快速识别和修复潜在的问题。

除了在仿真环境中验证UART IP的功能,我们还需要将其移植到实际的FPGA平台上进行测试和应用。UART IP的可移植性是一个关键因素,它能够在不同的FPGA芯片上灵活使用。不同的FPGA芯片可能具有不同的架构、资源和特性,因此在移植UART IP时,设计师需要考虑适配不同平台的问题,并做出相应的调整。

针对UART IP的上板测试工程,我们采用了回环测试的方法。具体而言,我们将接收到的数据再发回给上位机,以验证UART IP的数据传输功能。为了实现这一测试,我们使用了Vivado工具套件。Vivado是一款功能强大的综合工具,能够帮助设计师完成从RTL设计到最终实现的整个开发流程。通过上板测试工程,我们可以验证UART IP在实际硬件环境中的性能,并进行必要的调试和优化。

总结起来,UART IP是一种在串行通信领域广泛应用的通信协议。在本文中,我们介绍了UART IP项目使用的Verilog代码、使用VCS进行仿真和将其移植到任何FPGA上使用的方法。通过对UART IP的测试和验证,我们可以确保其在不同平台和不同数据传输场景下的可靠性和性能。通过上板测试工程,我们可以验证UART IP的实际性能,并进行必要的调试和优化。希望本文对读者在UART IP的开发和应用方面有所启发,并提供有价值的参考。

相关的代码,程序地址如下:http://fansik.cn/688090032369.html

461

461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?