目录

半导体器件的开关特性

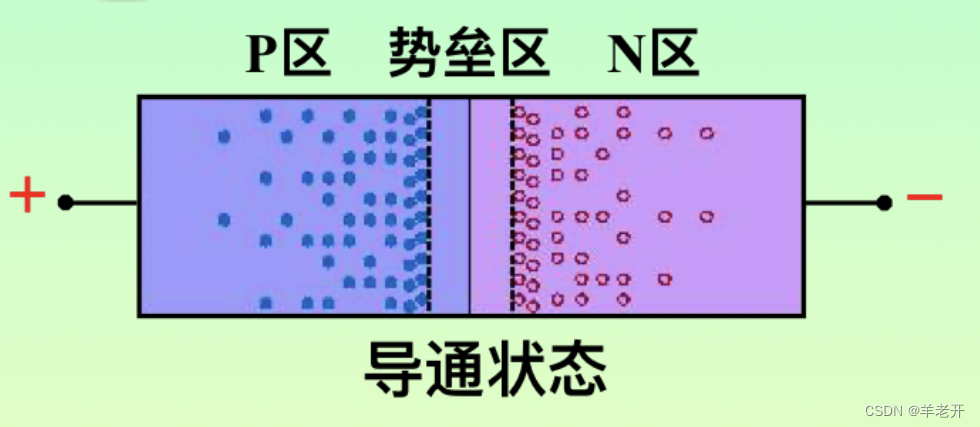

二极管开关特性(PN结)

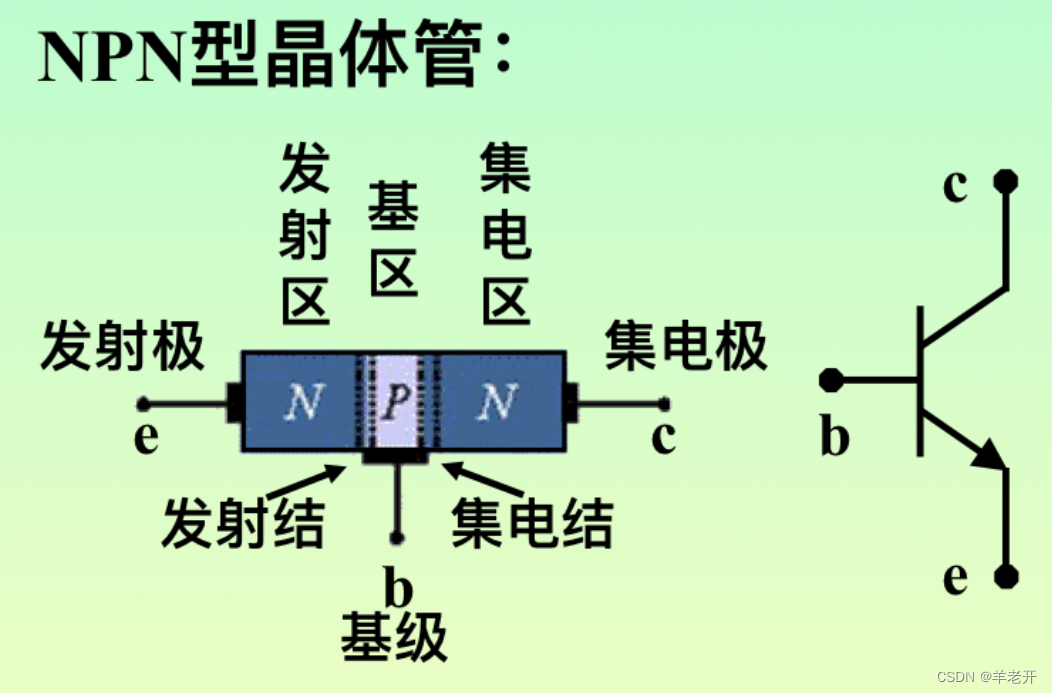

三极管开关特性(NPN型晶体管)

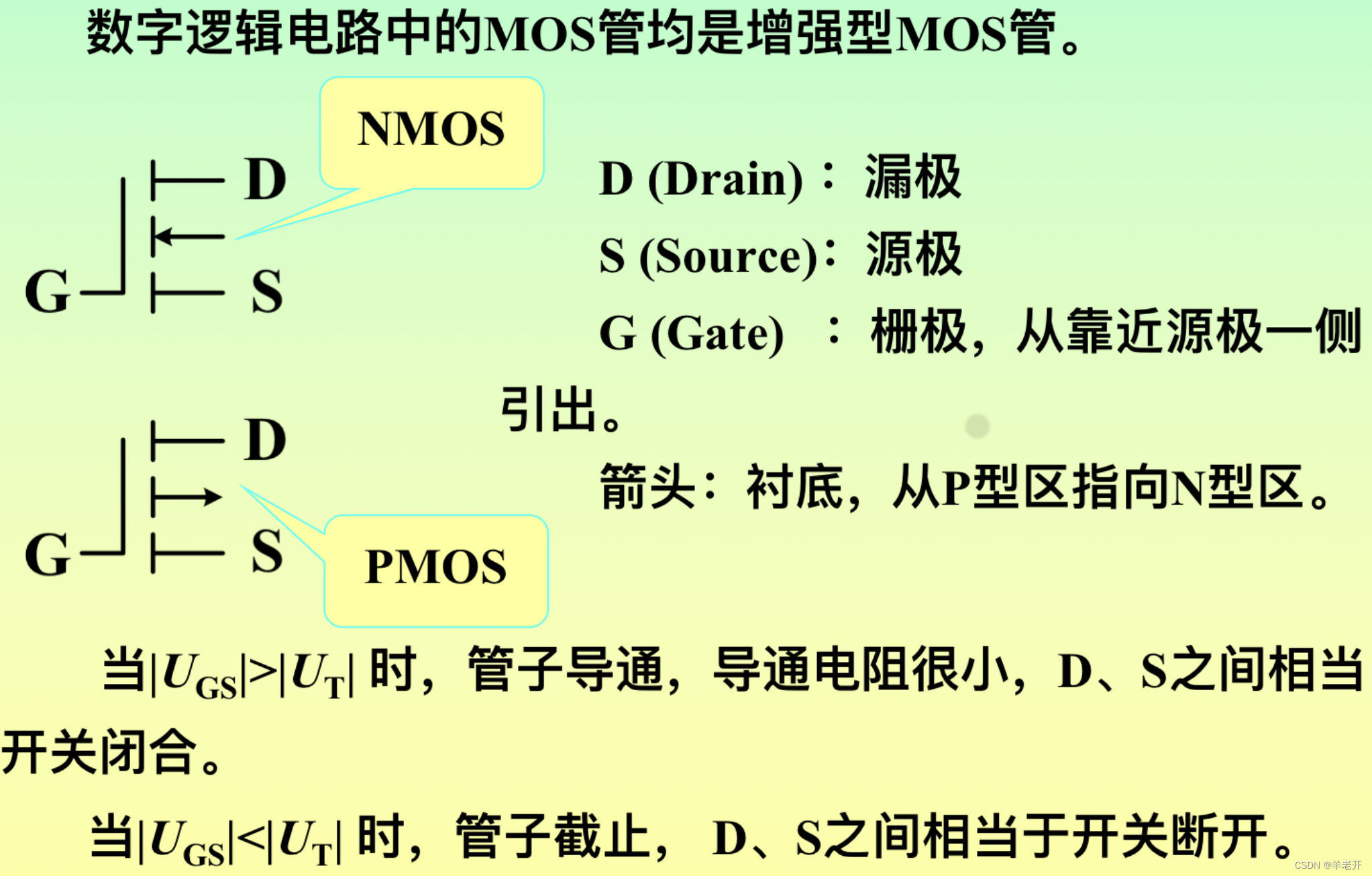

MOS管开关特性

TTL与非门

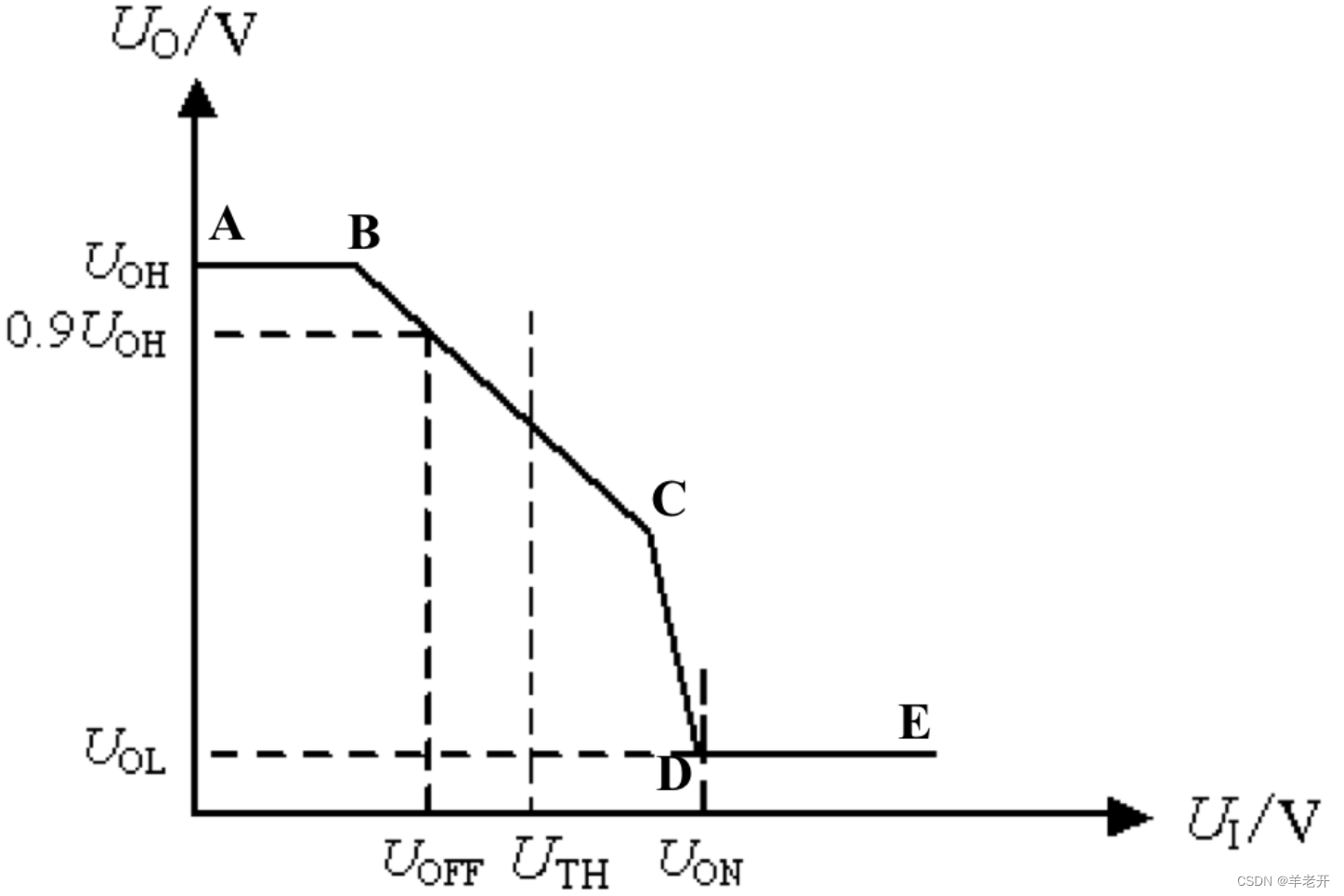

电压传输特性

输出低电平、 输出高电平

阀值电压:不知道干嘛

开门电平:让门低电平的最小输入

关门电平:让门高电平的最大输入

输入特性

输入短路电流

:低电平输入电流,灌电流负载

输入漏电流

:高电平输入电流,拉电流负载

扇入扇出系数

扇入系数:合格输入端个数

扇出系数:与非门输出端连接同类门的最多个数,反应与非门带负载的能力

TTL与非门多余输入端处理方法:

- 接 + 5V

- 悬空,则相当于高电平,易受干扰

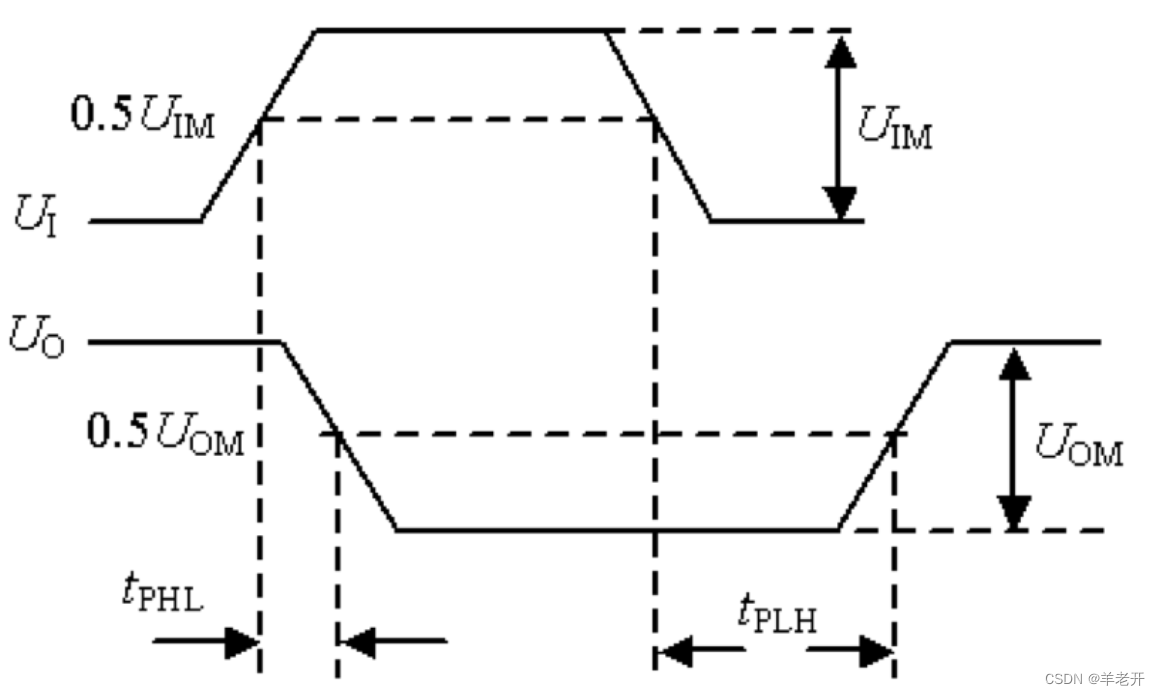

平均传输延迟时间

: 输出从H到L,导通延迟时间,取斜线中点的时间差

: 输出从L到H,截至延迟时间,取斜线中点的时间差

: 平均时间

功耗

静态功耗:空载导通功耗、空载截止功耗

动态功耗:电路发生转化时的功耗

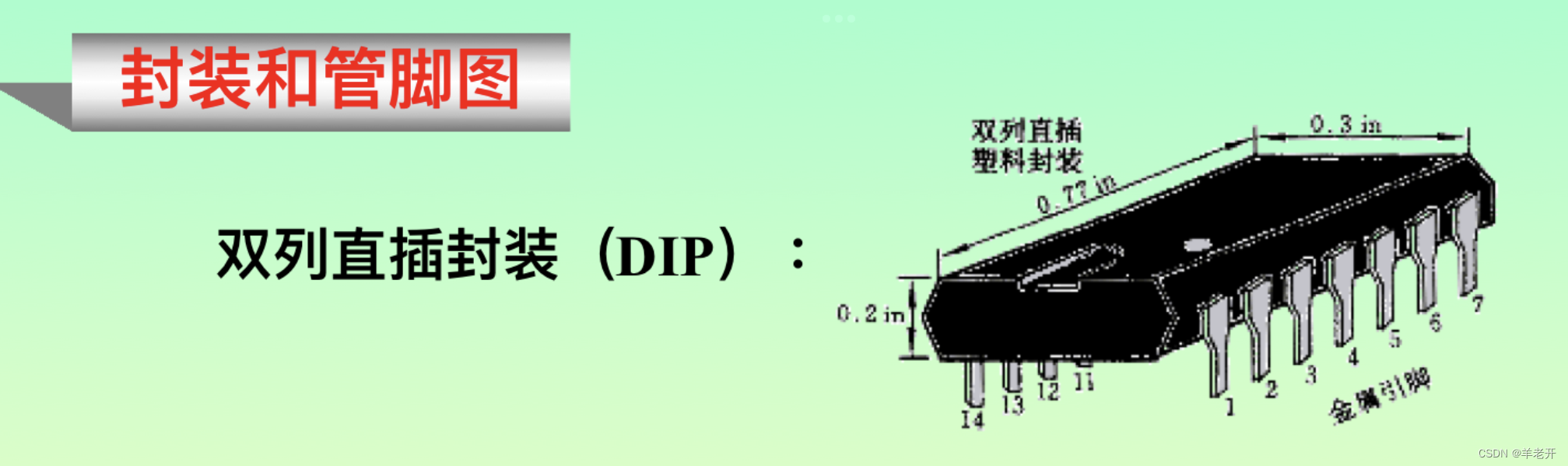

封装管脚

使用时,豁口朝左

其他TTL门电路

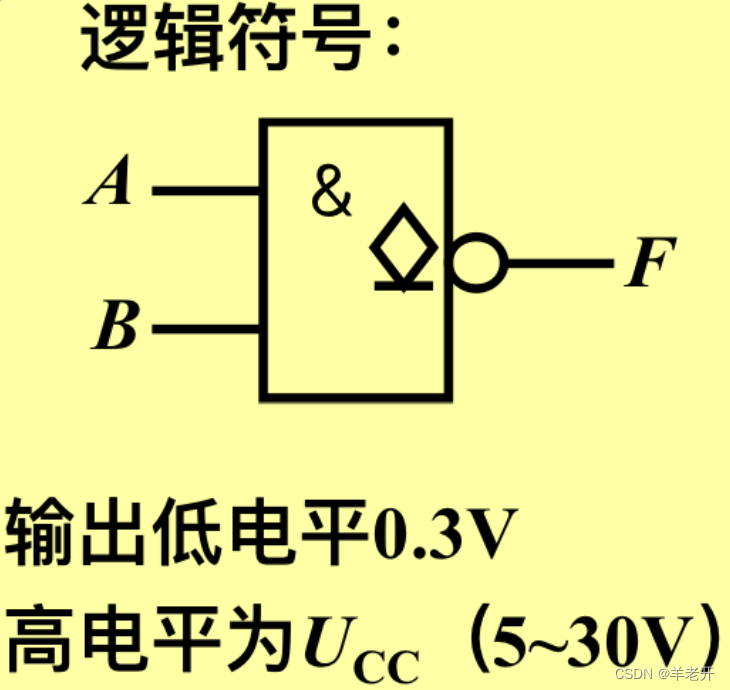

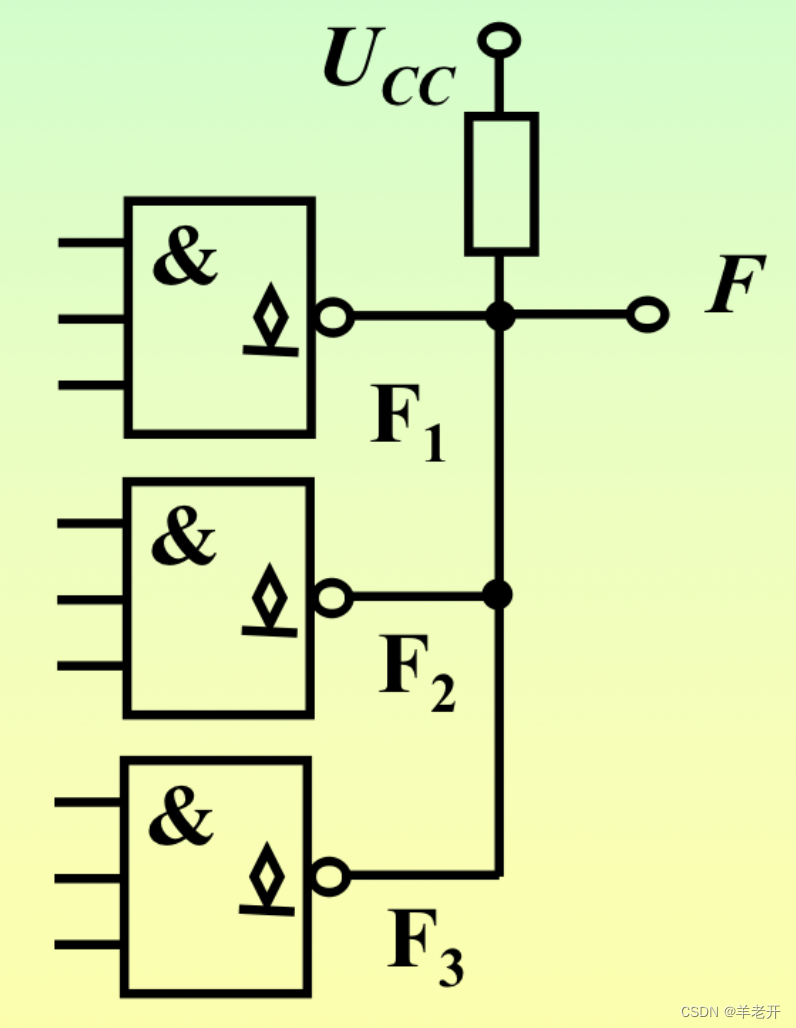

集电极开路门(OC门)

OC门实现“线与”逻辑

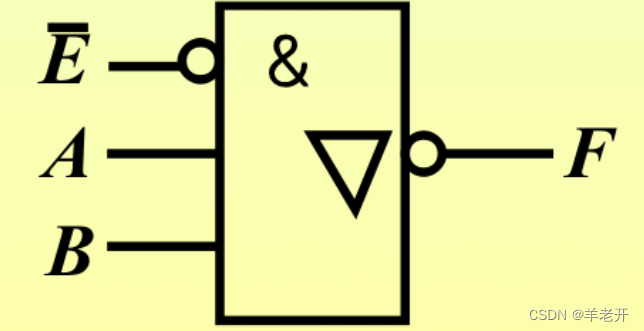

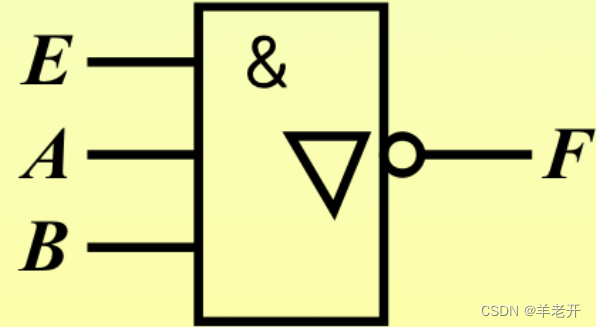

三态输出逻辑门(TSL门)

低电平使能

高电平使能

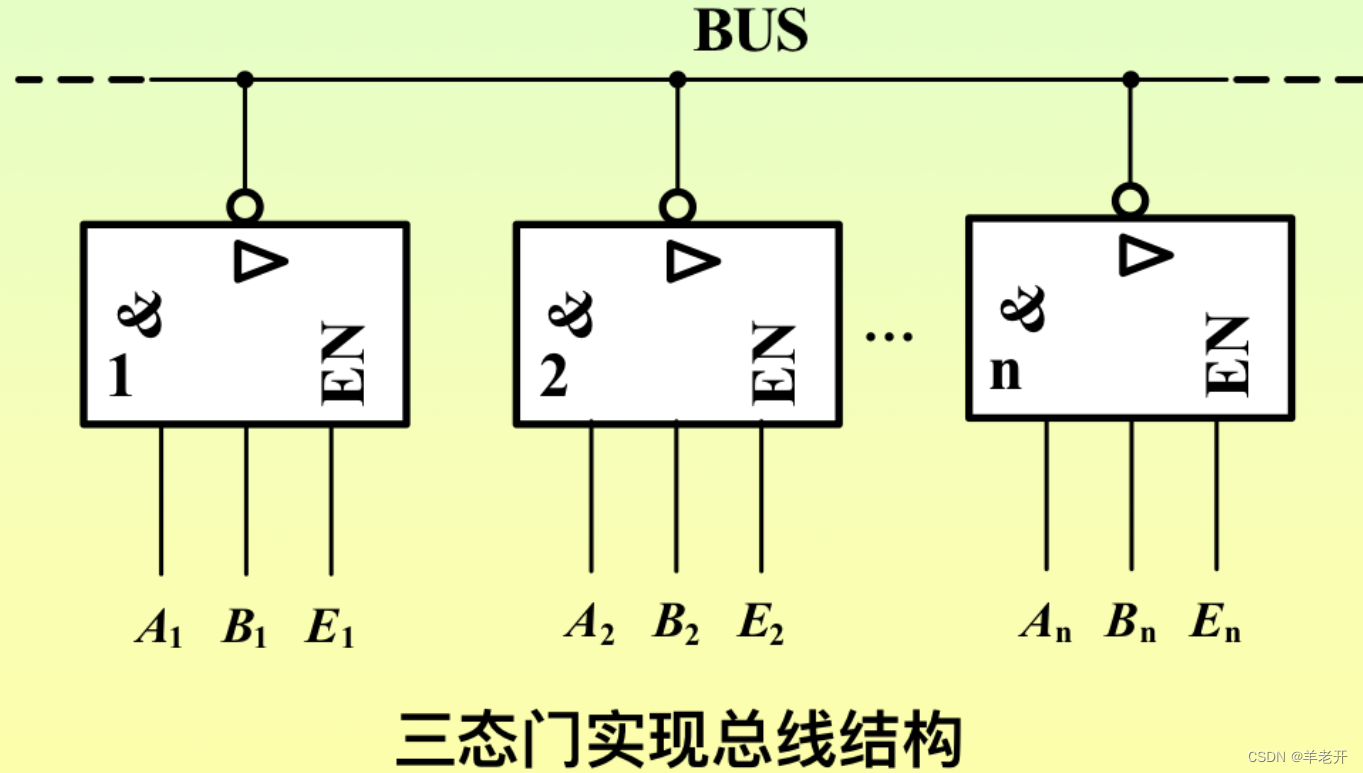

三态门实现总线结构

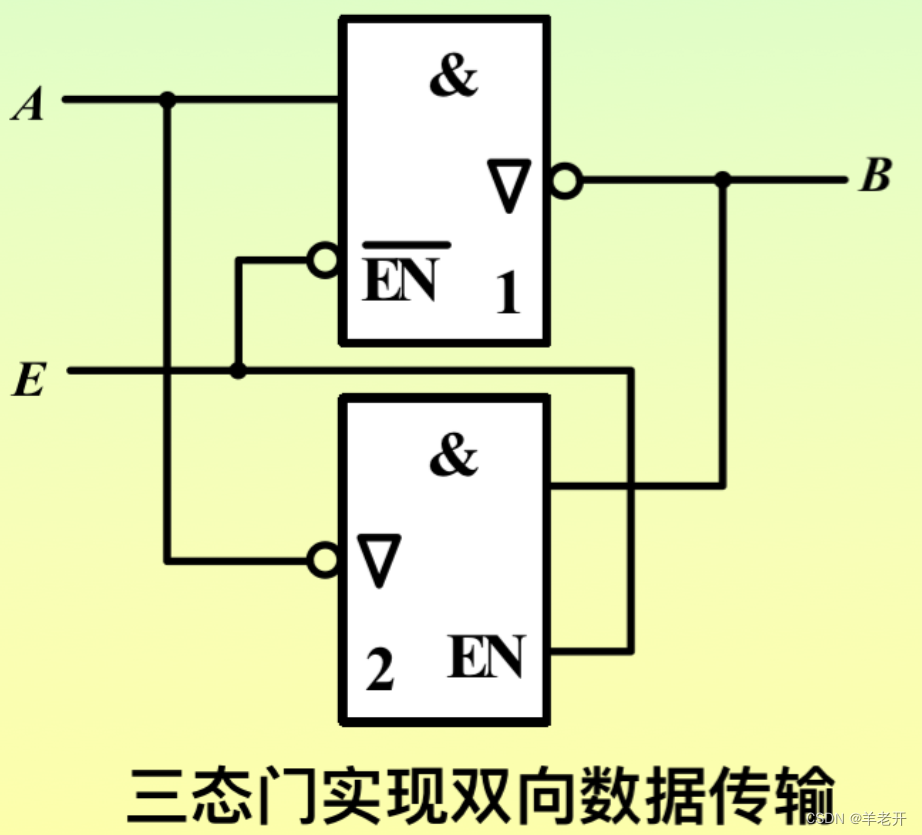

三态门实现双向数据传输

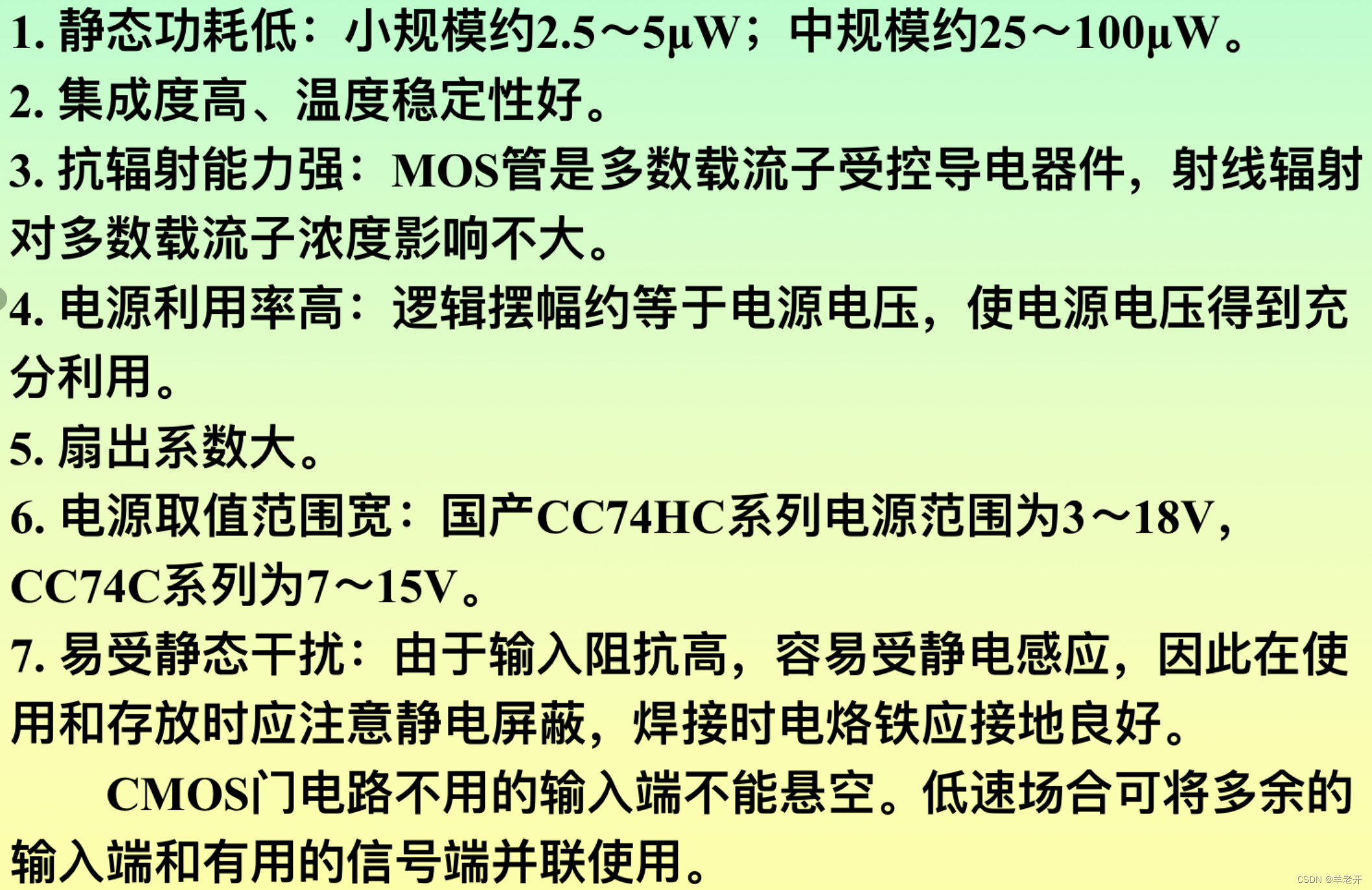

CMOS电路特点

图片来源:厦门大学计算机科学与技术系 程明

本文仅供个人学习、他人参考之用

1809

1809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?