目录

前言

Verilog中运算符

3.运算符

运算符可分为以下几类:

(1) 算术运算符(+,-,*,/,%)

(2) 赋值运算符(=,<=)

(3) 关系运算符(>,<,>=,<=,==,!=)

(4) 逻辑运算符(&&,||,!)

(5) 条件运算符(?:)

(6) 位运算符(~,|,^,&,^~))

(7) 移位运算符(<<,>>)

(8) 拼接运算符({ })

3.1 算术运算符

“+”(加法运算符),”-“(减法运算符),”*”(乘法运算符),”/”(除法运算符,如 7/3 =2),

“%”(取模运算符,也即求余数,如 7%3=1,余数为 1)

3.2 赋值运算符

“=”阻塞赋值,”<=”非阻塞赋值。阻塞赋值为执行完一条赋值语句,再执行下一条,可理解为

顺序执行,而且赋值是立即执行;非阻塞赋值可理解为并行执行,不考虑顺序,在 always 块语句

执行完成后,才进行赋值。如下面的阻塞赋值:

//阻塞赋值

module top(

input din,

input clk,

output reg a,b,c

);

always@(posedge clk)

begin

a = din;

b = a;

c = b;

end

endmodule

//非阻塞赋值

module top(

input din,

input clk,

output reg a,b,c

);

always@(posedge clk)

begin

a <= din;

b <= a;

c <= b;

end

endmodule `timescale 1 ns/1 ns

module top_tb() ;

reg din ;

reg clk ;

wire a,b,c ;

initial

begin

din = 0 ;

clk = 0 ;

forever

begin

#({$random}%100)

din = ~din ;

end

end

always #10 clk = ~clk ;

top t0

(.din(din),

.a(a),

.b(b),

.c(c),

.clk(clk)

) ;

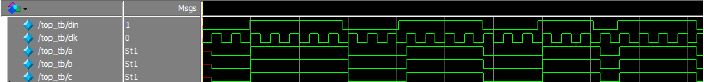

endmodule可以从仿真结果看到,在 clk 的上升沿,a 的值等于 din,并立即赋给 b,b 的值赋给 c。

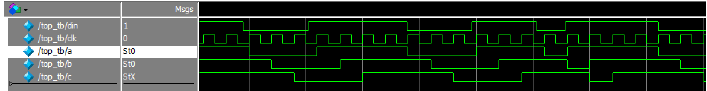

如果改为非阻塞赋值,仿真结果如下,在 clk 上升沿,a 的值没有立即赋值给 b,b 为 a 原来

的值,同样,c 为 b 原来的值

阻塞赋值与非阻塞赋值的RTL图分别如下所示:

深入理解下阻塞赋值与非阻塞赋值:微观上,在时序中“=”是引发“即时事件”,“<=”则是引发“时间点事很多的设计都不包含结构和使用方法,只要设计可以发挥预期般的效果就可以 ,掌握这个简单的道理,自然会明白。自定义 Verilog HDL 语言的结构和使用方法是非常的重要和基础“=”阻塞赋值,”<=”非阻塞赋值。阻塞赋值为执行完一条赋值语句,再执行下一条,可理解为顺序执行,而且赋值是立即执行;非阻塞赋值可理解为并行执行,不考虑顺序,在 always 块语句执行完成后,才进行赋值。一般情况下,在时序逻辑电路中使用非阻塞赋值,可避免仿真时出现竞争冒险现象;在组合逻辑中使用阻塞赋值,执行赋值语句后立即改变;在 assign 语句中必须用阻塞赋值。3.3 关系运算符

用于表示两个操作数之间的关系,如 a>b,a<b,多用于判断条件,例如:

if (a>=b)

q <= 1’b1 ;

else

q <= 1’b0 ;表示如果 a 的值大于等于 b 的值,则 q 的值为 1,否则 q 的值为 0

3.4 逻辑运算符

“&&”(两个操作数逻辑与),”||”(两个操作数逻辑或),”!”(单个操作数逻辑非)例如:

If (a>b && c <d) 表示条件为 a>b 并且 c<d; if (!a)表示条件为 a 的值不为 1,也就是 0。

3.5 条件运算符

“?:”为条件判断,类似于 if else,例如 assign a = (i>8)?1’b1:1’b0 ;判断 i 的值是否大于 8,如果大

于 8 则 a 的值为 1,否则为 0。

3.6 位运算符

“~”按位取反,”|”按位或,”^”按位异或,”&”按位与,”^~”按位同或,除了”~”只需要一个操

作数外,其他几个都需要两个操作数,如 a&b,a|b。具体应用在后面的组合逻辑一节中有讲解。

3.8 拼接运算符

“{ }”拼接运算符,将多个信号按位拼接,如{a[3:0], b[1:0]},将 a 的低 4 位,b 的低 2 位拼接成

6 位数据。另外,{n{a[3:0]}}表示将 n 个 a[3:0]拼接,{n{1’b0}}表示 n 位的 0 拼接。如{8{1’b0}}表示

为 8’b0000_0000.

3.9 优先级别

此处记不住运算符的优先级别的话,最好的办法就是写逻辑代码时加()。

总结

简单介绍运算符,最重要的是理解赋值运算与非赋值运算符。

489

489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?