目录

前言

本系列主要介绍verilog HDL基础模块,只要夯实基础,以后FPGA的深入学习以及相应的项目算法开发才会更加顺利。此系列适合有一定数电基础或者初步了解Verilog HDL结构的同学。本系列会不定时更新(科研狗平时事情多)。

一、Verilog是什么?

Verilog HDL (Hardware Description Language) 是一种硬件描述语言,可以在算法级、门级到开关级的多种抽象设计层次上对数字系统建模。Verilog HDL进行设计最大的优点是其工艺无关性.这使得工程师在功能设计,逻辑验证阶段可以不必过多考虑门级及工艺实现的具体细节,只需根据系统设计的要求施加不同的约束条件,即可设计出实际电路。通俗来讲它是在开发FPGA、ASIC时使用的语言,跟开发软件使用C语言差不多,Verilog也从C语言中继承了多种操作符和结构,两者在结构上有比较多的相似之处,但是不同于C语言的地方是,Verilog是一种并行语言,而C语言则是一种面向过程语言。简单介绍这么多,要想学好这门语言,就必须掌握一定的基础。下面我们就展开介绍。

二、数据类型

1.常量

整数:整数可以用二进制 b 或 B,八进制 o 或 O,十进制 d 或 D,十六进制 h 或 H 表示,例

如, 4’b0011 表示 4 位位宽的二进制整数,4’ha 表示 4 位位宽的十六进制整数。

X 和 Z:X 代表不定值,Z代表高阻值,例如,5’b00x11,第三位不定值,3’b00z 表示最低位

为高阻值。

下划线:在位数过长时可以用来分割位数,提高程序可读性,如 8’b0000_1111 。

参数 parameter: parameter 可以用标识符定义常量,运用时只使用标识符即可,提高可读性

及维护性,如定义 parameter width = 8 ; 定义寄存器 reg [width-1:0] a; 即定义 8 位宽度寄存器。

参数的传递:在一个模块中如果有定义参数,在其他模块调用此模块时可以传递参数,并可

以修改参数,如下所示,在 module 后用#()表示。 parameter 可以用于模块间的参数传递,而 localparam 仅用于本模块内使用,不能用于参数传递。localparam 多用于状态机状态的定义(后面会介绍什么是状态机以及如何写好状态机)。

定义模块例如:

module top

#(

parameter depth = 15,

parameter width = 8

)

(

input [depth-1:0] addr,

input [width -1:0] data,

output result

);

endmodule2.变量

变量是指程序运行时可以改变其值的量,下面主要介绍几个常用了变量类型。

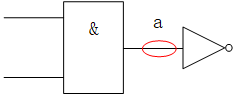

2.2.1 wire型

Wire 类型变量,也叫网络类型变量,用于结构实体之间的物理连接,如门与门之间,不能储

存值,用连续赋值语句 assign 赋值,定义为 wire [n-1:0] a ; 其中 n 代表位宽,如定义 wire a ; assign a = b ; 是将 b 的结点连接到连线 a 上。如下图所示,两个实体之间连线即是 wire 型变量。

2.2.2 reg型

reg 类型变量,也称为寄存器变量,可用来储存值,必须在 always 语句里使用。其定义为

reg [n-1:0] a ; 表示 n 位位宽的寄存器,如 reg [7:0] a; 表示定义 8 位位宽的寄存器 a。如下所示定

义了寄存器 q,生成的电路为时序逻辑。

module test(d, clk, q) ;

input d ;

input clk ;

output reg q ;

always @(posedge clk)

begin

q <= d ;

end

endmodule

也可以生成组合逻辑,如数据选择器,敏感信号没有时钟,定义了 reg Mux,最终生成电路

为组合逻辑。

module top(a, b, c, d, sel, Mux) ;

input a ;

input b ;

input c ;

input d ;

input [1:0] sel ;

output reg Mux ;

always @(sel or a or b or c or d)

begin

case(sel)

2'b00 : Mux = a ;

2'b01 : Mux = b ;

2'b10 : Mux = c ;

2'b11 : Mux = d ;

endcase

end

endmodule

2.2.3 Memory 型

可以用 memory 类型来定义 RAM,ROM 等存储器,其结构为 reg [n-1:0] 存储器名[m-1:0],意义

为 m 个 n 位宽度的寄存器。例如,reg [7:0] ram [255:0]表示定义了 256 个 8 位寄存器,256 也即

是存储器的深度,8 为数据宽度。

总结

简答介绍了Verilog数据类型。

1234

1234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?