FPGA纯verilog代码实现H.264/AVC视频解码,提供工程源码

ID:55520704789597517

FPGA小白

随着信息技术的快速发展,视频编码技术在多个领域中扮演着重要的角色。H.264 AVC作为一种广泛应用的视频编码标准,其高压缩比和优秀的图像质量使其成为了当今最受欢迎的视频编码标准之一。为了高效解码H.264 AVC编码的视频流,传统的软件实现面临着诸多挑战,例如计算量大、功耗高等问题。为了克服这些问题,本文基于FPGA技术,采用纯Verilog代码实现了H.264 AVC视频解码器,为视频解码提供了一种高性能、低功耗的解决方案。

首先,我们介绍了H.264 AVC视频编码标准的基本原理。H.264 AVC通过空间域和时间域的预测、变换和熵编码等技术,将视频数据进行有损压缩。而视频解码的过程则是对H.264 AVC编码的比特流进行解码,恢复出视频图像的过程。为了实现H.264 AVC视频解码器,我们参考了H.264 AVC标准文档,并分析了其中的关键算法和数据结构。

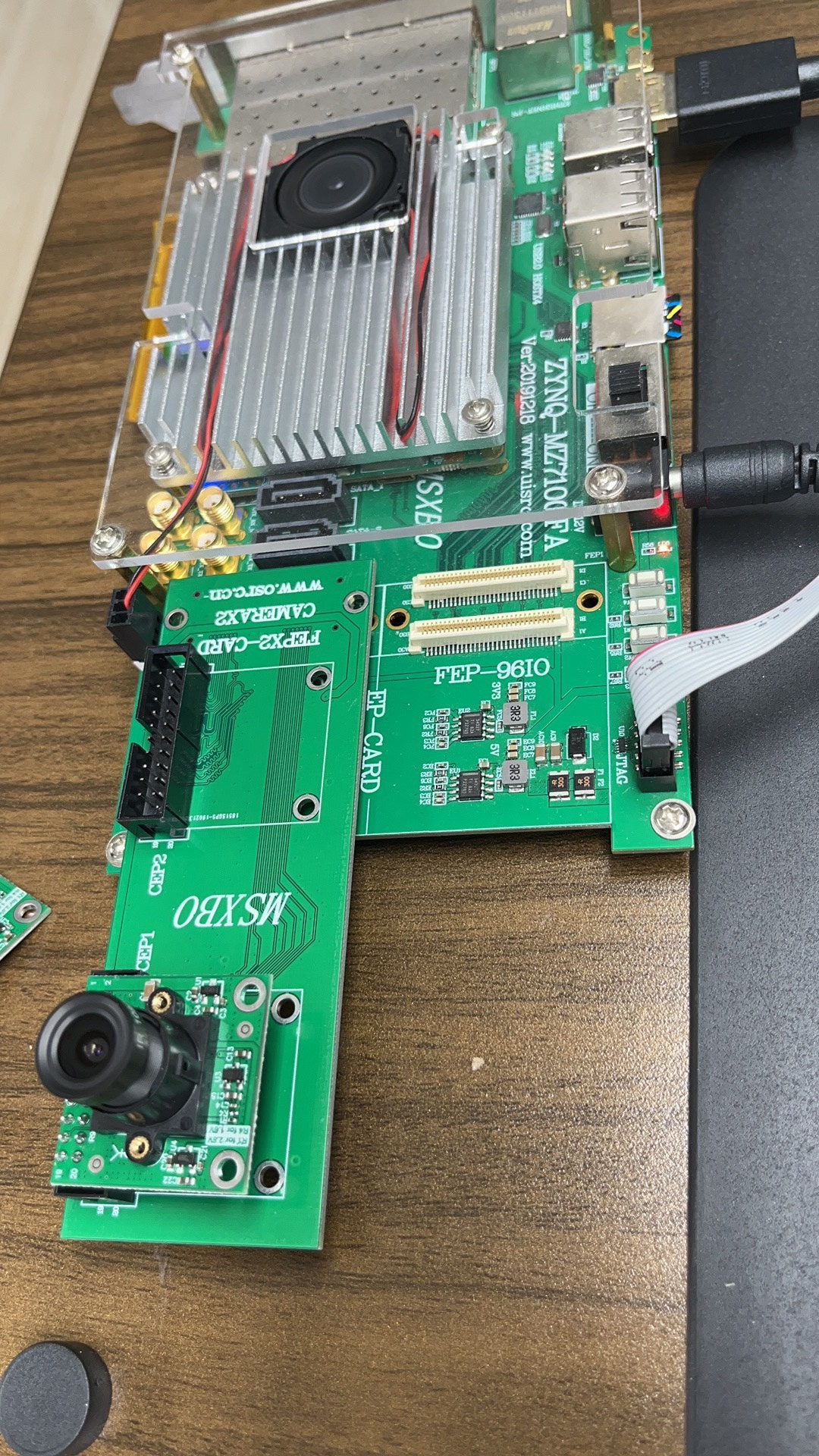

其次,我们介绍了FPGA技术在视频解码领域的优势。FPGA芯片具有可编程性和并行性强的特点,能够满足实时视频解码的需求。通过使用纯Verilog代码编写FPGA实现,我们可以充分发挥FPGA的优势,实现高效的视频解码。

然后,我们详细介绍了FPGA纯Verilog代码实现H.264 AVC视频解码的方法和步骤。首先,我们设计了视频解码器的基本模块,包括比特流解析模块、帧内预测模块、帧间预测模块、反量化模块、逆变换模块和帧重构模块等。然后,我们将这些基本模块组合在一起,构建了完整的H.264 AVC视频解码器。最后,我们使用Verilog语言编写代码,并进行仿真和综合,验证了我们设计的视频解码器的正确性和性能。

最后,我们提供了H.264 AVC视频解码器的工程源码。这些源码可以帮助开发者理解和学习H.264 AVC视频解码的原理和实现方法,并在实际应用中进行二次开发和优化。通过使用FPGA纯Verilog代码实现H.264 AVC视频解码,我们不仅提供了一种高性能、低功耗的视频解码方案,还为视频解码技术的研究和应用提供了一个有益的实践案例。

总之,本文围绕FPGA纯Verilog代码实现H.264 AVC视频解码展开阐述,介绍了H.264 AVC视频编码标准的原理,分析了FPGA技术在视频解码领域的优势,并详细介绍了FPGA纯Verilog代码实现H.264 AVC视频解码的方法和步骤。通过提供工程源码,我们希望为视频解码技术的研究和应用做出一定的贡献。我们相信,基于FPGA技术的视频解码方案将在未来的多媒体应用中发挥越来越重要的作用。

【相关代码,程序地址】:http://fansik.cn/704789597517.html

9073

9073

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?