摘要:PCIE——第7章——PCIe 总线的数据链路层与物理层

目录

7. 1. 2 事务层如何处理 DL_Down 和 DL_Up 状态

第 7 章 PCIe 总线的数据链路层与物理层

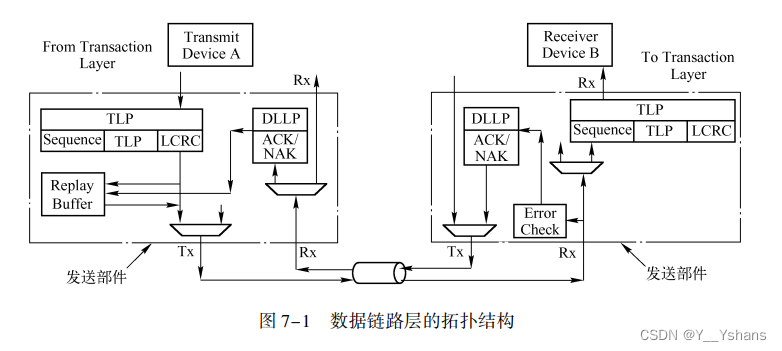

PCIe 总线的数据链路层处于事务层和物理层之间, 主要功能是保证来自事务层的 TLP 在 PCIe 链路中的正确传递, 为此数据链路层定义了一系列数据链路层报文, 即 DLLP。

与事务层不同, 数据链路层主要处理端到端的数据传送。

7. 1 数据链路层的组成结构

Replay Buffer 的大小决定了事务层可以暂存在数据链路层的报文数,在第 12. 4. 1 节中将进一步介绍 Replay Buffer 的大小与 PCIe 链路 延时间的关系。

如果 TLP 被正确接收, PCIe 设备将向对端设备发送 ACK DLLP ; 如果 TLP 没有被正确接收, PCIe 设备将向对端设备发 送 NAK DLLP。

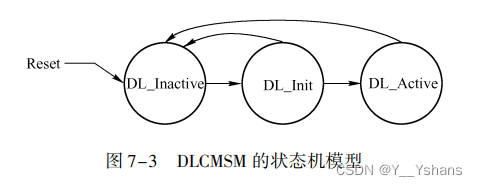

7. 1. 1 数据链路层的状态

DLCMSM 状态机除了可以使用上述状态位, 从物理层获得当前 PCIe 链路状态外, 还可 以使用以下状态位, 向事务层通知数据链路层所处的状态。 事务层通过这些状态位获知数据 链路层所处的工作状态。

● DL_Down。 数据链路层处于该状态时, 表示在 PCIe 链路的对端没有发现其他设备。当数据链路层处于 DL_Inactive 状态时, 该状态位有效。

● DL_Up。 数据链路层处于该状态表示在 PCIe 链路的对端连接了其他设备。 当数据链 路层处于 DL_Active 状态时, 该状态位有效。

7. 1. 2 事务层如何处理 DL_Down 和 DL_Up 状态

当事务层收到数据链路层的 DL_Down 状态信息时, 表示出现了以下情况。

● PCIe 链路的对端没有连接设备。

● PCIe 链路丢失了与对端设备的连接。

● 数据链路层和物理层出现某种错误, PCIe 链路不能正常工作。

● 系统软件禁用 PCIe 链路。

处于DL_Down的状态的时候,事务层不处理TLP,除非是被ACK/NCK报文确认过。当链路处于 DL_Down 状态时, RC 或者 Switch 的下游端口将复位与链路相关的内部逻 辑和状态。当链路为 DL_Down 状态时, Switch 和 PCIe 桥的上游端口, 将复位相关的内部逻辑和状 态, 并丢弃所有正在处理的 TLP。

事务层处于 DL_Up 状态时, 表示该设备与 PCIe 链路的对端设备已经建立连接, 链 路两端可以正常收发报文。 当事务层发现 PCIe 链路从 DL_Down 迁移到 DL_Up 状态时, 将向 PCIe 链路的对端设备重新发送 Set_Slot_Power_Limit 消息, 并重新初始化相关的寄 存器。

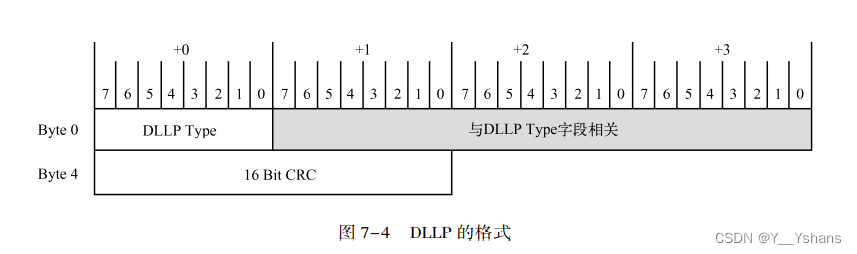

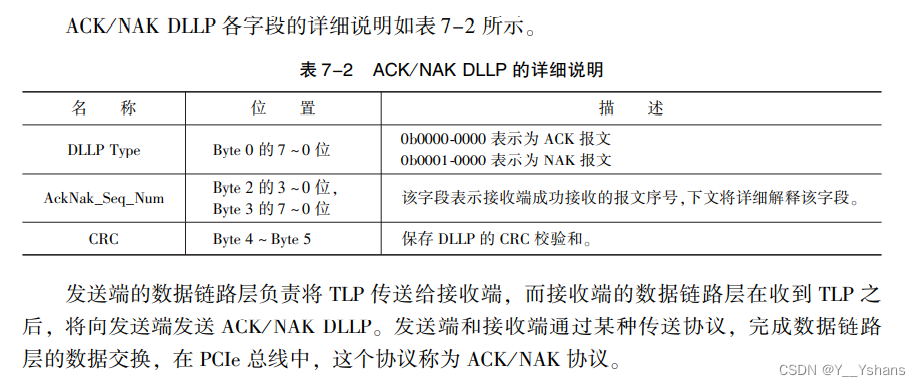

7. 1. 3 DLLP 的格式

DLLP 与 TLP 的概念并不相同, DLLP 产生于数据链路层, 终止于数据链路层, 这些报 文不会出现在事务层中, 而且对系统软件透明。 设置 DLLP 的目的是为了保证 TLP 的正确传 送和管理 PCIe 链路。

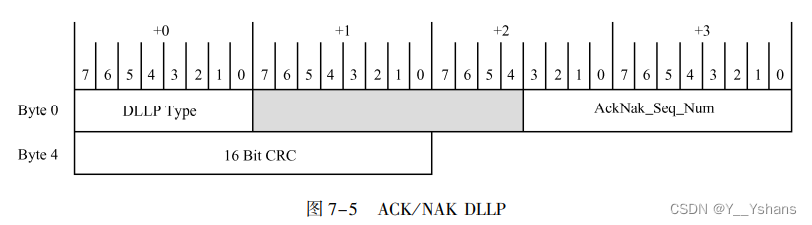

● ACK DLLP:该 DLLP 表示接收端正确收到来自对端的 TLP

● NAK DLLP: 该 DLLP 由接收端发向发送端。 该 DLLP 表示接收端有哪些 TLP 没有被正确接收

● Power Management DLLPs: PCIe 设备使用该组 DLLP 进行电源管理, 并向对端设备通 知当前 PCIe 链路的状态。

● Flow Control Packet DLLPs: 该组 DLLP 包括 InitFC1、 InitFC2、 UpdateFC DLLP, PCIe 总线使用这些 DLLPs 进行流量控制。

● Vendor⁃specific DLLP:一些定制的 DLLP, PCIe 总线规范并未对此约束。

7. 2 ACK / NAK 协议

ACK / NAK 协议是一种滑动窗口协议。发送端在发送 TLP 时, 首先将这个 TLP 放入发送窗口中 (这个窗口即 Replay Buffer) , 并对这些 TLP 从 0 ~ n 进行编号。当发送端收到接收端对第 n 个报文的确认后, 表示第 n、 n - 1、 n - 2 等在窗口中的报文都已经被正确收到, 然后统一 滑动这个窗口。 PCIe 总线使用这种方法可以提高窗口的利用率。

与此对应, 接收端也维护了一个窗口, 该窗口记录数据报文的发送序列号范围。

7. 2. 1 发送端如何使用 ACK / NAK 协议

发送端使用计数器 NEXT_TRANSMIT_SEQ 的当前值设置 TLP 的 Sequence 号, 该计数器 的初始值为 0。 PCIe 设备每发送完毕一个 TLP, 这个计数器将加 1, 直到该计数器的值为 4095(NEXT_TRANSMIT_SEQ 的最大值)。

与此对应, 接收端也设置了一个 12 位的计数器 NEXT_RCV_SEQ。 这个计数器记录接收 端即将接收的 TLP 的 Sequence 号。

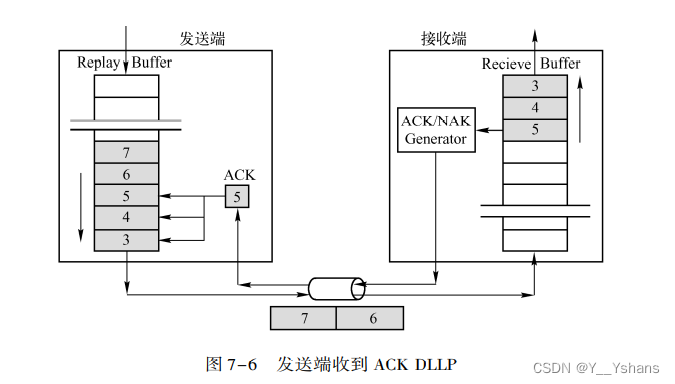

(1) 发送端向接收端发送 TLP3 ~ 7, 其中 TLP3 是第一个报文, TLP7 是最后一个报文。 此时发送端的 NEXT_TRANSMIT_SEQ 计数器为 8, 表示即将填入到 Replay Buffer 中的报文序 列号为 8。

(2) 接收端按序收到 TLP3 ~ 5, 而 TLP6 和 7 仍在传送过程中。 接收端的 NEXT_RCV_ SEQ 计数器为 6, 表示即将接收的报文序列号为 6。

(3) 接收端通过报文检查决定接收 TLP3 ~ 5, 然后发送 ACK DLLP, 此时这个 ACK DLLP 的 AckNak_Seq_Num 字段为 5。 为了提高总线的利用率, 接收端不会为每一个接收到 的 TLP 都做出应答。 在这个例子中, AckNak _Seq _Num 字段为 5 表示 TLP3 ~ 5 都已经被 接收。

(4) 发送端收到 AckNak_Seq_Num 字段为 5 的 ACK DLLP 后, 得知 TLP3 ~ 5 都被成功接 收。 此时发送端将 TLP3 ~ 5 从 Replay Buffer 中清除。

(5) 接收端陆续收到 TLP6 ~ 7 后, 接收端的 NEXT_ RCV_ SEQ 计数器为 8, 表示即将 接收的报文序列号为 8。 然后接收端向发送端发送 ACK DLLP, 这个 DLLP 的 AckNak_Seq_ Num 字段为 7, 即为 NEXT_RCV_SEQ - 1。

(6) 发送端收到 AckNak_Seq_Num 字段为 7 的 ACK DLLP 后, 得知 TLP6 ~ 7 都被成功接 收。 此时发送端将 TLP6 ~ 7 从 Replay Buffer 中清除。

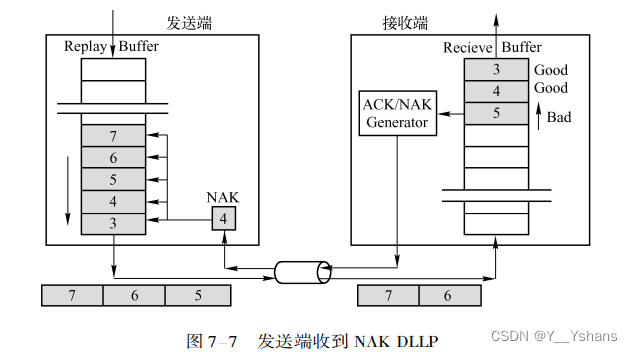

(1) 发送端向接收端发送 TLP3 ~ 7, 其中 TLP3 是第一个报文, 而 TLP7 是最后一个 报文。 (2) 接收端按序收到 TLP3 ~ 5, 而 TLP6 和 7 仍在传送过程中。

(3) 接收端通过报文检查决定接收 TLP3 ~ 4, 此时 NEXT_RCV_SEQ 为 5, 表示即将接 收 TLP5。

(4) TLP5 没有通过完整性验证, 此时接收端将向对端发送 NAK DLLP, 这个 DLLP 的 AckNak_Seq_Num 字段为 4, 即为 NEXT_RCV_SEQ - 1。 AckNak_Seq_Num 字段为 4 表示接收 端最后一个接收正确的 TLP, 其 Sequence 号为 4。

(5) 发送端收到 AckNak_Seq_Num 字段为 4 的 NAK DLLP 后, 得知 TLP3 ~ 4 已被成功接 收。 此时发送端首先停止从事务层接收新的 TLP, 之后将 TLP3 ~ 4 从 Replay Buffer 中清除。 (6) 发送端重新发送在 Replay Buffer 中从 TLP5 开始的报文。 在这个例子中, 发送端将 重新发送 TLP5 ~ 7。

当出现NAK的时候,表示链路肯定出了问题,所以不能无限次的发送同一个东西。为此在发送端中设置了一个 2 位计数器 REPLAY_NUM, 这个计数器的初始值为 0, 当数据链路层处于 Inactive 状态时, 该计数器保持为 0。 REPLAY_NUM 计数器按照以下几个原则进行更新。P202

7. 2. 2 接收端如何使用 ACK / NAK 协议

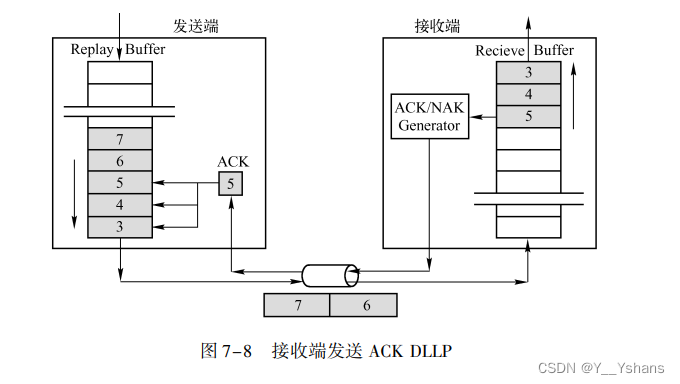

(1) 发送端发送 TLP3 ~ 7 给接收端, 其中 TLP3 是第一个报文, 而 TLP7 是最后一个 报文。 (2) 接收端按序收到 TLP3 ~ 5, 而 TLP6 和 7 仍在传送过程中。 此时 NEXT_RCV_SEQ 的 值被更新为 6, 表示下一个即将接收的 TLP, 其 Sequence 号为 6。

(3) 接收端通过报文检查决定接收 TLP3 ~ 5, 然后发送 ACK DLLP, 这个 DLLP 的 Ack⁃Nak_Seq_Num 字段为 5。 为了提高总线的利用率, 接收端不会对每一个接收到的 TLP 都做出 应答。 在这个例子中, AckNak_Seq_Num 字段为 5 表示 TLP3 ~ 5 都已经被接收。

(4) 接收端将接收到的 TLP3 ~ 5 传递给事务层。

(5) 接收端陆续收到 TLP6 ~ 7 后, 继续执行步骤 3 ~ 4。

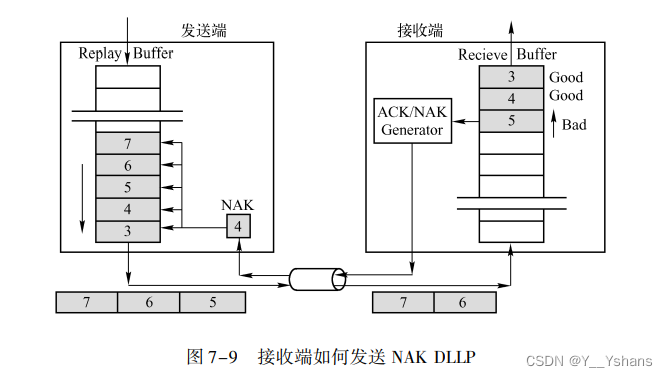

下面将使用一个实例进一步说明接收端如何发送 NAK DLLP, 该实例如图 7-9 所示, 其 描述如下所示。

(1) 发送端向接收端发送 TLP3 ~ 7, 其中 TLP3 是第一个报文, 而 TLP7 是最后一个 报文。 (2) 接收端按序收到 TLP3 ~ 5, 并将这些报文放入 Receive Buffer, 当然也可以在这些报 文通过完整性检查后, 再决定是否将这些 TLP 放入 Receive Buffer 中, 而 TLP6 和 7 仍在传送 过程中。

(3) 接收端通过报文检查决定接收 TLP3 ~ 4, 此时 NEXT_RCV_SEQ 为 5,表示即将接收TLP5。 此时接收端将 TLP3 ~ 4 传递给事务层。

(4) 而 TLP5 没有通过完整性验证, 此时接收端将发送 NAK DLLP, 这个 DLLP 的 Ack⁃ Nak_Seq_Num 字段为 4, 即 NEXT_RCV_SEQ - 1。 AckNak_Seq_Num 字段为 4 表示接收端最后 一个正确接收的 TLP, 其 Sequence 号为 4。 此时接收端将设置 NAK_SCHEDULED 位为 1, 而 NEXT_RCV_SEQ 保持不变, 即为 5。

(5) 接收端将丢弃 TLP5。 当 TLP6 ~ 7 到达时, 接收端仍然丢弃这些报文, 即便这些报 文通过了完整性检查, 因为这些报文的 Sequence 号大于 NEXT_RCV_SEQ。 接收端不会为 TLP6 ~ 7 发送 NAK DLLP, 因为此时 NAK_SCHEDULED 位有效。

(6) 发送端收到 NAK DLLP, 其序号为 4, 此时发送端首先将 TLP3 ~ 4 从 Replay Buffer 中清除,因为 TLP3 ~ 4 已经被接收端正确接收, 然后重新发送 TLP5 ~ 7。

(7) 接收端如果正确接收到 TLP5 时, 发现其 Sequence 号与 NEXT_RCV_SEQ 相等, 将 清除 NAK_SCHEDULED 位。

(8) 接收端陆续接收到 TLP6 ~ 7, 并根据 CRC 的检查结果决定发送 ACK DLLP 或者 NAK DLLP。

在某些情况下, 接收端发送的 NAK DLLP 可能并没有被发送端正确接收, 因此接收端在 很长一段时间内都不会得到 “发送端重试的” TLP。 此时接收端将会择时重发 NAK DLLP, 为此接收端设置了一个 AckNak_LATENCY_TIMER 计数器, 当该计数器溢出时, 接收端将重 发 NAK DLLP。

7. 2. 3 数据链路层发送报文的顺序

数据链路层还规定了报文发送的顺序。

(1) 正在发送的 TLP 或者 DLLP 具有最高的优先权。 PCIe 总线为了保证数据的完整性, 不允许打断正在传送的报文。 从理论上讲, 打断正在传送的报文是可行的, 但是硬件需要更 大的代价, 也需要制定更加复杂的协议保证数据的完整性。

(2) PLP (Physical Layer Packet)的传送。 一般来说, 处于协议底层的报文优先权高于处于协议高层的报文, 这 也是解决死锁的一个有效方法。

(3) NAK DLLP。 NAK DLLP 需要优先于 TLP 的发送, 原理同上。

(4) ACK DLLP。 ACK DLLP 响应正确接收的报文, 在绝大多数处理过程中, 错误处理 报文优先于正确的响应, 这也是一种防止死锁的方法。

(5) 重新传送 Replay Buffer 中的 TLP。 也是一种发现错误后的恢复手段, 因此这种报文 的传递优先权高于其他 TLP。 因为在错误没有处理完毕之前, 其他 TLP 的传递是没有意义 的, 接收端都将丢弃这些报文。

(6) 其他在事务层等待的 TLP。

(7) 其他 DLLP, 这些 DLLP 包括地址路由, 电源管理等报文, 这些报文与数据报文的 传递无关, 是 PCIe 总线规定的一些控制报文, 所以优先权最低。

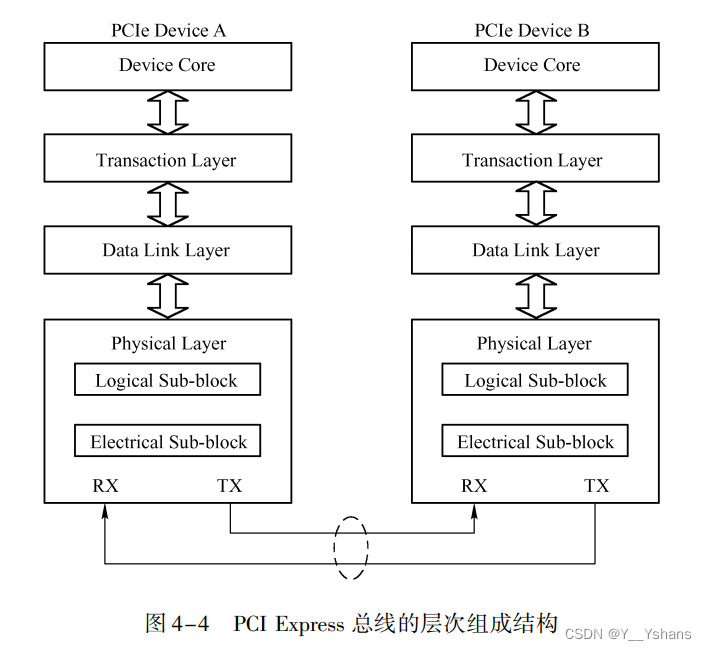

7. 3 物理层简介

物理层在数据链路层和 PCIe 链路之间, 其主要作用有两个, 一是发送 数据链路层的 TLP 和 DLLP; 二是发送和接收在物理层产生的报文 PLP (Physical Layer Pack⁃ et) ; 三是从 PCIe 链路接收数据报文并传送到数据链路层。

物理层主要由物理层逻辑模块和物理层电气模块组成

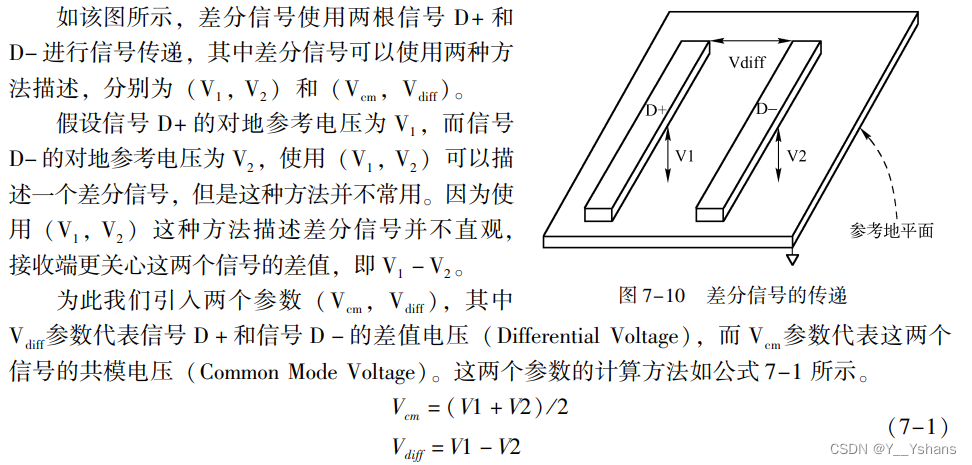

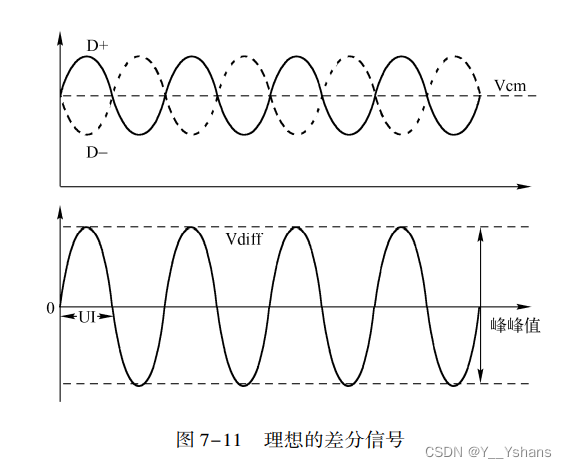

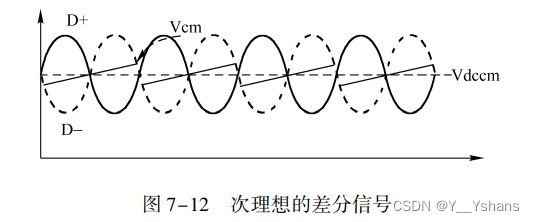

7. 3. 1 PCIe 链路的差分信号

差分信号是由驱动端发送 两个等值、 相位相反的信号, 接收端通过这两个信号的电压差值来判断差分信号是逻辑状态 “0” 还是 “1” 。 与单端信号相比, 差分信号具有许多优势。

7. 3. 2 物理层的组成结构

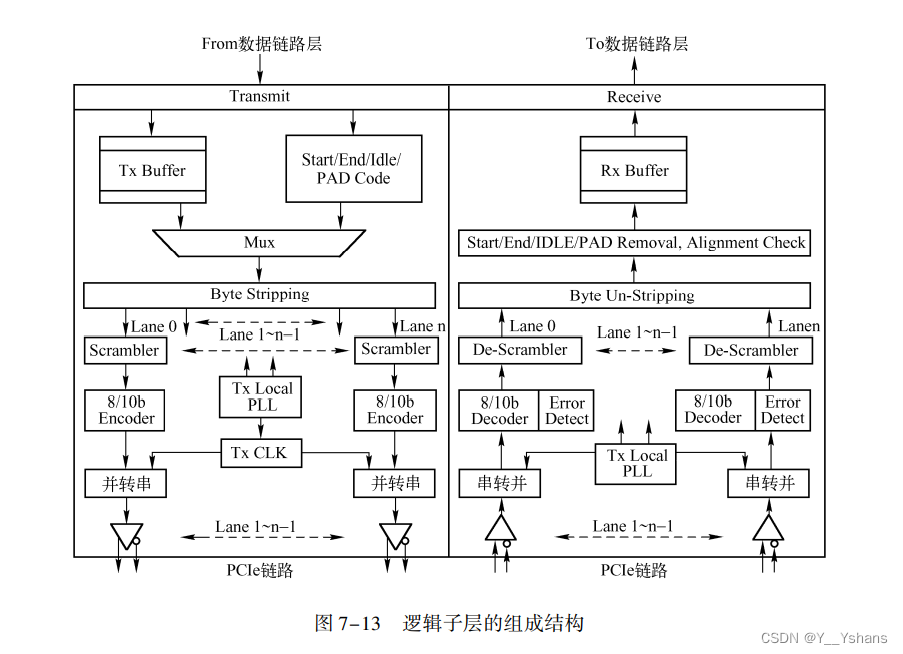

逻辑子层与数据链路层进行数据交换, 由发送逻辑 TX 和接收逻辑 RX 组成, 其结构如图 7-13 所示。

7. 3. 3 8 / 10b 编码与解码

该编码将 8 位编码转化为 10 位, 以平衡数据流中 0 与 1 的数量。 使用这种方法可以保 证数据流中 1 和 0 的数量相等, 即保证直流平衡 (DC Balance) 。

7. 4 小结

本章重点介绍了数据链路层的状态, 以及 ACK / NAK 协议, 并简要介绍了 PCIe 总线的 物理层。 其中 PCIe 总线的物理层非常重要, 深入理解物理层是深入理解 PCIe 体系结构的要 点。 在第 8 章讲述的内容以此为基础。

参考文章:

PCI_Express_体系结构导读——王齐

144

144

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?