提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

提示:这里可以添加本文要记录的大概内容:

VHDL和Verilog HDL是目前主流的两种硬件描述语言(Hard Description Language)。本文是硬件描述语言系列的第一篇 —— 组合电路的VHDL。参考了《EDA技术实用教程(第5版)》,使用的环境是quartus II13.1。

提示:以下是本篇文章正文内容,下面案例可供参考

一、entity和architecture——以MUX为例

首先来看一个组合电路的例子——多路选择器,通过它的VHDL代码我们能了解到最简单的代码结构。

1. Mux完整VHDL代码

代码如下(示例):

ENTITY mux21a IS

PORT(a, b, s :IN BIT;

y:OUT BIT );

END ENTITY mux21a;

architecture bhv OF mux21a is

BEGIN

PROCESS (a,b,s) BEGIN

IF (s = '1') THEN y<=a; ELSE y<=b; END IF;

END PROCESS;

end architecture bhv ;

可以看出Mux的代码包括了实体(entity)和结构体(architechture)两部分,进程(process)包含在architechture之中。

2.解析

①实体(entity)部分

ENTITY mux21a IS

PORT(a, b, s :IN BIT;

y:OUT BIT );

END ENTITY mux21a;

mux21a是顶层实体(top-level entity)的名字,最好跟工程文件同名(在quartus中是必须)。

端口语句中定义a,b,s为信号输入端口,y为信号输出端口。数据类型为bit,只有0和1,且在表达0和1时必须加单引号,否则会当成是INTEGER 类型。注意,端口声明的最后一行末尾不要加分号!

② architecture

architecture bhv OF mux21a is

BEGIN

PROCESS (a,b,s) BEGIN

IF (s = '1') THEN y<=a; ELSE y<=b; END IF;

END PROCESS;

end architecture bhv ;

bhv是结构体的名字,可以自定义的。由process引导的语句成为进程语句,PROCESS 旁边的(a,b,s)叫sensitivity list,里面放了所有的输入信号。如果敏感信号发生变化,process里的语句就会被执行。

③ process

process为以下结构。

process_label : process(sensitivity_list) --process_label 是自定义的,可以没有。

-- declarative part

begin

-- sequential statement

end process process_label;

注意,VHDL和软件编程语言不同,“end process; ”之后这个process还会被执行——只要敏感信号表(sensitivity list)中的信号改变。如果我不写sensitivity list会怎么样呢?答案是这个process会连续运行。在这种情况下,进程必须包含一个等待语句来暂停进程并在事件发生或条件变为真时激活它。 当敏感信号表存在时,进程不能包含等待语句。

process中的语句按顺序执行,而同一个architechture下的不同process是并行的。

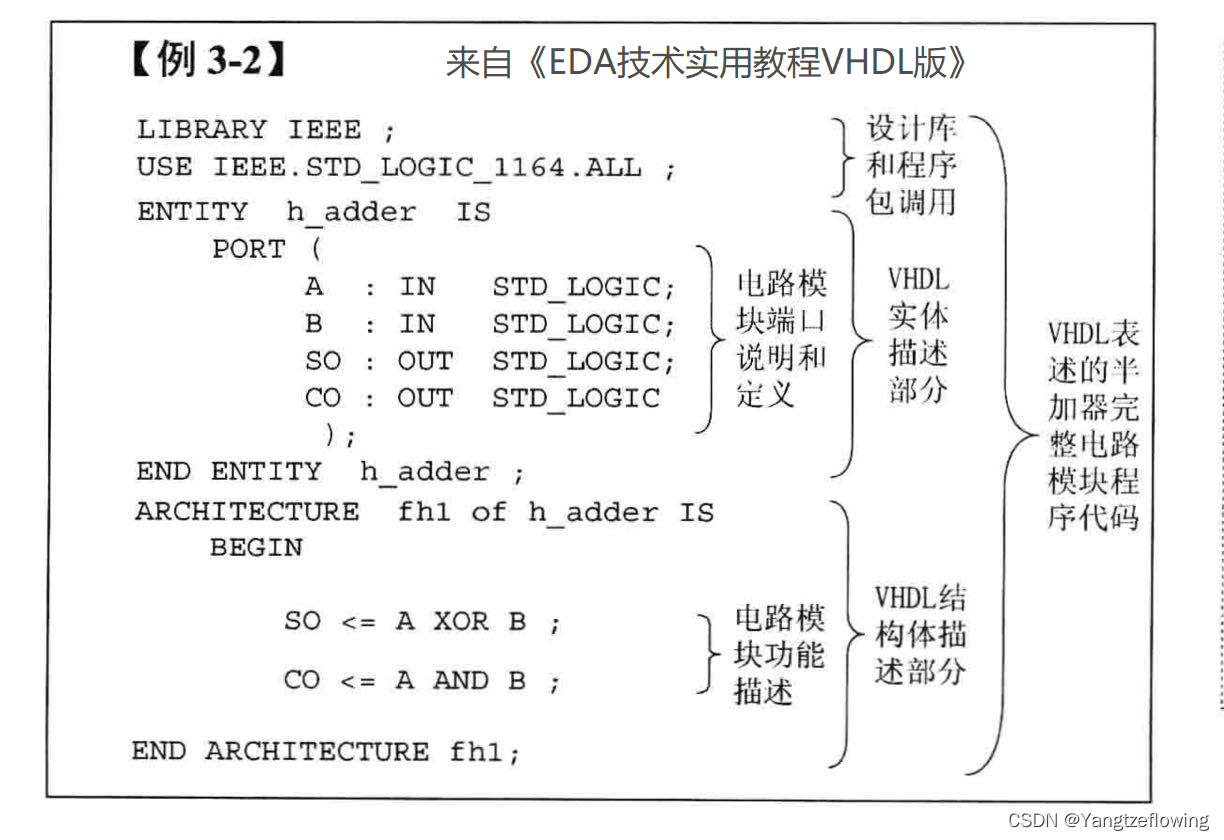

二、以半加器为例(half-adder)

1.完整代码

2. 半加器

半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。 是实现两个一位二进制数的加法运算电路。这里SO是结果位,CO是进位。

3. 代码解析

实体部分:A : IN STD_LOGIC 把引脚A作为输入,数据类型是STD_LOGIC,这种数据类型比bit更丰富,也包括0和1。还有别的数据类型,如 STD_LOGIC_VECTOR(n downto 0)。

设计库和程序包调用:

LIBRARY <设计库名>;

USE <设计库名>.<程序包名>.all

上例使用的数据类型std_logic 存放于程序包STD_LOGIC_1164中,这个程序包在库 IEEE里。

总结

本文从多路选择器开始,介绍了贼简单版的VHDL结构。然后通过半加器的例子,加入了调用设计库和程序包的说明。参考资料有《EDA技术使用教程(VHDL)版》,以及USF的教案https://cse.usf.edu/~haozheng/teach/cda4253/doc/vhdl-stmt.pdf

4957

4957

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?