VHDL语言设计的基本单元就是VHDL语言的一个基本设计实体(Entity)。

一个实体,简单的可以是一个与门,复杂点的可以是一个微处理器或一个系统。但是,不管是简单的数字电路,还是复杂的数字电路,其基本构成是一致的,都由实体说明(Entity Declaration)和构造体(Architecture Body)两部分构成。

实体说明部分规定了设计单元的输入输出接口信号或引脚,而构造体部分定义了设计单元的具体构造和行为。

例1示出了二选一电路的VHDL描述。由例1可以看出,实体说明是二选一器件外部引脚的定义;而构造体则描述了二选一器件的逻辑电路和逻辑关系。

【例1】 二选一电路的VHDL描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

-- ENTITY DECLARATION

ENTITY mux IS

PORT (d0,d1,sel:IN STD_LOGIC;

q:OUT STD_LOGIC);

END mux;

-- ARCHITECTURE BODY

ARCHITECTURE connect OF mux IS

SIGNAL tmp:STD_LOGIC;

BEGIN

PROCESS(d0,d1,sel)

BEGIN

tmp <= (d0 AND sel) OR (d1 AND (NOT sel));

q <= tmp;

END PROCESS;

END connect;

下面以本段程序为例,说明一下实体和构造体的书写规定。

一、实体

任何一个基本设计单元的实体说明都具有如下的结构:

ENTITY 实体名 IS

【类属参数说明】;

【端口说明】;

END 实体名;

一个基本设计单元的实体说明以“ENTITY 实体名 IS”开始至“END 实体名”结束。

例如在上面例子中从“ENTITY mux IS”开始至“END mux”结束。

这里大写字母表示实体说明的框架,即每个实体说明都应这样书写,是不可缺少和省略的部分。

小写字母是设计部分,随设计单元不同而不同。

实际上,VHDL不区分大小写,这里仅仅是为了阅读方便而加以区分的。

1.类属参数说明

类属参数说明必须放在端口说明之前,用于指定参数,例1中没体现类属说明语句,具体书写范例如下:

GENERIC ( m: TIME: = 1 ns)

该语句指定了m的值为1。

2.端口说明

端口说明是对基本设计实体与外部接口的描述,也可以说是对外部引脚信号的名称、数据类型和输入、输出方向的描述。其书写格式如下:

PORT(端口名{,端口名}:方向 数据类型名;

┇

端口名{,端口名}:方向 数据类型名);

(1)端口名

端口名是赋予每个外部引脚的名称,通常用一个或几个英文字母,或者用英文字母加数字命名之。例如例1中的外部引脚为d0,d1,sel,q。

(2)端口方向

端口方向用来定义外部引脚的信号方向是输入还是输出。例如,例1中的d0,d1,sel为输入引脚,故用方向说明符“IN”说明之,而q则为输出引脚,用方向说明符“OUT”说明之。

凡是用“IN”进行方向说明的端口,其信号自端口输入到构造体,而构造体内部的信号不能从该端口输出。

相反,凡是用“OUT”进行方向说明的端口,其信号将从构造体内经端口输出,而不能通过该端口向构造体内输入信号。

另外,“INOUT”用以说明该端口是双向的,可以输入也可以输出

“BUFFER”用以说明该端口可以输出信号,且在构造体内部也可以利用该输出信号。

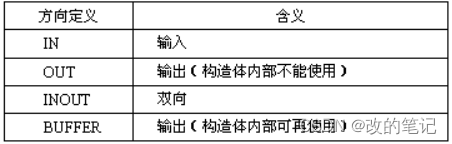

表示方向的说明符及其含义如表2.1所示。

表2.1 端口方向说明

注:OUT允许对应多个信号,BUFFER只允许对应一个

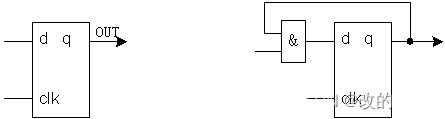

表2.1中“OUT”和“BUFFER”都可以定义为输出端口,但是它们之间是有差别的,如图1所示。

(a) (b) 图2 .1 OUT和BUFFER的区别

在图2.1(a)中,锁存器的输出端口被说明为“OUT”,而在(b)中,锁存器的输出被说明为“BUFFER”。从图中可以看到,如果构造体内部要使用该信号,那么锁存器的输出端必须说明为“BUFFER”,而不能用“OUT”说明。

图2.1(b)说明了,当一个构造体用“BUFFER”说明输出端口时,与其连接的另一个构造体的端口也要用“BUFFER”说明。对于“OUT”则没有这样的要求。

如下两例说明了端口方向的使用方法。

【例2】并行口通信芯片8255,其端口定义为:

ENTITY i8255 IS

PORT(

reset,cs:IN STD_LOGIC;

rd,wr:IN STD_LOGIC;

a1,a0:IN STD_LOGIC;

pa,pb:INOUT STD_LOGIC_VECTOR(7 DOWNTO 0);

pcl,pch:INOUT STD_LOGIC_VECTOR(3 DOWNTO 0);

d:INOUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END i8255;

根据电路定义,所有的控制信号和地址信号都是输入模式IN,而其3个端口以及与总线相连的数据端口都是双向的,因此定义为双向模式INOUT。

【例3】定时/计数器芯片8253,其端口定义为:

ENTITY i8253 IS

PORT(

rd,wr,cs,a1,a0:IN STD_LOGIC;

clk0,clk1,clk2:IN STD_LOGIC;

gate0,gate1,gate2:IN STD_LOGIC;

out0,out1,out2:BUFFER STD_LOGIC;

d:INOUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END i8253;

与8255一样,8253的控制与地址信号是输入模式,而连接总线的数据端口是双向模式。由于计数器的输出out要被用来决定下一个状态,而这个输出又不能连接别的输出或双向瑞口,因此将其定义成缓冲端口。

(3)数据类型

在VHDL语言中有10种数据类型,但是在逻辑电路设计中只用到两种:STD_LOGIC和STD_LOGIC_VECTOR。

当端口被说明为STD_LOGIC数据类型时,该端口的信号取值只可能是“1”或“0”。这里的“1”和“0”是指逻辑值,也就是说STD_LOGIC数据类型是位逻辑数据类型,其取值只能是两个逻辑值(“1”和“0”)中的一个。

当端口被说明为STD_LOGIC_VECTOR数据类型时,该端口的取值可能是一组二进制位的值。例如,某一数据总线输出端口,具有8位的总线宽度。那么这样的总线端口的数据类型可以被说明成STD_LOGIC_VECTOR。总线端口上的值由8位二进制位的值所确定。较完整的端口说明下例所示。

【例4】

PORT(d0,d1,sel:IN STD_LOGIC;

q:OUT STD_LOGIC;

bus:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

该例中d0,d1,sel,q都是STD_LOGIC数据类型,而bus是STD_LOGIC_VECTOR类型,

(7 DOWNTO 0)表示该bus端口是一个8位端口,由B7-B0 8位构成。位矢量长度为8位。

二、 构造体

构造体是一个基本设计单元,它具体地指明了该基本设计单元的行为、元件及内部的连接关系,也就是说它定义了设计单元具体的功能。

构造体对其基本设计单元的逻辑关系可以用3种方式进行描述,即行为描述(基本设计单元的数学模型描述)、寄存器传输描述(数据流描述)和结构描述(逻辑元件连接描述)。不同的描述方式,只体现在描述语句上,而构造体的结构是完全一样的。由于构造体是对实体功能的具体描述,因此它一定要跟在实体的后面。通常,先编译实体之后才能对构造体进行编译。如果实体需要重新编译,那么相应构造体也应重新进行编译。

一个构造体的具体结构描述如下:

ARCHITECTURE 构造体名 OF 实体名 IS

[定义语句] 内部信号,常数,数据类型,函数等的定义;

BEGIN

[并行处理语句];

END 构造体名;

一个构造体从“ARCHITECTURE 构造体名 OF 实体名 IS”开始,至“END 构造体名”结束。下面对构造体的有关内容和书写方法作一说明。

1.构造体名称的命名

构造体的名称是对本构造体的命名,它是该构造体的唯一名称。OF后面紧跟的实体名表明了该构造体所对应的是哪一个实体,用IS来结束构造体的命名。

2.定义语句

定义语句位于ARCHITECTURE和BEGIN之间,用于对构造体内部所使用的信号、常数、数据类型和函数进行定义。例如:

ARCHITECTURE behav OF mux IS

SIGNAL nesl:STD_LOGIC;

┇

BEGIN

┇

END behav;

信号定义和端口说明的语句一样,应有信号名和数据类型的说明。因它是内部连接用的信号,故没有也不需有方向的说明。

3.并行处理语句

并行处理语句处于语句BEGIN和END之间,这些语句具体地描述了构造体的行为及其连接关系。在构造体中的语句都是可以并行执行的,也就是说,语句的执行不以书写的语句顺序为执行顺序。

VHDL语言设计包括实体说明和构造体两部分。实体定义了设计单元的输入输出接口,如二选一电路示例中的d0,d1,sel和q。构造体描述了设计单元的逻辑电路和行为,如过程和信号定义。端口方向包括IN,OUT,INOUT和BUFFER,分别定义信号的方向和使用。数据类型主要为STD_LOGIC和STD_LOGIC_VECTOR,用于位逻辑和位向量操作。

VHDL语言设计包括实体说明和构造体两部分。实体定义了设计单元的输入输出接口,如二选一电路示例中的d0,d1,sel和q。构造体描述了设计单元的逻辑电路和行为,如过程和信号定义。端口方向包括IN,OUT,INOUT和BUFFER,分别定义信号的方向和使用。数据类型主要为STD_LOGIC和STD_LOGIC_VECTOR,用于位逻辑和位向量操作。

1007

1007

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?